Fターム[5F110HM15]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | ゲートに対する配置 (3,125) | オフセット (2,875) | LDD (2,472)

Fターム[5F110HM15]に分類される特許

2,001 - 2,020 / 2,472

薄膜トランジスタ

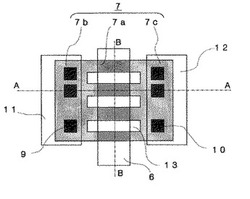

【課題】 有機電界発光型表示装置において、各画素の輝度を均一にする手段として、薄膜トランジスタの特性のばらつきを補償するための薄膜トランジスタを複数配置して電流を制御する技術が挙げられる。しかし、有機電界発光型表示装置においては微弱な電流の制御が必要であり、上記補償による電流の均一化だけでは不十分であった。

【解決手段】 本発明に係わる有機電界発光型表示装置における薄膜トランジスタは、ソース領域7bとドレイン領域7cとを共通にした複数のチャネル領域7aを備えて、かつそのパターン端がテーパー形状に加工されたポリシリコン膜7を備えたことを特徴としており、さらに各チャネル領域7aのチャネル幅Wが5μm以上30μm以下であることを特徴とするものである。

(もっと読む)

置換ゲート電界効果トランジスタ、及びその製造方法

【課題】

基板上に作製されるゲルマニウムまたはSiGeチャネルを有する、p−チャネルMISFETおよびn−チャネルMISFETの両方を提供する。

【解決手段】

傾斜SiGeチャネルまたはGeチャネルを有する、シリコン基板(502)上の自己整列MISFETトランジスタ(500H)。チャネル(526)は、ガスクラスタイオンビーム(524)照射を用いて形成され、従来のシリコンチャネルMISFETより高いチャネル移動度を提供する。上記トランジスタの製造方法は、ガスクラスタイオンビーム処理ステップで強化され、SiGeまたはGeチャネルを形成する置換ゲート工程に基づく。該チャネルは、補足ステップであるガスクラスタイオンビーム処理によって、あるいは、増移動度チャネルと同時にドープすることもできる。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

半導体回路並びに表示装置及び該表示装置を具備する電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することなくシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

短チャンネル半導体素子製造

蓄積モードのマルチゲート・トランジスタ素子(1100)の構成が開示される。本素子は、短チャンネル効果、特にhiが軽減され、チャンネル領域、拡張領域、及び/又は、ソース(1104)/ドレイン(1106)領域に更に1つのタイプのドーパント材料が埋め込まれて、不所望の漏れ電流をもたらすチャンネル領域内の、導電パスの設定、及び、電子の蓄積を緩和するように構成される。 (もっと読む)

複数の熱処理によって自己整列されたシリサイド膜を形成する方法

【課題】複数の熱処理によって自己整列されたシリサイド膜を形成する方法を提供する。

【解決手段】基板上に金属膜を形成し、第1の温度で第1の熱処理を遂行して、金属膜上に金属シリサイド膜を形成し、第1の熱処理とインサイチュウとして第1の温度より低い第2の温度で第2の熱処理を遂行することを含む。これにより、欠陥がない金属シリサイド膜を形成でき、金属シリサイド膜を採用する半導体素子の電気的特性を安定的に改善させることができる。

(もっと読む)

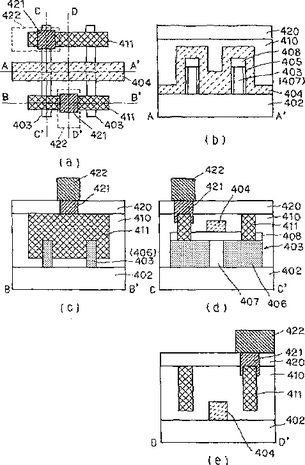

薄膜トランジスタの製造方法および液晶表示装置の製造方法

【課題】ゲート電極およびレジストを精度良くエッチングできる薄膜トランジスタの製造方法を提供する。

【解決手段】レジスト後退法で金属層41を後退させる前に、レジスト42および金属層41をマスクとして活性層6のソース領域12およびドレイン領域13となる部分に不純物をドーピングする。レジスト42および金属層41をRIEにてエッチングして金属層41をゲート電極17とする際に、レジスト42中の不純物から放出されるプラズマ発光強度の変化を測定する。プラズマ発光強度が略一定となった時点を、レジスト42および金属層41のRIEによるエッチングの終点とする。金属層41およびレジスト42を精度良くエッチングできる。

(もっと読む)

半導体装置およびその作製方法

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】ガラス基板上に第1の絶縁膜、島状の結晶性珪素膜、ゲイト絶縁層、ゲイト電極、第1の配線、ゲイト電極及び第2の絶縁膜を形成し、第2の絶縁膜及びゲイト絶縁層をエッチングしてゲイト電極及び第1の配線の側面に側壁を形成するとともに、島状の結晶性珪素膜のソース領域及びドレイン領域を露出し、ゲイト電極、第1の配線、側壁、島状の結晶性珪素膜及び第1の絶縁膜上に金属層を形成し、ソース領域及びドレイン領域と、金属層とを反応させて島状の結晶性珪素膜の側面から上面にわたって密着したシリサイド層を形成し、金属層をエッチングして、ソース領域又はドレイン領域の一方のシリサイド層と第1の配線とを接合する第2の配線を形成する。

(もっと読む)

CMOS集積回路の製造に用いるゲルマニウム・エピタキシャル膜を絶縁体上で成長させる方法

【課題】 SOIおよびGOIの両部分に対して用いられるCMOSの製造方法を好適に提供すること。

【解決手段】 本発明によるシリコンベースのCMOSを製造する方法は、シリコン基板ウェハを用意する工程(12)、シリコン基板ウェハ上に絶縁層を堆積させる工程(14)、絶縁層をパターニングおよびエッチングする工程(16)、絶縁層上およびシリコン基板ウェハの少なくとも一部の上に多結晶ゲルマニウムの層を堆積させる工程(18)、多結晶ゲルマニウムをパターニングおよびエッチングする工程(20)、絶縁材料を用いて多結晶ゲルマニウムを被覆する工程(22)、多結晶ゲルマニウムの溶解に十分な温度でウェハを短時間アニールする工程(24)、ウェハを冷却して多結晶ゲルマニウムの液相エピタキシを促す工程(26)、これにより単結晶ゲルマニウム層を形成する工程、CMOSデバイスを完成させる工程(28)を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

半導体装置およびその作製方法

【目的】CMOS構造を有する半導体装置において、精密なしきい値電圧の制御を行うための技術を提供する。

【構成】CMOS回路を作製するにあたって、ゲイト絶縁膜を形成する前の段階で、Pチャネル型半導体装置の活性層に対してP型を付与する不純物元素を添加する。その後、活性層に対して熱酸化処理を施すことで、不純物元素を再分布させ、活性層の主表面における不純物元素の濃度を微量なものとする。その微量な不純物元素によって、精密なしきい値電圧の制御が可能となる。

(もっと読む)

半導体装置

【課題】メモリセルが備えるキャパシタの電荷リークを抑制することができ、且つ、キャパシタの有効面積を増大させると共にその容量値のばらつきを抑制する。

【解決手段】SOI層3には分離トレンチ40が形成されており、その中には分離絶縁膜4が形成される。分離絶縁膜4には、分離トレンチ40の内壁を露出する開口部41が形成されており、当該開口部41は絶縁層2にまで達している。キャパシタ102の下部電極(不純物拡散層24)並びに誘電体層21は、開口部41に露出した分離トレンチ40の内壁に延在し、上部電極22の少なくとも一部は開口部41に埋め込まれる。

(もっと読む)

レーザ照射装置、およびレーザ照射方法

【課題】照射面上にレーザの干渉縞を生じさせることがなく、強度分布を均一にしてレーザビームを照射する。

【解決手段】レーザ発振器から出射したレーザビームはを回折光学素子により、強度分布が均一にされる。回折光学素子を通過したビームをスリットを通過させて、ビームの長軸方向の強度の弱い端部を遮断する。ビームを、投影レンズ及び集光レンズを通し、スリットの像を照射面に投影する。投影レンズは、スリットと照射面とが共役の関係になるように配置される。スリットによる回折を防ぎ、強度が均一なレーザを照射面に照射することが可能になる。

(もっと読む)

半導体装置の製造方法およびMOS電界効果トランジスタ

【課題】基板浮遊効果の抑制、およびオフリーク電流の低減化を、実用上充分なレベルで同時に達成すること

【解決手段】 絶縁体12b上の半導体層12cに設けられたp型の素子形成領域18にイオン注入された、n型の第1ドーパントを、アニールにより活性化することで形成されたソース領域20、ドレイン領域22、およびボディ領域24とを備える半導体装置を製造するにあたり、第1ドーパントのイオン注入に先立ち、(a)ボディ領域の形成予定領域内の領域であって、形成されるべきソースおよびドレイン領域との境界領域へのArのイオン注入と、(b)第1ドーパントの活性化のためのアニールよりも高温で、Arのイオン注入により生じた結晶の欠陥を部分的に回復させるための高温アニールとを行う。

(もっと読む)

電気光学装置の製造方法、及び電気光学装置

【課題】プラスチック基板のTG以上の熱処理が必要な各膜においても、ガラス基板に成膜した場合と同等の膜特性を有するプラスチック基板の液晶装置およびその製造方法を提供する。

【解決手段】一対の基板のうち少なくとも一方が樹脂からなる基板間に液晶層が挟持されてなる液晶装置の製造方法であって、形成用基板に分離層を形成する工程と、分離層上に少なくとも導電膜および配向膜を有する被剥離物を形成する工程と、分離層に照射光を照射して、分離層において剥離を生ぜしめ、被剥離物を形成用基板から離脱させる工程と、被剥離物を基板に貼着する工程と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 SOI基板を用いることなく、絶縁体上に形成される半導体層の面積を拡大する。

【解決手段】 開口部13aを介して半導体基板11の表面に接触する支持体14aが設けられた第2半導体層14を第1半導体層上に形成し、第1半導体層13の側面を露出させる露出部17を介してエッチングガスまたはエッチング液を第1半導体層13に接触させることにより、第1半導体層13をエッチング除去し、半導体基板11および第2半導体層14の熱酸化を行うことにより、半導体基板11と第2半導体層14との間の空洞部19に埋め込み酸化膜20を形成する。

(もっと読む)

半導体装置

【課題】ゲート電極の空乏化を抑制しながら、電子移動度の劣化を低減することが可能な半導体装置を提供する。

【解決手段】この半導体装置では、nチャネルMOSトランジスタ50aのゲート電極8aは、ゲート絶縁膜7aを部分的に覆うようにドット状に形成された金属含有層9aと、金属含有層9a上に形成され、ゲート絶縁膜7aの金属含有層9aにより覆われていない部分に接触する下部ポリシリコン層10aとを含み、pチャネルMOSトランジスタ50bのゲート電極8bは、ゲート絶縁膜27aを部分的に覆うように形成された金属含有層29aと、金属含有層29a上に形成され、ゲート絶縁膜27aの金属含有層29aにより覆われていない部分に接触する下部ポリシリコン層30aとを含み、ゲート電極8aおよびゲート電極8bは、互いに異なる金属(HfおよびPt)を含む。

(もっと読む)

半導体装置の作製方法

【課題】低コストで信頼性の高い半導体装置の作製方法を提供する。

【解決手段】基板上に金属膜を形成し、前記金属膜に酸素を含む雰囲気中でプラズマ処理を行うことにより、前記金属膜の表面に金属酸化膜を形成し、前記金属酸化膜上に下地膜を形成し、前記下地膜上に薄膜トランジスタを有する素子層を形成し、前記素子層上に保護層を形成し、前記金属膜、前記金属酸化膜、前記下地膜、前記素子層、及び前記保護層を選択的に除去して、開口部を形成し、前記基板から前記下地膜、前記素子層、及び前記保護層を分離し、可撓性を有する第1及び第2のフィルムを用いて前記下地膜、前記素子層、及び前記保護層を封止し、前記基板付近でのプラズマの電子密度は1×1011cm−3以上1×1013cm−3以下であり、電子温度は0.5eV以上1.5eV以下である。

(もっと読む)

半導体装置、液晶ディスプレイパネル及び電子機器並びに半導体装置の製造方法

【課題】 長期間の使用後もトランジスタの動作が安定な半導体装置、この半導体装置を備えた液晶ディスプレイパネル及び電子機器、並びに前記半導体装置の製造方法を提供する。

【解決手段】 トランジスタT5はそのしきい値電圧の絶対値が増加する方向に変動するように使用されるものであり、トランジスタT6はそのしきい値電圧の絶対値が低下する方向に変動するように使用されるものである。トランジスタT5のチャネル領域6には、リンを1×1012cm−2の濃度で導入し、トランジスタT6のチャネル領域6には、リンを3×1012cm−2の濃度で導入する。これにより、トランジスタT5の作製当初のしきい値電圧の絶対値を、トランジスタT6の初期しきい値の絶対値よりも小さくする。

(もっと読む)

薄膜トランジスタの作製方法、その薄膜トランジスタを用いた表示装置及びその表示装置が組み込まれた電子機器

【課題】薄膜トランジスタを作製する際、従来のCVD法により形成される膜よりも高品質の膜を形成すること、熱酸化法で形成される膜と同等又はそれ以上の品質の膜を基板に影響を及ぼさない温度で形成することを目的とする。

【解決手段】ガラス基板、所定のパターンに形成された非晶質シリコンを含む半導体膜、ゲート電極及び該ゲート電極から延びた配線、ゲート絶縁膜となる絶縁膜、保護膜の少なくとも一つに対し、ガラス基板の温度を該ガラス基板の歪点より100℃以上低い温度とし、低電子温度且つ高電子密度でプラズマ酸化又はプラズマ窒化をおこなう。

(もっと読む)

2,001 - 2,020 / 2,472

[ Back to top ]