Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

3,101 - 3,120 / 3,265

パターン形成構造、パターン形成方法、デバイス及び電気光学装置、電子機器

【課題】パターン形成時に、微細パターンと他のパターンとの各々の高さを同じくすることにより、パターンを含む領域の上面に平坦領域を形成するバンク構造体、パターン形成方法、及び電気光学装置、電子機器を提供する。

【解決手段】機能液により形成するパターンに対応した凸部35が設けられた隔壁構造体であって、第1パターンに対応して設けられた第1凹部55と、第1パターンに接続され、かつ、第1パターンよりも幅が狭い第2パターンに対応して設けられた第2凹部56と、第1凹部55に少なくとも1以上設けられた凸部35と、を備えることを特徴とする。

(もっと読む)

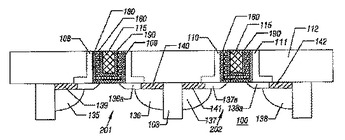

半導体装置及びその製造方法

【課題】短チャネル効果を抑制できる構造であり、しきい値電圧を制御でき、電流駆動力に優れ、高速動作が可能なマルチフィンFETを有する半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置の1態様は、半導体基板上に設けられたソース領域及びドレイン領域と、前記ソース領域及びドレイン領域を接続する複数のフィンと、前記半導体基板の上方に設けられ、前記各フィンの一方の側面側に設けられた第1のゲート電極と、前記半導体基板の上方に設けられ、前記フィンに対して前記第1のゲート電極と対向して前記各フィンの他方の側面側に設けられ、前記第1のゲート電極と分離された第2のゲート電極と、前記各々の第1のゲート電極に接続する複数の第1のパッド電極と、前記複数の第1のパッド電極を接続する第1の配線と、前記各々の第2のゲート電極に接続する複数の第2のパッド電極と、前記複数の第2のパッド電極を接続する第2の配線とを具備する。

(もっと読む)

有機電界効果半導体装置及びその製造方法、並びに有機半導体層及びその形成方法

【課題】有機半導体層の構成分子の配向を密にできる高性能な有機電界効果半導体装置及びその製造方法を提供すること。

【解決手段】有機電界効果半導体装置1は、基体上2に形成された第1電極3及び第2電極5と、これらの電極間に形成された有機半導体層7と、この有機半導体層7に絶縁膜8を介して電界を印加する第3電極9とを備え、基体2は外部刺激により伸縮する材質からなり、この基体2の収縮状態で有機半導体層7の有機半導体分子4が密に、望ましくは接触し合って配向されている。これにより、第1電極及び第2電極間のキャリア移動度を大きくすることができ、オン電流値及びオン・オフ比の特性が向上する。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、微細な形状を有する半導体領域の形成方法を提供する。バラツキの少ない半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、半導体膜の一部にレーザ光を照射し、絶縁層を形成した後、該絶縁層をマスクとして半導体膜をエッチングして、所望の形状を有する半導体領域を形成した後、該半導体領域を用いる半導体装置を作製する。本発明では、公知のレジストを用いたフォトリソグラフィー工程を用いずとも、所定の場所に微細な形状を有する半導体領域を形成することが可能である。

(もっと読む)

直列接続されたトランジスタ列を組込んだプログラマブルメモリアレイ構造およびこの構造を製造して作動させるための方法

三次元フラッシュメモリアレイは、直列接続されたNAND列に電荷蓄積誘電体が配置された薄膜トランジスタを組込んで、4F2のメモリセルのレイアウトを達成する。各NAND列はそれぞれ、グローバルビット線にNAND列の一方端を結合し、共有されたバイアスノードに他方端を結合するための2つのブロック選択デバイスを含む。ブロック内のNAND列の対は、同じグローバルビット線を共有する。メモリセルは、ブロック選択デバイスと同様に、好ましくはデプリーションモードのSONOSデバイスである。メモリセルは、デプリーションしきい値電圧付近にプログラミングされ得、ブロック選択デバイスは、デプリーションモードのしきい値電圧付近の電圧を有するプログラム状態に維持される。2つ以上の層上のNAND列は、1つの層上のグローバルビット線に接続され得、好ましくは、垂直方向の積層型ビアにより、ともに接続され得る。  (もっと読む)

(もっと読む)

透過型光変調素子の製造方法

【課題】 設計の自由度の大きい、構造が簡単で、コスト安で、制御が簡単で、波長依存性がない電気機械式光シャッター素子を、高精度・高品質・低価格で製造できる製造方法を提供する。

【解決手段】 透過型光変調素子の製造方法において、まず、Si(シリコン)基板上に駆動回路を形成し、次に、その上に透過型光変調部の成膜をしてパターニングを行い、その後、前記駆動回路と前記透過型光変調部を前記Si基板から透明基板上に転写するようにした。

(もっと読む)

基板構造及びその製造方法

【課題】 触媒材料をパターニングすることなく、従って基板上の他の部分にダメージを与えたり、当該触媒材料が汚染されたりすることなく、容易且つ確実に基板上の任意の形状・面積の所定領域にCNTを成長させる。

【解決手段】 シリコン基板1上の所望部位にTi膜2をパターン形成し、Ti膜2を覆うように基板1上にCo膜3を形成する。そして、熱CVD法により600℃程度でCo膜3表面のうち、下部にTi膜2の形成された部位のみにCNT4を形成する。CNT4の長さはTi膜2の厚みを調節することにより制御できる。

(もっと読む)

転写元基板、薄膜半導体装置、薄膜半導体装置の製造方法、電気光学装置及び電子機器

【課題】 フレキシブル基板に形成された薄膜半導体装置が金属膜の内部応力の影響を受けにくい、転写元基板、半導体装置及びその製造方法等を提供する。

【解決手段】

本発明の転写元基板(10)は、表面に剥離層(100b)が形成された基板(100a)と、基板上に剥離可能に形成される複数の薄膜半導体回路(D)と、基板上に形成される、薄膜半導体回路(D)を構成する成膜と同じ膜を含むプロセスモニタ部(PM)及び薄膜半導体回路(D)の外部接続端子部のうちの少なくともいずれかと、を含み、プロセスモニタ部及び外部接続端子部のうちの少なくともいずれかに含まれる複数の成膜のうち、相対的に残留応力の高い成膜のパターン(105)を小面積のパターンの集合によって構成してなる。

(もっと読む)

横型MOSトランジスタ

【課題】 配線抵抗及び配線容量を低減するとともに、チップ面積を削減する。

【解決手段】 SOI基板30は、シリコン基板31の上にシリコン酸化膜32が形成され、このシリコン酸化膜32の上にN−型シリコン層33が形成されて構成される。ドレイン領域35は、シリコン層33の表面からシリコン酸化膜32まで到達して形成される。ドレイン電極42は、SOI基板30の裏面に電気的接触して形成される。導電体プラグ41は、ドレイン領域35の表面からドレイン領域35およびシリコン酸化膜32を貫通してシリコン基板31中に延在して、ドレイン領域35およびシリコン基板31に電気的接触して形成される。

(もっと読む)

アクティブマトリクス基板の製造方法及び電気光学装置並びに電子機器

【課題】着弾した液滴を確実に溝内に塗れ拡がらせて細線化を可能にする

【解決手段】基板上にゲート配線を形成する第1の工程と、ゲート配線上にゲート絶縁膜を形成する第2の工程と、ゲート絶縁膜を介して半導体層を積層する第3の工程と、ゲート絶縁層の上にソース電極及びドレイン電極を形成する第4の工程と、ソース電極及び前記ドレイン電極上に絶縁材料を配置する第5の工程と、絶縁材料を配置した上に画素電極を形成する第6の工程と、を有し、第1の工程及び第4の工程及び第6の工程の少なくとも一つの工程では、機能液32が塗布される被塗布領域31と、被塗布領域31を囲んで形成されたバンクBとを有し、被塗布領域に対する機能液の接触角と、バンクに対する機能液の接触角との差が40°以上であり、バンク間の溝幅Wが、吐出された機能液の液滴の直径Dよりも小さい基板Pに対して機能液を吐出する。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】 金属ゲート電極、金属ソース領域および金属ドレイン領域を備え、電流駆動能力を高めた電界効果型トランジスタおよびその製造方法を提供することである。

【解決手段】 ソース領域26、ドレイン領域28、およびゲート電極31n、31pをシリサイド等の金属材料により構成し、nチャネルMISFET24nでは、ゲート電極31nの仕事関数Wgとソース領域26の仕事関数Wsとの関係がWg<Wsであり、pチャネルMISFET24nでは、ゲート電極31pの仕事関数Wgとソース領域26の仕事関数Wsとの関係がWg>Wsであるように金属材料を選択する。

【効果】 ソース領域26とチャネル領域29との界面のバリア高さが低下し、チャネル領域29のキャリア濃度が向上し電流駆動能力が向上する。

(もっと読む)

レーザ処理装置、レーザ処理方法及び半導体装置の作製方法

【課題】

線状レーザの走査回数を減少させ、レーザアニールにかかる時間を短縮させ、半導体装置の作製工程、作製時間、作製にかかるコストを短縮させることを課題とする。

【解決手段】

本発明では、線状レーザビームの照射面に重なり合うように高温の気体を局所的に噴き付ける。線状レーザビームは、レーザ発振器から射出したレーザビームをレンズに入射することにより得られる。高温の気体は、気体圧縮ポンプで圧縮された気体をノズル型ヒータにより加熱することによって得られる。加熱された気体は、線状レーザビームの照射面に重ね合わせるように噴出する。

(もっと読む)

液晶パネル及び液晶表示装置

【課題】 開口率を高めると共に、全画素への書き込み時間を短縮することができる液晶パネル及び液晶表示装置を提供すること。

【解決手段】 液晶パネルを構成するTFT基板100において、ゲートバスライン101とデータバスライン102が互いに直交する方向に配線され、両バスラインの交差箇所の近傍にスイッチング素子(TFT)107が設けられ、さらに、各画素毎に設けられた画素電極104との間で補助容量Csを形成するCsバスライン103が、データバスライン102と平行な方向に配線されている。ゲートバスライン101、データバスライン102及びCsバスライン103は、それぞれ同じ配線間隔で配線され、各Csバスライン103を境界として正方形状の画素領域が画定されている。

(もっと読む)

半導体装置、半導体装置の製造方法、電気光学装置及び電子デバイス

【課題】 表面が平坦かつ均一な膜厚のゲート絶縁膜等を形成することが可能な技術を提供する。

【解決手段】 各半導体膜202A、202Bを囲繞するように隔壁210を形成する。その後、隔壁210によって囲繞された囲繞領域SA、SB内に液体材料を配置し、これを乾燥、焼成することによりゲート絶縁膜220を形成する。ここで、ゲート絶縁膜220の膜厚は、隔壁210の側壁から離れるにつれ漸次変化しているが、このゲート絶縁膜220の膜厚が漸次変化する部分の幅をDとし、隔壁210から囲繞領域内にある半導体膜202の最も近い部分までの距離をLとした場合、L≧Dの関係が成立するように、隔壁210の配置位置や上記液体材料の乾燥に関わるパラメータを制御する。

(もっと読む)

半導体装置

【課題】 半導体装置に於いて、高い短チャネル効果耐性並びに高い電流駆動能力を保ちつつ、ゲート絶縁膜中の電場の緩和を図る。その結果として高電流駆動能力且つ高信頼性の、高性能な微細半導体装置を提供する。

【解決手段】 チャネルの形成される領域が稜を持つ電界効果トランジスターに於いて、稜の近傍に於いてはゲート絶縁膜が他の領域よりも厚く形成されている、ないしゲート絶縁膜は積層であり、積層を形成する層の内で誘電率の低い層が稜の近傍に於いて他の領域よりも厚く形成されている。それ故、チャネル領域の電位に対するゲート電極の制御性は良好に保たれたままでゲート絶縁膜中に生ずる電場強度の緩和が図られ、その結果として高電流駆動能力且つ高信頼性の高性能微細半導体装置を実現する。

(もっと読む)

液晶表示装置の製造方法およびTFT基板

【課題】液晶表示装置製造の費用減少、生産性向上。

【解決手段】TFT部及びゲート−パッド連結部に第1及び第2金属膜を蒸着しそれら金属膜をパターニングしゲート電極及びゲートパッドを形成する段階、全面に絶縁膜を形成する段階、第1及び第2非晶質シリコン膜パターンをTFT部の絶縁膜上に形成する段階であって第2非晶質シリコン膜全体の下部表面が第1非晶質シリコン膜表面と当接するようそれらのパターンを形成する段階、ソース及びドレイン電極をTFT部上に形成しソース及びドレイン電極間の第2非晶質シリコン膜を除去する段階、ドレイン電極及びゲートパッドの一部が露出されるよう保護膜を形成しゲートパッドの一部上の絶縁膜を除去する段階、第1及び第2画素電極パターンを形成する段階を含み、第1金属膜はCr、Mo、Ta及びTiのうち1つの金属膜であり、第2金属膜はAl又はAl合金である。

(もっと読む)

半導体装置及びその作製方法

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域に高抵抗不純物領域(HRDまたは低濃度不純物領域)を自己整合的に形成する方法を提供する。

【解決手段】ゲイト電極105上面にマスク106を残し、比較的低い電圧でポーラスな第1の陽極酸化膜107をゲイト電極の側面に成長させる。この陽極酸化膜をマスクとしてゲイト絶縁膜104’をエッチングする。必要に応じては比較的高い電圧でバリア型の第2の陽極酸化膜108をゲイト電極の側面および上面に形成する。第1の陽極酸化膜を選択的にエッチングする。不純物ドーピングをおこなうと、ゲイト電極の下部にはドーピングされず、ゲイト電極に近い領域では、不純物濃度の低い高抵抗領域111,112となる。ゲイト電極から遠い領域では、不純物濃度の高い低抵抗領域110,113となる。

(もっと読む)

半導体装置及びそれを用いた光半導体リレー装置

【課題】 信号遮断時の出力端子間容量Coffを低減し、且つオン抵抗Ronを低減化

したSOI構造の半導体装置及びそれを用いた光半導体リレー装置を実現する。

【解決手段】 パワーMISFET20は、第1のシリコン基板1の表面上にBOX層(

酸化膜層)2が形成され、このBOX層2の表面上にN+ソース層7、P層6、低不純物

濃度オフセット層5、N+ドレイン層8が設けられている。このP層6上には、ゲート絶

縁膜9を介して第1のゲート電極10が設けられている。そして、第1のシリコン基板1

の裏面には、P層6に対向してBOX層2をゲート絶縁膜とする第2のゲート電極15が

設けられている。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

ファラデーカップ装置およびイオンドーピング装置ならびに半導体装置の製造方法

【課題】イオンビームの一部を受容するファラデーカップ31により該イオンビームのビーム電流密度を検出する一方、その検出値が予め設定された条件に基づき、ファラデーカップ31の検出値が設定値になるように制御手段40によりイオン源を制御するようにしたイオンドーピング装置において、ビーム電流密度の設定値を変更しなくても、ビーム電流密度の実際値を変更できるようにし、もって、稼働率を低下させることなくドーズ量を微調整できるようにする。

【解決手段】ファラデーカップ31の受容面に半導体薄膜を設け、この半導体薄膜の温度を変更して該半導体薄膜の導電性を変化させることにより、ファラデーカップ31の検出感度を変更できるようにする。

(もっと読む)

3,101 - 3,120 / 3,265

[ Back to top ]