Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

3,141 - 3,160 / 3,265

液晶表示装置

【課題】 消費電力の小さなものを得る。

【解決手段】 前記画素領域の集合である表示領域をx方向に沿った仮想の線を境にして一方の表示領域と他方の表示領域とに区分けられ、一方の表示領域側の各ゲート信号線に走査信号を供給する走査信号駆動回路と他方の表示領域側の各ゲート信号線に走査信号を供給する走査信号駆動回路とが別個に形成され、かつ、一方の表示領域側の各ドレイン信号線と他方の表示領域側の各ドレイン信号線とが分離されているとともに、一方の表示領域側の各ドレイン信号線に映像信号を供給する映像信号駆動回路と他方の表示領域側の各ドレイン信号線に映像信号を供給する映像信号駆動回路とが別個に形成されている。

(もっと読む)

アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器

【課題】 半導体膜と画素電極の間に導電性材料を吐出して導電膜を形成する際に、導電性材料が半導体膜上から流出することを防止して、導電膜の十分な膜厚を確保することができるアクティブマトリクス基板の製造方法等を提供する。

【解決手段】 基板P上に、格子パターンの配線40,42と、配線40,42に囲まれた領域に配置された画素電極45と、画素電極45及び配線42に導電膜44を介して電気的に接続するスイッチング素子30と、を有するアクティブマトリックス基板20にであって、画素電極45と導電膜44とを電気的に接続する補助導通部50を備える。また、補助導電部50上の一部にバンク61を備える。

(もっと読む)

薄膜トランジスタ製造方法

【課題】 結晶粒の大きさが大きく、残留する金属触媒の量が微量である多結晶シリコン層を製造でき、多結晶シリコン層の特性を制御することができる薄膜トランジスタ製造方法を提供する。

【解決手段】 絶縁基板を準備する段階と、基板上に非晶質シリコン層を形成する段階と、非晶質シリコン層上に屈折率が1.78から1.90のキャッピング層を形成する段階と、キャッピング層上に金属触媒層を形成する段階と、基板を熱処理して非晶質シリコン層を多結晶シリコン層に結晶化する段階を含む。本発明の薄膜トランジスタ制造方法によれば、SGS結晶化法で結晶化時、窒化膜で形成されたキャッピング層の屈折率を制御することにより、結晶粒径が大きい半導体層を得ることができ、電子移動度が大きく、特性が優秀で、特性を制御することができる。

(もっと読む)

配線パターン及びその形成方法、電気光学装置、並びに電子機器

【課題】 配線パターンを形成する際のプロセスタイムを短縮する。

【解決手段】 撥液性を有する基板P上に配線パターンを形成する配線パターン形成方法であって、液滴吐出法によって親液性材料X2を上記基板上に吐出配置することによって親液領域H1を形成する工程と、上記親液領域上に導電性微粒子を含む機能液を配置し乾燥、焼成させることによって上記配線パターンを形成する工程とを有する。

(もっと読む)

電子装置の製造方法およびこの製造に用いる非晶質薄膜形成用インク組成物

【課題】 蒸留又は昇華により精製される有機低分子材料を材料利用効率の高いインクジェット法を用い、スループットが高く、大型有機ELパネルや有機薄膜トランジスタ等の電子装置の製造が可能なる方法を提供する。

【解決手段】 2種類の溶剤を混合し、最適インク粘度の確保と、乾燥過程におけるインクの表面張力並びに上記有機材料の溶解限を増加させることによって、隔壁層で区画された凹領域のみに選択的に、インクジェット法で有機材料の非晶質膜形成する。2種類の溶剤の第一の溶剤は溶解度が0.5wt%以上の第1溶媒で、第二の溶剤は溶解度が0.1wt%以下の第2溶媒である。第1溶媒の沸点は第2溶媒の沸点よりも高い方が望ましく、このインク溶剤系を用いることによって、インク中の第1溶媒の比率が乾燥と共に増加することから、結晶核や凝集の発生を抑制でき、均一な非晶質薄膜形成が可能となる。

(もっと読む)

アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器

【課題】 ドライプロセスとフォトリソエッチングを組み合わせた工程の回数を低減することができるアクティブマトリクス基板の製造方法等を提供することを目的とする。

【解決手段】 アクティブマトリクス基板20の製造方法において、第1方向又は第2方向のいずれか一方の配線42が交差部56において分断された格子パターンの配線40,42,46を基板P上に形成する第1工程と、交差部56及び配線40,42,46の一部上に絶縁膜と半導体膜30とからなる積層部を形成する第2工程と、積層部上に分断された配線42を電気的に連結させる導電層49、及び半導体膜30を介して配線42と電気的に接続される画素電極45を形成する第3工程と、を有する。

(もっと読む)

半導体装置およびその作製方法

【課題】 従来のパルス発振のレーザー光による照射を半導体膜に行った場合、半導体表面にリッジと呼ばれる凹凸が形成され、トップゲート型TFTの場合には、素子特性がリッジにより大きく左右されていた。特に、電気的に並列に接続する複数の薄膜トランジスタ間でのバラツキが問題となっている。

【解決手段】 本発明は、複数の薄膜トランジスタからなる回路の作製において、連続発振レーザを用いて半導体膜にレーザ光を照射して溶融する領域の幅LP(微結晶領域を含まない)を大きくし、一つの領域に複数の薄膜トランジスタ(電気的に並列に連結された薄膜トランジスタ)の活性層を配置することを特徴の一つとする。

(もっと読む)

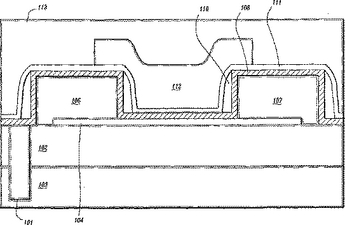

自己整合型ナノチューブ電界効果トランジスタおよびこれを製造する方法

【課題】 自己整合型カーボン・ナノチューブ電界効果トランジスタ半導体デバイスを提供する。

【解決手段】 基板(102)上に堆積したカーボン・ナノチューブ(104)と、カーボン・ナノチューブ(104)の第1の端部および第2の端部にそれぞれ形成されたソースおよびドレイン(106〜107)と、誘電体膜(111)によってカーボン・ナノチューブから分離された、実質的にカーボン・ナノチューブ(104)の一部の上に形成されたゲート(112)とを備える。  (もっと読む)

(もっと読む)

高分子化合物、高分子薄膜およびそれを用いた高分子薄膜素子

【課題】 有機薄膜トランジスタ、有機太陽電池などの高分子薄膜素子用の薄膜の材料として有用な新規な高分子化合物を提供する。

【解決手段】 下記式(1)で示される繰り返し単位と式(2)で示される繰り返し単位とを含み、ポリスチレン換算の数平均分子量が103〜108である高分子化合物

〔式中、Ar1およびAr2は、それぞれ独立に、3価の芳香族炭化水素基または3価の複素環基を表し、X1およびX2は、それぞれ独立に、O、S、C(=O)、S(=O)、SO2等を表し、X1とX2は、同一ではない。YはO、Sを表し、R9はハロゲン原子、アルキル基、アルキルオキシ基等を表す。mは0または1を表し、nは1から6までの整数を表す。oは1から6までの整数を表し、pは0から2までの整数を表す〕

(もっと読む)

半導体装置の製造方法

【課題】大気中に曝すことなく不純物元素の混入を防ぎ、かつフラットバンド電圧のバラツキを抑えるための半導体装置の製造方法を安価にかつ容易に実現する。

【解決手段】基板100上に半導体膜102を形成する第1工程(a)、半導体膜から水素を除去する脱水素処理を行う第2工程(b)、脱水素処理によって活性化した半導体膜表面に不純物元素を含む分子をドープ量に対応した密度で供給し当該半導体膜の結合手を終端させて不活性化する第3工程(c)、不活性化した当該半導体膜にエネルギーを供給して当該結合手に結合した当該分子中の前記不純物元素を当該半導体膜にドーピングしつつ当該半導体膜を結晶化させる第4工程(d)を備え、これらの工程を大気から隔離された環境下で連続的に行う。

(もっと読む)

積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置

【課題】 印刷法のような低コストかつ材料使用効率の高い方法が適用でき、簡便に微細なパターンの形成が可能であって、かつ、パターン形成以外に高付加価値機能を有し、より高移動度の半導体層を有する積層構造体を廉価に提供する。

【解決手段】 エネルギーの付与によって臨界表面張力が変化する材料を含み、より臨界表面張力の大きな高表面エネルギー部3とより臨界表面張力の小さな低表面エネルギー部4との少なくとも臨界表面張力の異なる2つの部位を有する濡れ性変化層2と、この濡れ性変化層2に対して高表面エネルギー部3の部位に形成された導電層5と、濡れ性変化層2に対して少なくとも低表面エネルギー部4の部位に接して設けられた半導体層6と、を有し、濡れ性変化層2は、メチレン基を含み、側鎖に疎水性基を有する高分子材料を含むように積層構造体1を構成した。

(もっと読む)

エッチング方法、微細構造体の製造方法、導電線の形成方法、薄膜トランジスタの製造方法及び電子機器の製造方法

【課題】本発明は、微細なパターンを単純な工程で形成し得るエッチング方法を提供することを目的としている。

【解決手段】 本発明は、基板上に膜形成材料を含む液滴を配置する第1工程と、前記液滴を乾燥し、前記配置時の液滴の径よりも狭い幅の乾燥膜を形成する第2工程と、前記乾燥膜をエッチング保護膜としてエッチングする第3工程と、を含むエッチング方法により、上記課題を解決する。前記第2工程の後に、前記乾燥膜の一部を除去することにより前記乾燥膜をパターニングする第4工程を含んでもよい。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】ゲッタリングのための構造として、電極としても用いることができ、かつ遮光を実現する構造としての、半導体素子の支持体及び半導体素子の支持体の駆動方法を提供する。

【解決手段】半導体素子の支持体100上に形成されているMOSトランジスタ302や、保持容量303等の半導体素子に印加されている最低電位を0Vとしたとき、半導体素子の支持体100の構成要素であるタングステン膜103には、−3Vの電位を与えて駆動する。タングステン膜103に半導体素子の最低電位0Vよりも低い電圧が与えられているため、珪酸ガラス基体101や酸化珪素膜102、104に存在している正の電荷を有する可動性のあるナトリウムイオン等のアルカリ金属は、低い電位に保たれているタングステン膜103の方へ移動し、タングステン膜103に捕らえられることで固定される。

(もっと読む)

表示装置用駆動回路

【課題】 長時間の駆動に対しても信頼性の高い表示装置用駆動回路を提供する。

【解決手段】 互いに接続され、順次に出力信号をそれぞれ生成する複数のステージを有する表示装置用駆動回路であって、前記各ステージは、複数のトランジスタを有し、前記各トランジスタは、制御電極と、前記制御電極上に形成される第1絶縁膜と、前記第1絶縁膜上に形成される半導体層と、前記半導体層上に少なくとも一部分が形成される入力電極と、前記半導体層上に少なくとも一部分が形成される出力電極と、前記入力電極及び出力電極上に形成される第2絶縁膜とを備え、前記半導体層と前記第1絶縁膜の厚さとの比が、0.3〜1.5である。

(もっと読む)

表示装置

【課題】TFTと補助容量により各画素を駆動制御する表示装置において、電圧保持率を十分に維持しながら開口率を最大にすることができる表示装置を提供すること。

【解決手段】駆動回路基板118と、対向基板119と、これらの両基板の間に封止された液晶層112とを備え、駆動回路基板118には各画素に対応した駆動制御用の有機TFT117と補助容量部120とを有しており、有機TFT117のソース電極108、ドレイン電極109、ゲート電極104及び補助容量部120の補助容量電極103、特に補助容量電極103が透明導電材料で形成されることにより、開口率を最大にできる。

(もっと読む)

半導体装置及びその製造方法

【課題】 PN接合耐圧の向上が図れるとともに、スイッチング速度を高めることができる半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極109は、その一端がLOCOS酸化膜107上まで延設されており、ソース電極111は、その一端がゲート電極109よりもさらにLOCOS酸化膜107上に延設される。ゲート電極109およびLOCOS酸化膜107を覆う絶縁膜は、支持基板101の主面方向から見たときに、ゲート電極109のLOCOS酸化膜107側の端部からボディ領域側へかけての端部領域Tにおいて、ゲート電極109とソース電極111との間の膜厚が、ソース電極111のドレイン領域104側端部下における絶縁膜の膜厚並びにゲート電極109のボディ領域105側端部上における絶縁膜の膜厚よりも薄くなるように形成される。

(もっと読む)

半導体デバイスの形成方法およびその構造

一実施形態では、半導体デバイス(10)の形成方法が示される。半導体基板(11)は、第1の部分(14または16)および第2の部分(18または20)を有する。第1の誘電体層(24または26)は半導体基板の第1の部分の上に形成され、第2の誘電体層(30)は半導体基板の第2の部分の上に形成される。ポリシリコンなどのシリコンを含み得るキャップ(28)は第1の誘電体層の上に形成される。第1の電極層(40)はキャップの上に形成され、第2の電極層(32,36または40)は第2の誘電体の上に形成される。  (もっと読む)

(もっと読む)

半導体層のパターン形成方法及び電子素子、電子素子アレイ、表示装置

【課題】FET構造を有する素子の半導体層を、製造工程が簡便で、高速、かつメンテナンス性よく、しかも有機半導体材料にダメージを与えることなく任意のパターン形状で形成できるパターン形成方法と、電子素子、電子素子アレイ、表示装置を提供する。

【解決手段】基板1上に直接またはゲート絶縁層4を介してソース電極5およびドレイン電極6を対向形成すると共に、該ソース電極およびドレイン電極形成領域以外のゲート絶縁層または基板の各臨界表面張力を各電極の形成領域における各臨界表面張力よりも小さい低表面エネルギーとし、ソース電極およびドレイン電極間に半導体材料を含有する溶液を付与してパターン化された半導体層3を形成する。この製造方法によって得られた電子素子をアレイ化し、これを用いて表示装置を構成する。

(もっと読む)

薄膜トランジスタの製法およびそれによって得られた薄膜トランジスタ

【課題】ソースおよびドレインの形成にかかるコストを低減することができる薄膜トランジスタの製法およびそれによって得られた薄膜トランジスタを提供する。

【解決手段】基板1上に薄膜トランジスタを形成する方法であって、ソースS1 およびドレインD1 の形成が、上記基板1上に形成されたSi多結晶膜からなるチャネルC1 の表面のソースS1 およびドレインD1 形成予定部分に、PまたはBを含有するSiGe薄膜を成長させることにより行われる。

(もっと読む)

半導体装置とその製造方法

【課題】PMOSFETにおいて、ショートチャネル効果を抑制でき、より短いゲート長での動作を確保できる半導体装置及びその製造方法を提供することである。

【解決手段】半導体基板に形成されたnウエル領域とnウェル領域上に形成されたゲート電極と、ゲート電極の両端部のnウェルの表面層に形成された一対のボロン含有拡散領域と、ボロン含有拡散領域と同等もしくはより深く、かつ、ゲート電極下においてボロン含有拡散領域と同等もしくはより広い、フッ素、窒素、または炭素からなる群から選択される少なくともいずれかの一の拡散抑制元素を拡散した拡散抑制元素拡散領域と、ボロン含有拡散領域より深く、かつ、横方向端部がボロン含有拡散領域の横方向端部よりゲート電極端から離れた位置にあるp型の不純物拡散領域とを有する半導体装置である。

(もっと読む)

3,141 - 3,160 / 3,265

[ Back to top ]