Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

3,221 - 3,240 / 3,265

半導体装置

【課題】 完全空乏型MISFETでは、単結晶SOI層が数十nm程度と薄くなると、不純物濃度によるしきい値電圧Vthの制御には原理的に限界があり、相補型MISFETにおいてp型とn型の双方の所期のVthを同時に実現することは困難であった。

【解決手段】MISFETのゲート絶縁膜を金属酸化物4と酸窒化膜3の積層とし、ゲート電極5はソース・ドレイン6と同じ導電型の多結晶Si半導体膜を用いて形成する。ゲート絶縁膜と半導体膜のゲート電極に発生するフラットバンド電圧のシフトにより、エンハンスメントの所期のVthが同時に達成される。不純物濃度によりVthを制御する場合に較べ、1つのMISFETに対する不純物の個数の統計的なゆらぎによるVthのばらつきを低減できるため、Vth、電源電圧ともに低く設定することが可能となる。

(もっと読む)

電界効果トランジスタ

【課題】 従来よりもオン電流値を上昇させ、精度の高い回路動作を行なえるようにした、優れた電界効果トランジスタを提供する。

【解決手段】 ゲート絶縁部2に、強誘電体物質を含有するコア部と、常誘電体物質を含有するシェル部とからなるコア・シェル構造粒子を含有させる。

(もっと読む)

薄膜トランジスタを備えた電子装置の製造方法

半導体層(10,20)上部に水素含有層(22)を形成する工程と、半導体層を水素化させるために水素含有層に光照射する工程と、半導体層上部に電極(24、26,28)を形成する工程とを備えた薄膜トランジスタ(42)を備えた電子装置の製造方法。水素が拡散する距離が短くなり、直接的な経路が形成されるので、比較的少ない高レーザフルエンスのレーザパルスを用いた半導体層の高速水素化が可能になる。支持基板(12)はそれ程過熱されないので、この方法は、特に、ポリマー基板上のTFTに有用である。半導体層の結晶化と水素化とを同じ照射工程で行うことができる。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】 電界効果トランジスタのキャリアの移動度を向上させる。

【解決手段】 電界効果トランジスタに、強誘電性及び強磁性をともに有する物質を含有する絶縁部16と絶縁部16に対向して設けられ強磁性を少なくとも有する物質を含有する強磁性部14とを設ける。

(もっと読む)

発光装置

【課題】 アクティブマトリクス方式に代表される、トランジスタ4を駆動素子として用いる電流駆動方式の発光装置において、簡素な構成によって従来よりも発光効率を向上させる。

【解決手段】 発光素子2と、発光素子2を駆動する駆動回路3とを備える発光装置であって、駆動回路3中にトランジスタ4が介装されるとともに、トランジスタ4の電流経路に、発光素子2から発する光により電気抵抗が低下する物質を含有させる。

(もっと読む)

有機半導体を利用した薄膜トランジスタ表示板及びその製造方法

【課題】 量産性が高くてトランジスタ特性も確保できる有機半導体薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】まず、絶縁基板上にゲート線を形成し、ゲート線を覆うゲート絶縁層を形成する。次に、ゲート絶縁層上にソース電極を有するデータ線及びドレイン電極を形成し、有機半導体層と絶縁層を順次に積層する。また、絶縁層のゲート電極上部に陽性の感光膜パターンを形成した後、感光膜パターンをエッチングマスクとして有機半導体層と絶縁層をエッチングしてゲート電極の上部に有機半導体と絶縁体を形成する。その後、有機半導体、絶縁体、データ線及びドレイン電極上にドレイン電極を露出する接触孔を有する保護膜を形成し、接触孔を通じてドレイン電極と連結される画素電極を形成する。

(もっと読む)

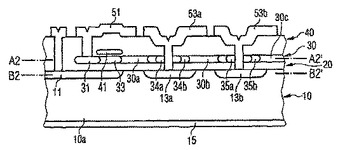

SOIトレンチ横型IGBT

【課題】IGBTにおいて、高耐圧で、大電流での駆動を可能とし、ラッチアップ耐量を高くし、単位面積あたりのオン抵抗を低くすること。

【解決手段】n+エミッタ領域6aとp+コレクタ領域12aとの間のウェハ全面にトレンチ16a,16bを形成し、その中をトレンチ埋め込み絶縁膜17で埋めることによって、耐圧を担持するドリフト領域を折り曲げて、実効的なドリフト長を長くする。トレンチ埋め込み絶縁膜17内に、エミッタ側フィールドプレート15を埋め込み、トレンチ埋め込み絶縁膜17のエミッタ側に生じる横電界を遮蔽することによって、n-ドリフト領域3aとpベース領域4aとのPN接合で発生する電界を緩和する。

(もっと読む)

ナノワイヤ成長および採取のための系および方法

本発明は、ナノワイヤ成長および採取のための系および方法に関する。1つの実施形態において、シリコン前駆体の組み合わせを用いるエピタキシャル配向のナノワイヤ成長のための方法を含む、ナノワイヤ成長およびドーピングのための方法が提供される。本発明のさらなる局面において、犠牲成長層を用いることを通じてナノワイヤの質を改善する方法が提供される。本発明の別の局面において、ナノワイヤを1つの基板から別の基板へと転移させる方法が提供される。  (もっと読む)

(もっと読む)

独立して歪むNチャネル型及びPチャネル型トランジスタ

第一ウェハ上に形成された第一の複数のトランジスタと、第二ウェハ上に形成された第二の複数のトランジスタとを備えた集積回路。第一トランジスタのうち少なくとも実質的に大部分が第一導電型であり、第二の複数のトランジスタのうち少なくとも実質的に大部分が第二導電型である。ウェハ同士が結合された後、第二ウェハの一部が除去されて、第二の複数のトランジスタのチャネルの歪みの圧縮性が、第一の複数のトランジスタのチャネルの歪みの圧縮性よりも高くなる。  (もっと読む)

(もっと読む)

金属トランジスターデバイス

本発明はトランジスターデバイスのチャネル領域の絶縁基板上に形成される金属薄膜あるいは複合金属層が含まれるデプレッションあるいはエンハンスメントモードの金属トランジスターに関する。

(もっと読む)

(もっと読む)

複数誘電体のFINFET構造および方法

【課題】基板(110)から伸長するフィン(112、113、114)を覆う異なる厚さのゲート誘電体(502、504)を有するフィン型電界効果トランジスタ(FinFET)構造のための方法および構造を提供すること。

【解決手段】これらのフィンは、中央チャネル領域と、このチャネル領域の両側にソース領域(60)およびドレイン領域(62)とを有する。厚い方のゲート誘電体(504)は、複数層の誘電体(200、500)を含むことができ、薄い方のゲート誘電体(502)は、それよりも少ない層の誘電体(200)を含むことができる。ゲート誘電体とは異なる材料を含むキャップ(116)を、フィンを覆うように配置することができる。

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

接触部及びその製造方法、薄膜トランジスタ表示板及びその製造方法

【課題】低抵抗の導電物質からなる信号線を用いることにより、良好な接触特性を備える接触構造およびその製造方法を提供する。

【解決手段】接触部形成方法は、基板上に第1配線を形成する段階と、第1配線を覆い、第1配線の一部分を露出させるコンタクトホールを有する絶縁膜を形成する段階と、コンタクトホールによって露出する第1配線の表面に接触層を形成する段階と、接触層を介して第1配線と接続される第2配線を形成する段階とを含み、第1配線は、アルミニウムまたはアルミニウム合金で形成し、第2配線は、ITOまたはIZOで形成する。

(もっと読む)

絶縁耐力の高いSOI半導体素子

本発明は、第1半導体域と第2半導体域との間に配置されたフィールド電極および/またはフィールド領域を備えた、SOI半導体素子に関するものである。電気的結合を、フィールド電極とフィールド領域との間で行うことができる。  (もっと読む)

(もっと読む)

スペーサによって定められる通路内で成長した半導体ナノチューブを組み込んだ垂直型電界効果トランジスタ

【課題】 ICチップの大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込んだ垂直型FET構造体を提供する。

【解決手段】 少なくとも1つの半導体ナノチューブによって定められたチャネル領域を有する垂直型電界効果トランジスタ、及び、こうした垂直型電界効果トランジスタを、スペーサによって定められるチャネルを用いて化学気相成長法によって製造する方法である。各々のナノチューブは、スペーサとゲート電極との間に定められる高アスペクト比通路の底部に位置決めされた触媒パッドにより触媒される化学気相成長法によって、成長する。各々のナノチューブは、スペーサによる境界の存在によって制限される垂直配向を持つ通路内で成長する。通路の開口部から離れたスペーサの底部に、隙間が設けられる。隙間を通って触媒パッドに流れる反応物質が、ナノチューブの成長に関与する。

(もっと読む)

垂直型ナノチューブ半導体デバイス構造体及びその形成方法

【課題】 大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込む垂直型FET構造体を提供する。

【解決手段】 少なくとも1つのナノチューブを組み組む垂直型デバイス構造体、及び、化学気相成長法によってこうしたデバイス構造体を製造する方法である。各々のナノチューブは、触媒パッドによって触媒作用が及ぼされる化学気相成長法によって成長され、誘電体材料のコーティング内に包み込まれる。包み込まれたナノチューブがゲート電極の厚さを通って垂直方向に延びるように、該包み込まれたナノチューブの周りにゲート電極を形成することによって、垂直型電界効果トランジスタを作ることができる。包み込まれたナノチューブ、及び、該包み込められたナノチューブを支持する対応する触媒パッドが1つのキャパシタ・プレートを形成するように、キャパシタを作ることができる。

(もっと読む)

両極性発光電界効果トランジスタ

トランジスタのチャネル長を規定する長さLによって分離される電子注入電極及び正孔注入電極と接触する有機半導体層を備え、発光元の有機半導体層の領域は、電子注入電極及び正孔注入電極の両方からL/10より離れている両極性発光トランジスタ。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びそれを用いた表示装置

有機物を含有する半導体層(15)と、少なくとも互いに電気的に非接触である第一電極(16)、第二電極(12)及び第三電極(14)を含む電界効果トランジスタであって、半導体層(15)の上方に第一電極(16)が配置され、半導体層(15)の下方に第二電極(12)が配置され、半導体層(15)の側方に第三電極(14)が配置され、半導体層(15)は第一電極(16)、第二電極(12)及び第三電極(14)から選ばれるいずれか2つの電極と電気的に接合され、各電極(12,14,16)間には電気的絶縁体層(13,17)を介在させ、第一電極(16)は半導体層(15)の上方を半導体層(15)の外周部より外側にはみ出して覆っている。これにより、有機半導体を用いた電界効果トランジスタであっても、空気や水に強く、かつ長寿命な電界効果トランジスタ及びそれを用いた表示装置を提供する。 (もっと読む)

3,221 - 3,240 / 3,265

[ Back to top ]