Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

3,241 - 3,260 / 3,265

フィン型FETを製造する方法

【課題】 結晶学的に完璧に近く、薄いフィンの固有の構造的な弱さを克服した側壁表面を有する極めて薄いフィンを有するフィン型FETを製造する方法を提供する。

【解決手段】 フィン型FET構造体およびフィン型FETデバイスを形成する方法。この方法は、(a)半導体基板(100)を設けるステップと、(b)基板(100)の上面(105)上に誘電体層(110)を形成するステップと、(c)誘電体層(110)の上面(115)上にシリコン・フィン(135)を形成するステップと、(d)フィン(135)の少なくとも1つの側壁(150A)上に保護層(160)を形成するステップと、(e)フィン(135)のチャネル領域(175)において、少なくとも1つの側壁(150A)から保護層(160)を除去するステップと、を含む。第2の実施形態では、保護層(160)は、保護スペーサ(210A)に変換される。

(もっと読む)

少なくとも一つの電気的コンポーネントを有するフィルム及びその生産プロセス

【課題】

本発明は、少なくとも一つの電気的コンポーネントを有するフィルムと、そのようなフィルムの生産プロセスと、に関するものである。

【解決手段】

放射架橋性接着剤を備えた接着剤層はベースフィルム(61)に塗布される。接着剤層はベースフィルムへパターン形状に塗布され、及び/または、接着剤層がパターン形状に構造化して硬化するようにパターン形状に放射線照射される。キャリアフィルムと電気的機能層とを備えたトランスファーフィルム(41)が接着剤層に塗布される。キャリアフィルム(41)は、ベースフィルム、接着剤層、及び電気的機能層を含むフィルム体から剥がされ、そこではパターン形状に構造化された第一領域では電気的機能層はベースフィルム(61)に残り、パターン形状に構造化された第二領域では電気的機能層は前記キャリアフィルム(45)に残り、ベースフィルム(61)からキャリアフィルムとともに取り除かれる。

(もっと読む)

(もっと読む)

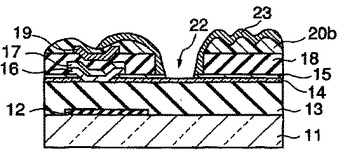

絶縁された金属領域を備えたフィールドプレートを有する横方向薄膜SOIデバイス

横方向薄膜シリコン−オン−インシュレータ(SOI)デバイスにおいて、フィールドプレートは、パッケージ及び表面電荷効果からデバイスを保護するために横方向ドリフト領域に亘って実質的に延在するように設けられている。特に、フィールドプレートは、シリコンドリフト領域にドーピング量勾配により形成される横方向電界分布を呈するように、スペーシングにより相互に横方向において絶縁される複数の金属領域からなる層を備えている。  (もっと読む)

(もっと読む)

液晶表示装置の製造方法

アクティブマトリクス型液晶表示装置の薄膜トランジスタにおける下地電極上の絶縁膜上にフォトエンボッシング材料を用いて凹凸を有する有機膜を形成し、この有機膜にドライエッチングを施して有機膜の膜厚を減少させてコンタクトホール形成領域の絶縁膜を露出させる。その後、露出した絶縁膜にドライエッチングを施してコンタクトホールを形成すると共に下地電極を露出させ、得られた構造上に反射電極を形成して、露出した下地電極と反射電極とを接続する。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

欠陥解析を実行するための方法及びそのシステム

回路欠陥解析及びプロセス問題識別を実行するための方法は、テスト信号を回路に印加するステップと、テスト信号に応答して生成された応答信号を得るステップと、応答信号を参照情報と比較するステップと、比較するステップの結果に基づいて回路内の欠陥を分類するステップと、欠陥分類に基づいて、欠陥を引き起こした製造プロセスにおける問題を識別するステップとを有している。参照情報は、製造プロセス中に発生する可能性がある予め定義されたタイプの欠陥に対応する1つ又は複数の信号プロフィルを含むことができる。欠陥の分類は、応答信号が、信号プロフィルのうちの1つ又は複数内に入るかどうか判定することによって実行されることが好ましい。応答信号が2つ以上の信号プロフィル内に入る場合には、各プロフィルについて確率を決定することができる。次いで、欠陥は、その信号プロフィルがより高い確率を有する欠陥タイプに対応するものとして分類することができる。処理システムは、同様の方法を使用して、欠陥の分類及びプロセス問題識別を実行する。 (もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

電界効果トランジスタ構成および電界効果トランジスタ構成の製造方法

有機半導体を有する電界効果トランジスタ、特に相互接続構造を有する複数の電界効果トランジスタを含むデバイスを製造する方法が提供される。ここで、4層に対して3つのフォトリソグラフィ・マスクが使用される。それに加えて、トランジスタがトップ・ゲート構造で提供され、有機半導体層(307)および誘電体層(309)が構造であり、一緒にパターン化される。電界効果トランジスタ(300)に関連しない領域または第1および第2導電体層(303,305,501)の交差導電体部に関連しない領域から半導体層(307)および誘電体層(309)を取り除くことができる。  (もっと読む)

(もっと読む)

薄膜トランジスタを備えた平板表示装置

【課題】 薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】 各駆動薄膜トランジスタの活性層の結晶粒の差によって、そして、駆動薄膜トランジスタの活性層のサイズを変更せずホワイトバランスを合せ、各副画素に最適の電流を供給することによって適正な輝度を得、寿命を短縮させないようにするためのものであって、自己発光素子を備えた複数の副画素を含む画素と、前記各副画素に備えられて少なくともチャンネル領域を有する半導体活性層を備え、前記自己発光素子に各々接続されて電流を供給するものであって、前記活性層の少なくともチャンネル領域が前記副画素別にその結晶粒のサイズまたは形状が相異なるように備えられた駆動薄膜トランジスタと、を含むことを特徴とする平板表示装置。

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法並びに液晶表示装置

【課題】 本発明の目的は、液晶配向の不良を減少させ、開口率を高めることにある。

【解決手段】 第1絶縁基板と、第1絶縁基板上部に形成されており、ゲート電極を有するゲート線と、ゲート線を覆うゲート絶縁膜と、ゲート絶縁膜上部に形成されている半導体層と、半導体層上部に形成されているソース電極及びドレイン電極とソース電極に連結されており、ゲート線と交差するデータ線と、有機絶縁膜からなっており、ドレイン電極を露出する第1接触孔を有する保護膜と、第1接触孔を通じてドレイン電極と連結されている画素電極と、第1絶縁基板と対向する第2絶縁基板と、ゲート線またはデータ線と重なるブラックマトリックスと、第1絶縁基板と第2絶縁基板の間でブラックマトリックスと重なって位置し、写真エッチング工程で形成された基板スペーサとを含む液晶表示装置を提供する。

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

液晶表示装置の製造方法

【課題】 画素電極近傍の光り抜けを防止できるアクティブマトリックス型液晶表示装置の製造方法を提供すること。

【解決手段】 アレイ基板に対して略平行な電界を発生させることにより、液晶分子の配列を変化させる、アクティブマトリックス型液晶表示装置において、アレイ基板10上に、配線を形成した後透明な絶縁膜20を成膜する工程と、該配線側面に、該配線の膜厚に対する比が0.5以上1.0以下の膜厚の前記絶縁膜を残すように、該絶縁膜をドライエッチングする工程と、前記配線の膜厚に対する比が0.2以下の膜厚の前記配線のみ、ウェットエッチングする工程とを含むようにした。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

電気光学装置及び電子機器

【課題】 液晶装置等の電気光学装置において、耐光性を高め、高品位の画像を表示する。

【解決手段】 電気光学装置は、TFTアレイ基板(10)上に、画素電極(9a)と、これに接続されたTFT(30)と、これに接続された配線(3a、6a)と、TFTの少なくともチャネル領域を上側から覆う上側遮光層(300、6a)と、このTFTの少なくともチャネル領域を下側から覆う下側遮光層(11a)とを備える。基板には、配線に対向する領域に格子状やストライプ状の溝(10cv)が掘られており、この溝内でチャネル領域に対向する領域に凹部(401)が更に掘られている。下側遮光膜は、該凹部内に形成されている。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 薄膜トランジスタの製造方法に関し、LDD領域の抵抗を許容レベルにまで下げるとともにTFTしきい値電圧のシフトを防ぐことを目的とする。

【解決手段】 絶縁性基板上に多結晶Siを形成する工程と、該多結晶Si上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜上に下層ゲート電極と該下層ゲート電極より幅の狭い上層ゲート電極から成る2層ゲート電極を形成する工程と、該2層ゲート電極をマスクにして3属あるいは5属元素から成る不純物をイオン注入する工程と、熱処理する工程と、該2層ゲート電極をマスクにして水素をイオン注入する工程を含むように構成する。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

3,241 - 3,260 / 3,265

[ Back to top ]