Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

3,161 - 3,180 / 3,265

半導体装置及びその製造方法

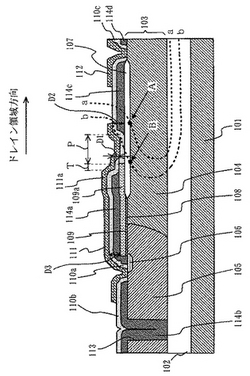

【課題】 PN接合耐圧の向上が図れるとともに、スイッチング速度を高めることができる半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極109は、その一端がLOCOS酸化膜107上まで延設されており、ソース電極111は、その一端がゲート電極109よりもさらにLOCOS酸化膜107上に延設される。ゲート電極109およびLOCOS酸化膜107を覆う絶縁膜は、支持基板101の主面方向から見たときに、ゲート電極109のLOCOS酸化膜107側の端部からボディ領域側へかけての端部領域Tにおいて、ゲート電極109とソース電極111との間の膜厚が、ソース電極111のドレイン領域104側端部下における絶縁膜の膜厚並びにゲート電極109のボディ領域105側端部上における絶縁膜の膜厚よりも薄くなるように形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

半導体薄膜の結晶化方法、結晶化された半導体薄膜を有する基板、そして半導体薄膜の結晶化装置

【課題】非晶質または多結晶半導体薄膜(12)に形成される再結晶領域(21)の正確な配置を容易にし、さらにこの再結晶領域に形成される薄膜トランジスタ(98)等の電子素子の形成工程に利用可能なアライメントマーク(15)を形成する。

【解決手段】表面が絶縁材料からなる基板(11)に非晶質または多結晶半導体薄膜(12)を形成し、第1のレーザ光(19)の照射により該非晶質または多結晶半導体薄膜の所定の位置にアライメントマーク(15)を形成し、該アライメントマークに基いた位置合わせにより、所定の位置に第2のレーザ光(20)の照射による大粒径化された再結晶領域(21)を形成する。

(もっと読む)

TFT−LCDの画素構造及びその製造方法

【課題】 4回のマスク工程によって形成されるTFT−LCDの画素構造及びその製造方法を提供する。

【解決手段】 基板の上に透明導電層と第1金属層を順に形成し、第1金属層と透明導電層をパターン化して、ゲートパターンと画素電極パターンを形成する。次に、ゲート絶縁層と半導体層を基板の上に形成し、パターン化工程によりゲートパターン上方にあるゲート絶縁層と半導体層を保留すると同時に、画素電極パターンの第1金属層を除去する。そして、基板の上に第2金属層を形成し、該第2金属層をパターン化し、半導体層上にソースパターンとドレインパターンを形成する。最後に、基板の上に保護層を形成し、該保護層をパターン化し、画素電極パターンの透明導電層を露出させる。

(もっと読む)

半導体装置の作製方法

【課題】 高い特性及び信頼性を有する半導体装置の作製方法を提供する。

【解決手段】 絶縁膜上の電極や配線形成後のドライエッチングにおけるエッチングダメージを防止する。ドライエッチングのプラズマによる荷電粒子の発生を、半導体層に達しないように、導電層を形成してダメージを抑制する。これにより、特に微細化な構造を持つ薄膜トランジスタにおいて、トランジスタ特性の劣化を生じさせない方法を提供することを目的とする。

(もっと読む)

半導体装置

【課題】 SOI基板上に、高精度なアナログICが形成された半導体装置を安価に提供する こと。

【解決手段】 SOI基板上に形成した半導体集積回路において、ブリーダー抵抗は単結晶シ リコンデバイス形成層で形成し、ブリーダー抵抗の上部には、薄い酸化膜を介して上部抵抗値 固定用電極を設けてそれぞれの下部に位置するブリーダー抵抗と同一の電位に固定し、基板部 分には不純物拡散領域を設けて、それぞれの上部に位置するブリーダー抵抗と同一の電位に固 定するようにした。さらに1つの電位固定用のコンタクトホールに埋め込まれた導電体により 、上部抵抗値固定用電極とブリーダー抵抗と不純物拡散領域の3つを一括して電気的に接続し た半導体装置とした。

これにより高精度で安価なアナログICを提供することができる。

(もっと読む)

光変調素子、結晶化装置、結晶化方法、薄膜半導体基板の製造装置、薄膜半導体基板の製造方法、薄膜半導体装置、薄膜半導体装置の製造方法および表示装置

【課題】半導体膜から粒径の大きな結晶相の半導体を得る工程において、以降の工程で、アライメントマークとして利用可能なマーク構造を、同一の露光工程において半導体膜に形成する。

【解決手段】この発明は、光を変調して結晶化のための光強度分布を形成する光強度変調構造SPと、光強度変調構造と一体にまたは独立に設けられ、光を変調して所定形状のパターンを含む光強度分布を形成するとともに結晶化領域の予め定められた位置を示すマーク形成構造MKと、を有することを特徴とする光変調素子3に関する。この光変調素子によれば、絶縁基板上に所定厚さに堆積された半導体膜の任意の位置に、結晶核を形成し、その結晶核から所定の方向に結晶を成長させるとともに、半導体膜の任意の位置にアライメントマークAMを、同一工程で形成できる。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】ゲート配線、データ配線または保護層、ゲート絶縁層を複数のパターンで形成することによって、基板に伝達されるストレスを最小化できる、薄膜トランジスタ基板及びその製造方法を提供する

【解決手段】薄膜トランジスタ基板は絶縁基板、絶縁基板上に形成され、複数に分離されたゲート部分とこれらゲート部分の間を接続するゲート連結部とで構成されるゲート配線、ゲート配線と絶縁されて交差するデータ配線、ゲート配線及びデータ配線と接続されている薄膜トランジスタ、薄膜トランジスタと接続されている画素電極を含む。  (もっと読む)

(もっと読む)

液晶表示素子及びその製造方法

【課題】薄膜トランジスタの製造に使用されるマスクの数を減少させる液 晶表示素子及びその製造方法を提供する。

【解決手段】第1基板上にソース領域とドレイン領域及びチャンネル領域を有したアクティブ層を形成し、その上に第1絶縁膜を形成する段階と、第1絶縁膜上に第1導電膜と第2導電膜を形成、パターニングしてゲート電極とゲートライン及び画素電極を形成する段階と、この上に第2絶縁膜を形成し、前記第1絶縁膜と第2絶縁膜のソース/ドレイン部にコンタクトホールを形成して、前記画素電極の上部の第2絶縁膜を除去する段階と、その上に第3導電膜を形成パターニングして前記コンタクトホールを通じてソース/ドレイン領域と電気的に接続されるソース/ドレイン電極を形成し、前記画素電極の上部の第2導電膜を露出させる段階と、前記第1基板と第2基板間に液晶層を形成する段階とを含む。

(もっと読む)

薄膜トランジスタの製造方法、電気光学装置、および電子機器

【課題】 本発明は、薄膜トランジスタに用いられるゲート電極や半導体膜を、簡易かつ安価な工程によってサブミクロンオーダーの精度で形成する技術を提供することを目的とする。

【解決手段】 本発明は、基板上に、半導体材料を含む液滴(14)を配置する工程と、液滴を乾燥させ、該液滴の少なくとも周縁部に半導体材料を析出させることによって、半導体膜(16)を形成する工程と、を含む半導体薄膜の形成方法、および/または、導電性材料を含む液滴を配置する工程と、液滴を乾燥させ、該液滴の少なくとも周縁部に導電性材料を析出させることによってゲート電極を形成する工程と、を含むゲート電極の形成方法を含む薄膜トランジスタの製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 電界集中による不所望な寄生トランジスタの形成を防止するフィン型FET及びその製造方法を提供する。

【解決手段】 フィン型FETが、支持基板11と、前記支持基板上に設けられた埋め込み絶縁膜12と、前記埋め込み絶縁膜上に設けられた、シリコン層からなる領域に形成されると共に、互いに対向する側面を有するフィン部16と、少なくとも前記側面の一部を覆うように絶縁膜を介して設けられたゲート電極19とを含み、前記ゲート電極19が、前記支持基板11と前記埋め込み絶縁膜12との界面20よりも低い位置から前記側面の一部を覆うように形成されている。

(もっと読む)

半導体装置

【課題】特性の優れた薄膜トランジスタ(TFT)およびTFTを有する半導体集積回路を提供する。

【解決手段】周辺回路およびアクティブマトリクス回路を含む半導体装置において、前記周辺回路および前記アクティブマトリクス回路は、第1の絶縁膜を介して半導体層の下に設けられた第1のゲイト電極および第2の絶縁膜を介して前記半導体層の上に設けられた第2のゲイト電極を含む複数の薄膜トランジスタを含み、前記周辺回路の薄膜トランジスタの半導体層に結晶性半導体が用いられ、前記アクティブマトリクス回路の半導体層に非晶質半導体が用いられたことを特徴とする。

(もっと読む)

配線基板、薄膜トランジスタ、表示装置及びテレビジョン装置の作製方法

【課題】 本発明は、材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置の作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】 本発明の配線基板の作製方法の一は、被処理物を有する第1の領域を形成し、一部の被処理物表面を改質して、第1の領域と境界線を有する第2の領域を形成し、境界線を越えて第1の領域の一部、及び第2の領域に連続的に導電性材料を含む組成物を吐出し、組成物を固化して導電層を形成し、境界線を越えて第1の領域の一部に形成された導電層を除去する。

(もっと読む)

半導体装置

【課題】 SOI基板上に、完全空乏型の高速MOSトランジスタと、高耐圧型MOSトランジスタとを混載した高精度なアナログICが形成された半導体装置を安価に提供すること。

【解決手段】 ブリーダ抵抗はSOI基板上の単結晶シリコンデバイス形成層で形成し、それぞれのブリーダ抵抗の上面には、高速MOSトランジスタのゲート絶縁膜及びゲート電極により抵抗値固定用電極を形成し、下部に位置するブリーダ抵抗と同電位になるようにした。

(もっと読む)

TFTアレイパターン形成方法

【課題】段差部などに生じた印刷レジストパターンの欠落を防止し空隙を埋め、配線の断線やパターンの細りなどを抑制することにある。

【解決手段】基板上に配線や電極を形成したTFTアレイを形成するにあたり、その上から、印刷装置を使用して有機レジスト或いは金属粒子などを分散したレジストを印刷レジストパターン106として形成する。ついで、レジストパターン印刷後に、有機用溶剤雰囲気中に曝すか、或いは熱などの処理によってパターンを軟化させる。これにより、レジストパターン106が馴染み、レジストパターンと下地層間の空隙107やレジストパターンの段切れを修復することができる。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 薄膜トランジスタ表示板の製造工程を簡素化する。また、画素電極の断線を防止できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】 本発明の一実施形態による薄膜トランジスタ表示板の製造方法は、基板上にゲート線を形成する段階と、前記ゲート線上にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜上に半導体層を形成する段階と、前記半導体層上にオーミック接触部材を形成する段階と、前記オーミック接触部材上にデータ線及びドレイン電極を形成する段階と、前記データ線及び前記ドレイン電極上に保護膜を蒸着する段階と、前記保護膜上に第1感光膜を形成する段階と、前記第1感光膜をマスクとして前記ゲート絶縁膜及び前記保護膜をエッチングすることによって、前記ドレイン電極の少なくとも一部と前記基板の少なくとも一部を露出させる段階と、導電体膜を蒸着する段階と、並びに前記第1感光膜を除去し、前記ドレイン電極の露出した部分上に画素電極を形成する段階とを含む。

(もっと読む)

半導体装置及びその製造方法。

【課題】 トランジスタの幅が表面積に依存していた。また、半導体シリコン部分を流れる経路が、抵抗として作用していた。

【解決手段】 SOI基板上に、トランジスタのソース部、ゲート部、ドレイン部をウエハ方向に対し横に並べたトレンチ構造で形成し、トランジスタの実効幅が、ウエハ表面に対し垂直方向に依存した構造とした。その結果、微小な面積で大電流を流せるようなトランジスタが制御性良く製造できるようになった。また、CMOSの形成や、様々な半導体素子などとの混載も形成しやすくなった。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板表面内に複数の異なる結晶方位を有し、その各部において基板へのリーク電流の増大や消費電力の増大を抑制可能な半導体装置及びその製造方法を実現する。

【解決手段】同じ結晶方位<110>同士が所定の角度(例えば45°)だけずれた状態となるよう、2枚の半導体ウェハを貼り合わせてSOI基板を形成する。そのSOI基板の表面の一部を埋め込み絶縁層までエッチングして、その部分にエピタキシャル成長を行う。そして、SIMOX技術により、エピタキシャル成長層形成部にも埋め込み酸化膜を設け、各部をSOI構造とする。

(もっと読む)

応力制御を伴う窒化シリコン膜

アセンブリは、互いに重ねて形成された窒化物エッチストップ層を有する多層窒化物スタックを備え、これら窒化物エッチストップ層の各々は、膜形成プロセスを使用して形成される。多層窒化物スタックを形成する方法は、単一ウエハ堆積チャンバに基板を配置し、堆積の直前に基板に熱的ショックを与えることを含む。第1の窒化物エッチストップ層が基板上に堆積される。第2の窒化物エッチストップ層が第1の窒化物エッチストップ層上に堆積される。 (もっと読む)

薄膜集積回路の作製方法

【課題】 薄膜集積回路の飛散を防止する。

【解決手段】 本発明の薄膜集積回路の作製方法では、基板の一表面に剥離層を選択的に形成する。そうすると、剥離層が設けられた第1の領域と、剥離層が設けられていない第2の領域が形成される。次に、剥離層の上方に、薄膜集積回路を形成する。続いて、剥離層を露出させる開口部を形成し、開口部にエッチング剤を導入し、剥離層を除去する。そうすると、剥離層が設けられた領域では空間が生じるが、剥離層が設けられていない領域では空間が生じない。このように、剥離層を除去した後に、空間が生じない領域を設けることにより、剥離層を除去した後の薄膜集積回路の飛散を防止する。

(もっと読む)

3,161 - 3,180 / 3,265

[ Back to top ]