Fターム[5F110PP11]の内容

Fターム[5F110PP11]に分類される特許

1 - 20 / 177

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

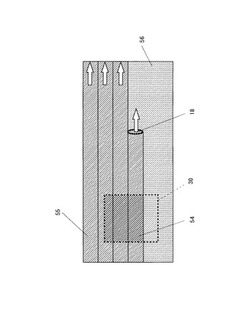

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】チャネル保護型の薄膜トランジスタにおいて、オフ特性及び信頼性に優れた薄膜半導体装置の製造方法を提供する。

【解決手段】基板1を準備する第1工程と、基板1上にゲート電極2を形成する第2工程と、ゲート電極2上に第1絶縁膜としてゲート絶縁膜3を形成する第3工程と、ゲート絶縁膜3上に非結晶質の半導体薄膜4aを形成する第4工程と、非結晶質の半導体薄膜4a上に第2絶縁膜としてチャネル保護膜5を形成する第5工程と、チャネル保護膜5の上方からレーザー光を照射することにより、非結晶質の半導体薄膜4aを結晶化させて結晶化領域を形成する第6工程と、結晶化領域の上方にソース電極7S及びドレイン電極7Dを形成する第7工程と、を含み、第5工程において、チャネル保護膜5は、前記レーザー光に対して透明となるように形成される。

(もっと読む)

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】高性能な電気特性を実現しうるpoly−Si膜の結晶性分布を有した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、絶縁性の基板と、前記絶縁性基板の上に形成されたゲート電極と、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜の上に形成された結晶シリコン膜と、前記結晶シリコン膜の端部の上方に形成されたソース電極と、前記結晶シリコン膜における前記ソース電極が形成された端部と対向する端部の上方に形成され、前記ソース電極と離間しているドレイン電極とを具備する薄膜トランジスタにおいて、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されている前記結晶シリコン膜の端部から、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されていない前記結晶シリコン膜の中央部に向かって、前記結晶シリコン膜の結晶化率が小さくなっている。

(もっと読む)

半導体装置及びその製造方法、発光装置並びに電子機器

【課題】チャネル保護層に対するソース、ドレイン電極及び不純物層のアライメントずれが生じた場合であっても、オン電流特性のばらつきを抑制することができる半導体装置及びその製造方法を提供する。また、製品の歩留まりを向上させることができるとともに、良好な画質を有する発光装置、並びに、該発光装置を実装した電子機器を提供する。

【解決手段】薄膜トランジスタTFTの半導体層14上に設けられるチャネル保護層15と、ソース、ドレイン電極18及び不純物半導体層17との間に、カーボン絶縁膜16が設けられている。半導体層14は、例えば非晶質シリコンをレーザーアニール処理することにより結晶化された微結晶シリコンにより形成されている。カーボン絶縁膜16は、このレーザーアニール処理において適用される光熱変換層であり、当該光熱変換層の一部を残したものである。

(もっと読む)

非晶質半導体膜の結晶化方法、薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法

【課題】特性の優れた半導体膜を簡便に得ることができる微結晶半導体膜の結晶化方法と、これを応用した薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、基板1上に形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3を介してゲート電極2の対面に形成され、ソース領域となる第1非晶質領域41、ドレイン領域となる第2非晶質領域42、及び第1非晶質領域41と第2非晶質領域42との間に配置されたチャネル領域となる結晶性領域43を有する半導体膜4と、半導体膜4上に結晶性領域43と直接接触することなく形成され、ソース領域及びドレイン領域とそれぞれ電気的に接続されたソース電極81及びドレイン電極82と、を備えるものである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体膜の製造方法、薄膜トランジスタの製造方法および表示装置の製造方法

【課題】半導体薄膜の結晶の不均一性を緩和し、薄膜トランジスタの動作特性を向上させることが可能な半導体膜の製造方法を提供する。

【解決手段】

基板10上に非晶質シリコン膜15Aおよび光熱変換層16をこの順に形成する。光熱変換層16を介して非晶質シリコン膜15Aに第1ビームL1を照射することにより非晶質シリコン膜15Aに高温過熱領域11を形成する。同時に、第2ビームL2を照射することにより高温過熱領域11の走査方向の前後に低温過熱領域12(昇温領域12Aおよび徐冷領域12B)を形成する。非晶質シリコン15Aでは、第1レーザL1の照射により結晶成長が始まり、第2レーザL2の照射により昇温、徐冷されるため、非晶質シリコン15Aの結晶化が緩やかに進行し、結晶粒径の不均一性が緩和される。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】金属箔から成る支持層、支持層の上に形成された半導体構造部、および半導体構造部の上に形成された樹脂フィルムを有して成るフレキシブル半導体装置。かかるフレキシブル半導体装置では、樹脂フィルムには開口部が形成されており、その開口部に半導体構造部の表面と接触する導電部材が形成されており、半導体構造部が半導体層および半導体層の表面に形成された絶縁層を有して成る。

(もっと読む)

非晶質半導体膜の結晶化方法、並びに薄膜トランジスタ、半導体装置、表示装置、及びその製造方法

【課題】近接配置される半導体膜の一方のみを精度良く選択的に結晶化することができ、アモルファスTFTと微結晶シリコンTFTを同じ透明絶縁性基板上に同時に形成することや、非晶質シリコンと微結晶シリコンが一つの半導体層内で混在したTFTを得ることが可能となる。

【解決手段】本発明の非晶質半導体膜の結晶化方法においては、透明絶縁性基板上にゲート電極と、ゲート絶縁膜と、非晶質半導体膜と、透光性絶縁膜を順次形成する工程と、開口を有したメタル膜をこの透光性絶縁膜上にパターニング形成する工程と、メタル膜を遮光マスクとして機能させてレーザーを照射することにより、開口により露出する領域においてのみ非晶質半導体膜を結晶性半導体膜に変換するレーザーアニール工程とを備えるものである。

(もっと読む)

半導体薄膜の形成方法、半導体薄膜の検査装置および半導体薄膜

【課題】レーザアニールによる結晶化を利用した半導体薄膜の形成において、その結晶化度を従来よりも高精度に評価することが可能な半導体薄膜の形成方法を提供する。

【解決手段】p−Si膜23の結晶化度の検査処理の際に、p−Si膜23およびa−Si膜230へ向けて照射光Loutを照射し、p−Si膜23およびa−Si膜230の透過画像を取得する。画像処理用コンピュータ15において、p−Si膜23(結晶化領域51)の透過輝度とa−Si膜230(未結晶化領域50)の透過輝度との透過コントラストを求める。この際、予め形成された基準マーク6を用いて、結晶化領域51内および未結晶化領域50内におけるコントラスト算出用領域60,61を特定し、これらのコントラスト算出用領域60,61を用いて透過コントラストを求める。そして、求めた透過コントラストに基づいて、p−Si膜23に対する選別を行う。

(もっと読む)

多結晶半導体膜及びその製造方法

【課題】半導体膜の表面に優れた光閉じ込め効果を有する凹凸形状を形成して光電変換素子の感度を向上させる。

【解決手段】多結晶半導体膜10は、基板1上に形成されており、ラテラル結晶を含む。多結晶半導体膜の表面に自己組織化的に形成されたテクスチャ構造を有し、その表面の二乗平均粗さが4nm以上である。

(もっと読む)

半導体装置の製造方法、半導体検査装置および結晶化度検査方法

【課題】本発明は、アニール処理後の結晶化の状態について、非接触で精度よく、しかも効率的に、評価を行えるようにする。

【解決手段】アニール処理後の半導体層を有する多層構造体210を搭載するステージ201と、前記半導体層に対して光を照射する光源202と、前記光源202による光の照射によって得られるラマン散乱光を受光する受光部205と、前記受光部205が受光した前記ラマン散乱光を用いて前記半導体層の結晶化度を検査する検査部207とを備えた半導体検査装置200において、前記検査部207は、前記ラマン散乱光のラマンスペクトルによって特定される領域を波数についての所定閾値で領域分割する領域分割部と、前記領域分割をする前の領域全体と前記領域分割をした後の前記所定閾値を超える領域部分との面積比を算出し、その算出結果を前記半導体層の結晶化度とする結晶化度算出部とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】 ガラス基板上に薄膜トランジスタ及び配線を有する半導体装置を製造する方法において、ガラス基板上に下地絶縁層を形成する工程と、前記下地絶縁層上に下地バリア層を形成する工程と、前記下地バリア層上にシード層を形成する工程と、前記シード層を前記配線に対応する形状にパターニングしてシード層パターンを形成する工程と、前記シード層パターンの表面に銅配線層を無電解めっき法で形成する工程と、前記銅配線層マスクとして前記下地バリア層をパターニングする工程と、前記銅配線層を被覆するように絶縁層を形成する工程とを備えたことを特徴する半導体装置の製造方法。

(もっと読む)

半導体製造方法、半導体製造装置、半導体装置および表示装置

【課題】均一性の極めて高いアニール処理結果を実現しつつ、その場合であっても生産性が損なわれてしまうことなく高スループット化を実現できるようにする。

【解決手段】基板上に少なくとも非晶質シリコン膜14と光吸収層16とが積層されてなる多層構造体に対して、前記光吸収層16の側から光を照射して当該光による局所加熱を行い、前記非晶質シリコン膜14を微結晶シリコン膜または多結晶シリコン膜に改質するアニール処理工程を備え、前記アニール処理工程では、前記局所加熱にあたり同一走査ライン上に複数の光ビームを配置するとともに、前記光吸収層16の熱伝導率をk、密度をρ、比熱をc、走査すべきライン長/走査速度をtpとした場合に、前記複数の光ビームを少なくとも間隔L=2×{k・tp/(ρ・c)}1/2だけ隔てて配置する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタにおけるオン電流の向上とリーク電流の低減を図る。

【解決手段】微結晶シリコン領域51の両端側が非晶質シリコン領域52となっている半導体膜5bを備えるスイッチトランジスタ5において、チャネル保護膜5dが、半導体膜5bにおける微結晶シリコン領域51を覆いつつ、そのチャネル保護膜5dの両端側で、微結晶シリコン領域51側の非晶質シリコン領域52の一部を覆い、また、ソース・ドレイン領域となる不純物半導体膜5f,5gが、微結晶シリコン領域51と直接接触せず、半導体膜5bにおける非晶質シリコン領域52と接することで、ドレイン電極5hとソース電極5iとが不純物半導体膜5f,5gを介して半導体膜5bと電気的に接続することで、微結晶シリコンに起因するホールエレクトロンペアの発生を抑えて、リーク電流の低減を図った。

(もっと読む)

1 - 20 / 177

[ Back to top ]