Fターム[5F110PP36]の内容

Fターム[5F110PP36]に分類される特許

141 - 160 / 204

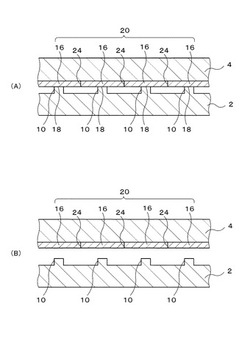

半導体薄膜、半導体装置およびそれらの製造方法

【課題】基板上に結晶方位が制御された擬単結晶半導体薄膜を得ることが可能となる半導

体薄膜およびその製造方法ならびに半導体装置およびその製造方法を提供する。

【解決手段】半導体薄膜の製造方法は、表面に配列された複数の突起部10を設けた単結

晶半導体基板(単結晶シリコン基板2)と表面に半導体薄膜を堆積した基板4とを互いの

表面を向き合わせて結合する。半導体薄膜に熱処理を施して半導体薄膜を固相成長により

結晶化させ、基板4上に、複数の突起部10のそれぞれを起点として複数の略単結晶粒(

結晶シリコン16)から構成される擬単結晶半導体薄膜(擬単結晶シリコン薄膜20)を

形成する。擬単結晶半導体薄膜(擬単結晶シリコン薄膜20)を含む基板4と単結晶半導

体基板(単結晶シリコン基板2)とを分離する。

(もっと読む)

結晶化パターンおよびこれを用いた非晶質シリコンの結晶化方法

【課題】 本発明は、多結晶シリコン薄膜トランジスタを形成するための結晶化パターンおよびこれを用いた非晶質シリコンの結晶化方法を提供するためのものである。

【解決手段】 本発明は、多結晶シリコン薄膜トランジスタを製造するための非晶質シリコンの結晶化方法であって、ガラス基板上に非晶質シリコン膜を形成するステップと、前記非晶質シリコン膜を薄膜トランジスタのアクティブパターンの形態でパターニングして結晶化パターンを形成するステップと、前記結晶化パターンにレーザを照射して多結晶シリコンで結晶化させるステップと、を含み、前記結晶化パターンは、縁部から第1距離以内に位置する周辺領域と、前記縁部から第1距離以上離れて位置する内部領域とを含み、前記内部領域は少なくとも1つ以上の区域に分割され、前記各区域は1つの結晶化誘導パターンを備えると共に、対応する結晶化誘導パターンから第2距離以内に位置するようにしたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高精度の抵抗値を有する抵抗素子を得ることを目的とする。

【解決手段】シリコン基板11上に0.1〜0.5μmの間隔を設けて島状に酸化膜12を形成する工程と、フッ化水素酸溶液を用いたウェット処理を行なう工程と、酸化膜12を備えたシリコン基板11上にシランガスを用いた成膜温度520〜560℃の減圧CVD法によりアモルファスシリコン層14aを形成する工程と、温度890〜960℃、10〜15秒での熱処理を施す工程を含み、アモルファスシリコン層14aを単結晶シリコン層14bに構造変換し、単結晶シリコン層14bで抵抗素子を形成する。

(もっと読む)

半導体装置、集積回路、及び電子機器

【課題】起点部より成長させてなる結晶粒を有する半導体膜を用いたデバイスを3次元配置してなり、いずれの層に配置されたデバイスにおいても所望のデバイス特性を得ることができる半導体装置、及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、表面に複数の微細孔G11,G12を有する起点部層211と、前記微細孔G11,G12を起点として形成された略単結晶粒を含む半導体膜201,202を用いて形成されたデバイス形成層212とを備えたデバイス層101上に、同様の構成を具備したデバイス層102,103を積層してなり、前記デバイス層101〜103に属する前記微細孔(例えば微細孔G21)は、隣接して配置された他の前記デバイス層101〜103に属する前記微細孔(例えば微細孔G11,G31)から平面視で離間した位置に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】結晶粒界の影響が無視し得るほど小さい半導体薄膜から動作半導体膜を形成し、極めて高い移動度の薄膜型の半導体装置を実現する。

【解決手段】幅広領域3aと幅狭領域3bとを有し、幅狭領域3bが幅広領域3aに対して非対称に位置するように連結されてなる形状の非晶質シリコン膜3を形成し、幅狭領域3bをシリコン酸化膜4を介して多結晶シリコン膜5が保温膜として側面から囲む状態で、幅広領域3aから幅狭領域3bへ向かってCWレーザ光を走査して結晶化させ、動作半導体膜11を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置、電気光学装置、並びに電子機器

【課題】同一基板上に、異なる閾値を有する複数の薄膜トランジスタを形成する場合において、製造コスト及びTATの増大を防止する。

【解決手段】基板上に第1の絶縁層を形成する絶縁層形成工程と、第1の絶縁層上に複数の微細孔を形成する微細孔形成工程と、第1の絶縁層上に半導体層を形成する半導体層形成工程と、熱処理を行うことで、微細孔を起点とする結晶粒を成長させて結晶粒界を形成する熱処理工程と、半導体層にソース領域、ドレイン領域及びチャネル領域を形成するトラジスタ領域形成工程と、ゲート電極パターン、ソース電極パターン及びドレイン電極パターンを形成することにより薄膜トランジスタを形成する薄膜トランジスタ形成工程とを有し、微細孔形成工程では、所定の薄膜トランジスタのチャネル領域内において、1つ以上の結晶粒界が、電流方向に対して略直交するように形成されるように微細孔を配置する。

(もっと読む)

半導体装置の製造方法及び半導体装置、電気光学装置、並びに電子機器

【課題】デザインルールに制限されることなく、薄膜トランジスタのリーク電流を低減する。

【解決手段】基板上に第1の絶縁層を形成する絶縁層形成工程と、第1の絶縁層上に複数の微細孔を形成する微細孔形成工程と、第1の絶縁層上に半導体層を形成する半導体層形成工程と、熱処理を行うことで、微細孔を起点とする結晶粒を成長させて結晶粒界を形成する熱処理工程と、半導体層にソース領域、ドレイン領域及びチャネル領域を形成するトラジスタ領域形成工程と、ゲート電極パターン、ソース電極パターン及びドレイン電極パターンを形成することにより薄膜トランジスタを形成する薄膜トランジスタ形成工程とを有し、微細孔形成工程では、所定の薄膜トランジスタのチャネル領域内において、2つ以上の結晶粒界が、電流方向に対して略直交するように形成されるように微細孔を配置する。

(もっと読む)

半導体装置の製造方法、半導体装置、集積回路、電気光学装置、電子機器

【課題】基板全体に渡って高性能な薄膜トランジスタを安定的に得ることを可能とする半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板(11)の一方面側に凹部(125)を形成する第1工程と、上記基板の一方面側に第一半導体膜(130)を形成する第2工程と、上記第一半導体膜側から上記基板の一方面に向けて平坦化処理を行う第3工程と、上記基板の一方面側に第二半導体膜(130b)を形成する第4工程と、上記第二半導体膜に熱処理を行い、上記凹部を略中心とする略単結晶粒(131)を形成する第5工程と、上記第二半導体膜を用いて半導体素子を形成する第6工程と、を含む。

(もっと読む)

半導体装置の製造方法、半導体装置、集積回路、電気光学装置、電子機器

【課題】凹部を用いた結晶成長をより安定に実現し、高性能な半導体素子を安定して得ることを可能とすること。

【解決手段】本発明にかかる半導体装置の製造方法は、基板(11)の一方面側に凹部(125)を形成する第1工程と、上記基板の一方面側に膜厚Tの半導体膜(130)を形成する第2工程と、上記半導体膜に熱処理を行い、上記凹部を略中心とする略単結晶粒を形成する第3工程と、上記半導体膜を用いて半導体素子を形成する第4工程と、を含み、上記第2工程では、上記凹部の直径Dと深さFがF+T≧4×D+532(nm)の関係を満たすように上記凹部が形成される。

(もっと読む)

多結晶シリコン層、多結晶シリコン層製造方法、および多結晶シリコン層を用いる平板表示装置

【課題】結晶粒大きさの均一性および結晶粒界の規則的な分布を実現できることにより、優秀な特性を備える多結晶シリコン層、多結晶シリコン層製造方法および多結晶シリコン層を用いた平板表示装置を提供する。

【解決手段】基板100上に位置して、面積が400μm2以上であるシード領域170と、シード領域170から成長した結晶化領域190とを含む多結晶シリコン層を提供する。

(もっと読む)

多結晶シリコン層、多結晶シリコン層の製造方法、及び平板表示装置

【課題】結晶粒の大きさや結晶粒界の分布が均一であり、薄膜トランジスタを形成した際に優秀な特性が得られる多結晶シリコン層、多結晶シリコン層の製造方法、及び平板表示装置を提供する。

【解決手段】基板上に非晶質シリコン層120を形成する段階と、非晶質シリコン層120の所定領域が露出するように第1パターン層130を形成する段階と、第2パターン層140を形成する段階と、第2パターン層140上に金属触媒層150を形成する段階と、基板を熱処理することにより、金属触媒が非晶質シリコン層の所定領域に拡散してシードを形成し、シードは非晶質シリコン層120の所定領域を少なくとも幅が3.5μm以上であるシード領域170に結晶化し、シード領域170の結晶性が成長して、非晶質シリコン層120を結晶化領域190に結晶化する段階と、を含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積の増大を抑制しつつ、サリサイド化された素子と非サリサイド化された素子とを同一基板上に混載する。

【解決手段】シリサイド層19a、19b、19cが設けられたソース/ドレイン層17a、17bおよびゲート電極14を半導体基板11に形成した後、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34に非サリサイド素子を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ面積の増大を抑制しつつ、アナログ回路とデジタル回路とを同一基板上に混載する。

【解決手段】半導体基板11上にアナログ回路を形成した後、凹部32が形成された絶縁膜31をアナログ回路上に形成し、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34にデジタル回路を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PチャンネルトランジスタとNチャンネルトランジスタとを異なる半導体層上に混載することにより、伝播遅延の増大を抑制しつつ、全体のプロセス長さを大幅に短縮する。

【解決手段】半導体基板11上にNチャンネルトランジスタ(Pチャンネルトランジスタ)を形成した後、凹部32が形成された絶縁膜31をNチャンネルトランジスタ(Pチャンネルトランジスタ)上に形成し、凹部32内が埋め込まれるようにして非晶質半導体層33を絶縁膜31上に形成し、非晶質半導体層33にレーザを照射することにより、非晶質半導体層33の溶融結晶化を行い、凹部32の周囲に略単結晶半導体粒34を形成し、略単結晶半導体粒34にPチャンネルトランジスタ(Nチャンネルトランジスタ)を形成する。

(もっと読む)

アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置及び電子機器

【課題】半導体装置の光リーク電流が少なく、半導体装置の電気特性が優れており、半導体装置の電気特性ばらつきの少ないアクティブマトリクス基板の製造方法、アクティブマトリクス基板、及びそれを用いた電気光学装置と電子機器を提供することを目的とする。

【解決手段】アクティブマトリクス基板の半導体装置が形成される領域(負荷回路領域及び駆動回路領域)に遮光膜を形成し、遮光膜上の絶縁膜に微細孔を形成し、微細孔周辺に略単結晶半導体膜を形成し、略単結晶半導体膜を用いて半導体装置を形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ及びその製造方法に関し、特に、漏洩電流を減少するための薄膜トランジスタ及びその製造方法を提供する。

【解決手段】可撓性基板100と、可撓性基板100上に形成される拡散防止層110と、拡散防止層110上に少なくとも二個の絶縁物質が積層して形成されるバッファ層120と、バッファ層120の一の領域上にチャンネル層130aとソース/ドレイン領域130bを有して形成される半導体層130と、半導体層130を含むバッファ層120上に形成されるゲート絶縁層140と、ゲート絶縁層140上のチャンネル層130aと対応する領域に形成されるゲート電極150と、ゲート電極150を含むゲート絶縁層140上に形成される層間絶縁層160と、層間絶縁層160にソース/ドレイン領域130bの少なくとも一の領域を露出させる所定のコンタクトホール170有し、ソース/ドレイン領域130bに接続されるように形成されるソース/ドレイン電極180a、180bと、を備えている。

(もっと読む)

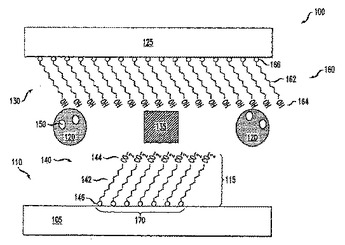

オンデマンド結晶構造成長

少なくとも1つの結晶化核形成部位が配置された表面を有する基板を備える装置。この装置はさらに、第2の表面を有する第2の基板を備える。第2の表面は、結晶化開始材料をアモルファス状態または初期結晶状態で維持するように構成される。結晶化核形成部位は、結晶化開始材料にある性質を与えるように構成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】SOS基板の素子形成領域の単結晶シリコン層とサファイア基板の間に絶縁膜層を形成する場合においても、素子形成領域に突合面による欠陥を形成しない手段を提供する。

【解決手段】サファイア基板に単結晶シリコン層を積層したSOS基板の単結晶シリコン層に、複数の半導体素子を形成した半導体装置において、SOS基板の素子形成領域のサファイア基板と単結晶シリコン層との間に形成された絶縁膜層と、絶縁膜層に隣接し、サファイア基板上に形成されたエピタキシャル層と、このエピタキシャル層を核とした単結晶シリコン層の絶縁膜層上へのエピタキシャル成長により形成された突合面と、絶縁膜層上の突合面を含む領域に形成され、隣合う素子形成領域間を絶縁分離する素子分離層とを備える。

(もっと読む)

電気光学装置及びその製造方法、電子機器、並びに半導体装置

【課題】例えば液晶装置等の電気光学装置において、表示領域ではポリシリコンからなる半導体層を形成すると共に周辺領域では平坦な単結晶シリコン膜からなる半導体層を形成する。

【解決手段】電気光学装置は、基板上に、表示領域に配列された複数の画素部と、表示領域の周辺に位置する周辺領域に配置されており、複数の画素部を駆動するための、第1単結晶シリコン膜からなるSOI(Silicon On Insulator)構造をなす第1半導体層及び該第1半導体層上にエピタキシャル成長により形成された第2単結晶シリコン膜からなる第2半導体層を有する半導体素子を含む駆動回路とを備える。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置および電子機器

【課題】 薄膜トランジスタを形成するための結晶成長の起点となる微細孔の良否を確認でき、また、所望の大きさのシリコン結晶粒が形成されたか否かを確認できる半導体装置の製造方法を提供する。

【解決手段】 基板上に半導体膜の結晶化の際の起点となるべき起点部を複数形成する起点部形成工程において、基板の素子形成領域に、所定の大きさ(孔径0.8μm)で所定の間隔(5μm)の複数の孔(凹部)123を形成し、テストパターン形成領域Bに、所定の大きさの複数の孔123と、所定の大きさとは異なる大きさの複数の孔123a(孔径0.7μm)、123b(孔径0.9μm)と、所定間隔とは異なる間隔(4μm、6μm)の複数の孔を形成し、かかる起点部(孔)からのシリコン結晶粒の成長により結晶成長の起点となる微細孔の良否を確認し、また、所望の大きさのシリコン結晶粒が形成されたか否かを確認する。

(もっと読む)

141 - 160 / 204

[ Back to top ]