Fターム[5F110PP36]の内容

Fターム[5F110PP36]に分類される特許

81 - 100 / 204

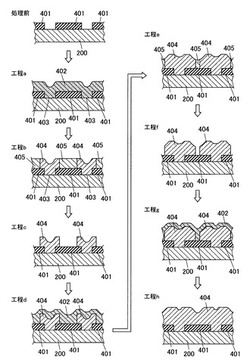

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

結晶核マスク、結晶核マスクの製造方法、多結晶シリコン層の製造方法、半導体装置、ならびに電気光学装置

【課題】結晶核形成を促進する触媒物質をα−Siに点状に付着させるための結晶核マスクを形成する場合に、単結晶シリコン基板を用いて、結晶面に沿って突起状の構造を形成し、その先端に触媒物質を付着させる工程を用いて製造した場合、直径30cm程度が限度の単結晶シリコン基板以上の面積を有する、α−Si層に、この転写用基板を用いて押圧転写することは困難であるという課題がある。

【解決手段】ガラス基板10上のα−Si層にエキシマレーザー光を照射して、規則的配列を備える突起部13を配置し、突起部13を覆うように触媒金属層を配置して結晶核マスク1を構成する。ガラス基板10は対角1m以上の基板が容易に入手できることから、大型(対角1m程度)の被転写基板21に対しても結晶核形成を促進する触媒物質をα−Siに点状に付着させることが可能となる。

(もっと読む)

半導体薄膜の製造方法、半導体薄膜、及び薄膜半導体装置

【課題】大きな結晶粒径の結晶粒径で、且つ、3次元的に結晶方位を制御された結晶粒で構成された半導体薄膜を製造し、この半導体薄膜を用いた半導体薄膜によって、優れたキャリア移動度を得る。

【解決手段】半導体薄膜の製造方法は、基板上に非晶質膜を形成する非晶質膜形成工程と、前記非晶質膜形成工程で形成した非晶質膜の少なくとも一部を結晶化させて、膜面に平行な特定の結晶面を持つ第1の多結晶膜を形成する第1結晶化工程と、前記第1結晶化工程で形成した第1の多結晶膜に1方向からイオン注入を行うことにより、3次元的に方位制御された所定の結晶方位を有する結晶粒を残す一方、それ以外の結晶粒を非晶質化させるイオン注入工程と、前記イオン注入工程で残った3次元的に方位制御された所定の結晶方位を有する結晶粒をシ−ドとして非晶質領域を結晶化させることにより第2の多結晶膜を形成する第2結晶化工程と、を備える。

(もっと読む)

膜製造方法

【課題】基板上に薄膜成長核を形成する場合に、大気圧環境下で、高温プロセスを排除し、かつスループットを低下させることなく、さらには薄膜成長核の無駄を発生させることなく容易に薄膜成長核を形成することにより膜製造設備のコストの低減及び膜製造コストの低減を図ることができる膜製造方法を提供する。

【解決手段】金属若しくは半導体を構成する元素、又はその元素からなるイオンを組成中に含む物質の溶液又は懸濁液を、基板上に塗布し、乾燥させた後、大気圧水素プラズマにて曝露処理することにより、基板上に薄膜を形成するための薄膜成長核を形成する。

(もっと読む)

レーザ結晶化装置、マスク、レーザ結晶化方法、結晶材、および半導体素子

【課題】粒内欠陥を抑制した高品質な結晶を得る。

【解決手段】投影マスク15は、第1スリットパターン15−1を介したレーザ光の照射によって、第1照射パターンを形成するためのブロックB1と、第2スリットパターン15−2を介した照射によって、第1照射パターンと平行であるとともに第1照射パターンの端部の一部を重畳する第2照射パターンを形成するためのブロックB2と、第3スリットパターン15−3を介した照射によって、第1照射パターンおよび第2照射パターンと直交する第3照射パターンを形成するためのブロックB3と、第4スリットパターン15−4を介した照射によって、第1照射パターンと平行である第4照射パターンを形成するためのブロックB4とを備え、第3レーザ光の照射により、第1照射パターンと第2照射パターンと第3照射パターンとの重畳領域に単結晶の種結晶領域を形成し、第4照射パターンが種結晶領域の一部と重畳する。

(もっと読む)

半導体装置の製造方法、トランジスタの製造方法ならびに電気光学装置の製造方法

【課題】結晶シリコン層を得る結晶化技術として、能動層の一部にNi,Co,Fe,Pd,Pt,Cu,Auの金属触媒を導入し、加熱処理を施して結晶化を行い、引き続きエキシマレーザ等によりエネルギーを与えることで種結晶を形成し、非晶質シリコン層領域を結晶化するという発明が提案されているが、この技術を用いた場合、種結晶の面配向を制御することができないという課題がある。

【解決手段】アルミニウム層102上に非晶質シリコン層103を堆積した後、アニールを行うことで層転換を行わせる。同時に非晶質シリコン層103は(111)配向を有する多結晶シリコン層104に変換される。多結晶シリコン層104をパターニングし種結晶として用いて、積層された非晶質シリコン層105をレーザアニールにより結晶化し、結晶シリコン層12を有する半導体装置108の製造方法を提供することが可能となる。

(もっと読む)

薄膜トランジスタ

【課題】本発明は、結晶化触媒の均一な低濃度拡散制御で金属触媒から形成されるシードの位置を調整して多結晶シリコーン層内のチャネル領域を単結晶に近いように形成することによって薄膜トランジスタの素子特性を向上させて均一な値を得ることができる薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタは基板上に形成された金属触媒層、金属触媒層上に次々と形成された第1キャッピング層及び第2キャッピング層パターンを含む。製造方法は金属触媒層上に第1キャッピング層を形成する。第1キャッピング層上に第2キャッピング層を形成してパターニングする。パターニングされた第2キャッピング層上に非晶質シリコーン層を形成する。金属触媒を拡散させる。非晶質シリコーン層を結晶化して多結晶シリコーン層を形成する段階を含む。

(もっと読む)

マスク、レーザ結晶化装置、レーザ結晶化方法、結晶材、および半導体素子

【課題】従来よりも大きな角型結晶を得る。

【解決手段】マスクには、レーザ光の照射によって略閉ループの結晶粒界に包囲された種結晶が形成するように種結晶形成用マスク要素群のスリットが配置され、種結晶中の特定位置を原点とするX−Y直交座標系について、kを1から4の自然数とし、第k象限におけるX軸正方向をkX+、X軸負方向をkX−、Y軸正方向をkY+、Y軸負方向をkY−とすると、種結晶形成用マスク要素群に続く種結晶伸張用マスク要素群を介して照射されるレーザ光の照射タイミングの制御と当該マスクの相対的な移動の制御とにより、略閉ループの結晶粒界に包囲された種結晶が、1X+、1Y+、2X−、2Y+、3X−、3Y−、4X+、および4Y−の各方向に伸張するように、種結晶伸張用マスク要素群のスリットが配置される。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】オン電流が高くオフ電流が低い薄膜トランジスタを提供する。

【解決手段】絶縁表面を有する基板上に、ゲート電極を覆うゲート絶縁層と、該ゲート絶縁層に接し、非晶質構造の中に複数の結晶領域を含みチャネル形成領域を構成する半導体層と、ソース領域及びドレイン領域を形成する一導電型を付与する不純物半導体層と、該半導体層と該一導電型を付与する不純物半導体層との間の非晶質半導体により構成されるバッファ層とを有し、前記結晶化領域は、前記ゲート絶縁層と前記半導体層との界面から離れた位置から、前記半導体層が堆積される方向に向けて、前記一導電型を付与する不純物半導体層に達しない領域内において略放射状に成長した逆錐形状の構造を有する薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】オン電流が高い薄膜トランジスタを提供する。

【解決手段】絶縁表面を有する基板上に、ゲート電極を覆うゲート絶縁層と、該ゲート絶縁層に接し、非晶質構造の中に複数の結晶領域を含みチャネル形成領域を構成する半導体層と、ソース領域及びドレイン領域を形成する一導電型を付与する不純物を含む半導体層と、を有し、前記結晶化領域は、前記ゲート絶縁層と前記半導体層との界面から離れた位置から、前記半導体層が堆積される方向に向けて、前記一導電型を付与する不純物を含む半導体層に達しない領域内において略放射状に成長した逆錐形状の構造を有する薄膜トランジスタとする。

(もっと読む)

光照射装置、結晶化装置、結晶化方法、およびデバイス

【課題】 例えばTFTの作製に適用した場合に、TFTの移動度の向上およびTFT間の移動度の均一化を実現することのできる結晶化装置。

【解決手段】 光を位相変調する光変調素子(1)と、光変調素子により位相変調された光に基づいて、長辺同士が隣接する短冊状の繰返し領域に所定の光強度分布を形成する結像光学系(3)と、非単結晶半導体膜を保持するステージ(5)とを備え、非単結晶半導体膜に所定の光強度分布を有する光を照射して結晶化半導体膜を生成する。所定の光強度分布は、短冊状の繰返し領域の短辺方向の中心線に沿って下に凸で且つ短冊状の繰返し領域の長辺方向の中心線に沿って下に凸の分布を有する。短冊状の繰返し領域の中心から長辺方向の外側に向けて凸状に湾曲した等強度線を有し、該凸状に湾曲した等強度線のうち少なくとも1本の先端部の曲率半径は0.3μm以下である。短冊状の繰返し領域の短辺方向のピッチは2μm以下である。

(もっと読む)

半導体基板、半導体基板の製造方法、トランジスタ、並びに電気光学装置

【課題】多結晶シリコンを(111)配向を選択的に形成する場合、結晶粒界の位置はランダムに形成されるため、トランジスタのチャネル部分に結晶粒が配置された場合、結晶粒界に存在するトラップ準位の影響により、電気的特性が低下する。また、多結晶領域を形成する単結晶群の大きさは0.5μm程度であり、トランジスタを形成した場合複数の結晶粒界がチャネルに配置されてしまい、同様に電気的特性が低下するという課題がある。

【解決手段】(111)配向を含む第1シリコン層204上に貫通孔206を含む絶縁層205を形成した後、第2シリコン層前駆体207aを積層し、XeClエキシマレーザを用いて第1シリコン層204を種結晶として再結晶工程を行う。これにより、面方位が(111)に揃えられ、且つ10μm程度の大粒径単結晶が得られる。この結晶上にトランジスタを形成することで、電気的特性に優れたトランジスタを提供できる。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

薄膜トランジスタ、その製造方法、並びに、それを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法、並びに、それを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、チャネル領域、ソース/ドレイン領域及びボディコンタクト領域を含む半導体層と、前記半導体層上に位置し、前記ボディコンタクト領域を露出させたゲート絶縁膜と、前記ゲート絶縁膜上に位置し、前記ゲート絶縁膜により露出された前記ボディコンタクト領域と接しているシリコン膜と、前記シリコン膜上に位置しているゲート電極と、前記ゲート電極上に位置している層間絶縁膜と、前記層間絶縁膜上に位置し、前記ソース/ドレイン領域と電気的に接続されたソース/ドレイン電極とを含み、前記ボディコンタクト領域は前記半導体層のエッジ領域内に形成されたことを特徴とする薄膜トランジスタ、その製造方法、並びに、それを含む有機電界発光表示装置に関する。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】化合物半導体デバイスのスイッチング速度等の性能を向上する。

【解決手段】シリコン基板と、シリコン基板の上に形成された絶縁膜であってシリコン基板に達する開口部を有する絶縁膜と、開口部に形成されたGe結晶と、Ge結晶を核として成長された化合物半導体結晶であって絶縁膜の表面より凸に形成されたシード化合物半導体結晶と、シード化合物半導体結晶の特定面をシード面として、絶縁膜の上にラテラル成長されたラテラル成長化合物半導体層と、を備えた半導体基板を提供する。

(もっと読む)

レーザ加工方法及び半導体装置

【課題】 帯状の絶縁パターンの中央近傍に結晶粒界が発生することを防止することが可能なレーザ加工方法を提供する。

【解決手段】 単結晶半導体基板と、その半導体基板よりも熱伝導率の低い材料からなり、相互に平行に配置されて前記半導体基板まで達する複数の溝が形成されている第1の膜と、アモルファスまたはマイクロクリスタルの半導体からなり、溝内及び第1の膜の上に配置されている第2の膜とを有する加工対象物を準備する。第2の膜に、第2の膜の表面において溝の長手方向と平行な長尺ビームであるパルスレーザビームを入射させ、パルスレーザビームの入射位置を、第2の膜の表面において、溝の長手方向と交差する方向に、オーバラップさせながら移動させる。第2の膜の表面におけるパルスレーザビームのビームプロファイルの短軸方向の幅が、相互に隣り合う溝の間隔よりも狭い。

(もっと読む)

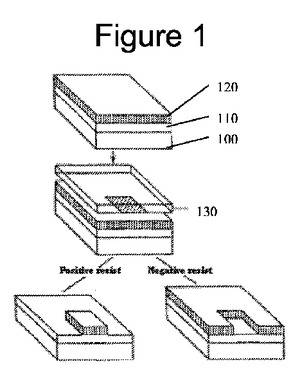

均一な結晶シリコン薄膜を製造するリソグラフィ方法

位置が制御される結晶粒の領域を備える結晶半導体膜と、位置が制御される結晶粒の位置を基準として規定される位置にある結晶半導体膜の中に位置するデバイスとを含む、結晶膜の中の既知の位置に位置付けられる電子デバイスに関係する方法および装置が説明される。この方法は、各照射ステップが、膜のリソグラフィで画成される領域を少なくとも部分的に融解させ、横方向に結晶化させ、横方向成長長さに垂直である少なくとも1つの長い粒子境界を有する横方向に成長した結晶粒の領域を得る、3つ以上の重複する照射ステップを使用して半導体膜の少なくとも一部を照射することと、少なくとも1つの長い粒子境界の位置を識別することと、長い粒子境界の位置を基準にして規定される位置にある半導体膜の中に電子デバイスを製造することとを含む。  (もっと読む)

(もっと読む)

シリコンの結晶化方法、接合体、半導体装置の製造方法および半導体装置

【課題】比較的低温下で、結晶粒や成長方向の制御を確実に行うことができ、これにより半導体特性に優れたポリシリコン層を効率よく形成可能なシリコンの結晶化方法、熱処理を施すことにより良好な結晶化がなされる非晶質部を備える接合体、前記結晶化方法により形成された半導体部を備える半導体装置を製造する方法、および、この方法により製造された半導体装置を提供すること。

【解決手段】本発明のシリコンの結晶化方法は、a−Si膜30a(非晶質部)と、c−Siの種結晶30cとを用意する工程と、a−Si膜30aの表面と種結晶30cの表面に、それぞれエネルギーを付与する工程と、a−Si膜30aと種結晶30cとを接合し接合体305を得る工程と、接合体305を加熱することにより、a−Si膜30aを結晶化する工程とを有する。これにより、a−Si膜30aと種結晶30cとの接合界面が成長核となって結晶化が進行する。

(もっと読む)

81 - 100 / 204

[ Back to top ]