Fターム[5F110PP36]の内容

Fターム[5F110PP36]に分類される特許

61 - 80 / 204

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードである。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれる電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かって成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置である。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】駆動回路及び画素部を有し、駆動回路は、デュアルゲート型の薄膜トランジスタを用いて構成され、画素部はシングルゲート型の薄膜トランジスタを用いて構成される表示装置である。該表示装置おけるデュアルゲート型の薄膜トランジスタは、半導体層が微結晶半導体領域及び一対の非晶質半導体領域で形成され、ゲート絶縁層及び絶縁層が半導体層の微結晶半導体領域に接する。

(もっと読む)

積層酸化物材料、半導体装置、および半導体装置の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向かって結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の同軸(アキシャル)成長をさせていることである。

(もっと読む)

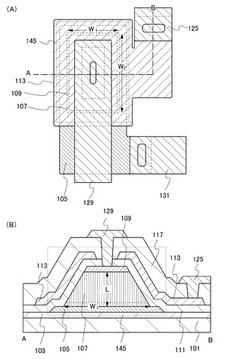

薄膜トランジスタおよびその製造方法

【課題】チャネル抵抗の増大を回避させた薄膜トランジスタの提供。

【解決手段】ボトムゲート型の薄膜トランジスタであって、ゲート絶縁膜上にゲート電極の形成領域に開口を有する層間絶縁膜が形勢され、半導体膜は前記開口を被って層間絶縁膜上に形成され、

前記層間絶縁膜は前記ゲート絶縁膜よりも窒化物を多く含み、前記半導体膜は、前記ゲート絶縁膜および前記層間絶縁膜面に形成された少なくともGeを含む半導体結晶核上に形成された微結晶半導体膜あるいは多結晶半導体膜によって構成されている。

(もっと読む)

多結晶シリコン層の製造方法、薄膜トランジスタ、それを含む有機電界発光表示装置及びその製造方法

【課題】多結晶シリコン層の製造方法、薄膜トランジスタ、それを含む有機電界発光表示装置及びその製造方法を提供する。

【解決手段】本発明は、基板100を提供する工程と、上記基板100上にバッファ層110を形成する工程と、上記バッファ層110上に金属触媒層115を形成する工程と、上記金属触媒層115の金属触媒をバッファ層110に拡散する工程と、上記金属触媒層115を除去する工程と、上記バッファ層110上に非晶質シリコン層120Aを形成する工程と、上記基板100を熱処理して上記非晶質シリコン層120Aを多結晶シリコン層に結晶化する工程とを含むことを特徴とする多結晶シリコン層の製造方法に関する。

(もっと読む)

結晶性半導体薄膜の製造方法

【課題】非晶質の絶縁層上に任意の位置に単結晶半導体層を成長させることにより高性能半導体素子の積層化あるいは3次元化を可能にし,高機能な半導体集積システムを実現する。

【解決手段】絶縁層上に非晶質半導体薄膜を堆積し,第1のイオン注入のチャネリングと熱処理により多結晶化させ,しかる後に,前記第1のイオン注入とは異なる方向から第2のイオン注入のチャネリングと熱処理による結晶化を行い、2つの結晶方位を規制した単結晶の半導体薄膜を成長する。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、表層にシリコン膜14を有する基板11上のシリコン膜14を一部覆う位置にマスク15aを形成する工程と、マスク15aが形成されていない領域のシリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

パターン形成方法、薄膜トランジスタ及びその作製方法

【課題】フォトリソグラフィ法に用いるフォトマスクの枚数を少なくする。

【解決手段】第1の膜を形成し、該第1の膜上にフォトリソグラフィ法により第1のレジストマスクを形成し、第1のレジストマスクを用いて所定のパターンを有する第1の層を形成し、第1のレジストマスクを除去し、第2の膜を形成し、該第2の膜上にフォトリソグラフィ法により第1のレジストマスクと同一のフォトマスクにより第2のレジストマスクを形成し、該第2のレジストマスクを縮小して第3のレジストマスクを形成し、第3のレジストマスクを用いて所定のパターンを有する第2の層を形成する。

(もっと読む)

半導体素子基板の製造方法及び半導体素子基板並びに表示装置

【課題】同一基板上に、結晶粒の平均粒径が互いに異なり、各々優れたキャリア移動度を有する2種類の結晶質半導体膜を形成し、それら2種類の結晶質半導体膜を用いて異なる電気特性が要求される各半導体素子に所望の電気特性を得る。

【解決手段】基板11上に非晶質半導体膜24を成膜する非晶質膜成膜工程と、非晶質半導体膜24の一部を溶融固化して結晶化することで第1結晶質半導体膜24Aを形成する第1結晶化工程と、残部の非晶質半導体膜24を固相成長させることで第1結晶質半導体膜24Aよりも結晶粒の平均粒径が大きい第2結晶質半導体膜24Bを形成する第2結晶化工程と、第1結晶質半導体膜24Aの結晶粒の平均粒径が第2結晶質半導体膜24Bの結晶粒の平均粒径よりも小さい状態を維持しながら第1及び第2結晶質半導体膜24Bを溶融固化することで再結晶化する再結晶化工程とを含む。

(もっと読む)

半導体装置の作製方法

【課題】大面積な半導体装置を低コストに提供することを目的の一とする。または、nチャネル型トランジスタ及びpチャネル型トランジスタに最適な結晶面をチャネル形成領域とすることにより、性能向上を図ることを目的の一とする。

【解決手段】絶縁表面上に(211)面から±10°以内の面を上面とする島状の単結晶半導体層を形成し、単結晶半導体層の上面及び側面に接して形成し、且つ絶縁表面上に非単結晶半導体層を形成し、非単結晶半導体層にレーザー光を照射して非単結晶半導体層を溶融し、且つ、単結晶半導体層を種結晶として絶縁表面上に形成された非単結晶半導体層を結晶化して結晶性半導体層を形成し、結晶性半導体層を用いて、nチャネル型トランジスタ及びpチャネル型トランジスタを形成する。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】動作初期における劣化が生じにくい薄膜トランジスタとその作製方法を提供する。

【解決手段】少なくとも最表面が窒化シリコン層であるゲート絶縁層と、前記ゲート絶縁層上に設けられた半導体層と、前記半導体層上にバッファ層を有し、該半導体層中のゲート絶縁層との界面近傍における窒素の濃度は、半導体層の他の部分及びバッファ層よりも低い薄膜トランジスタを作製する。このような薄膜トランジスタは、半導体層の形成前にゲート絶縁層を大気雰囲気に曝露し、プラズマ処理を行うことで作製することができる。

(もっと読む)

結晶性半導体薄膜の製造方法

【課題】非晶質の絶縁層上に任意の位置に単結晶半導体層を成長させることにより高性能半導体素子の積層化あるいは3次元化を可能にし、高機能な半導体集積システムを実現する。

【解決手段】絶縁層上に非晶質半導体薄膜を堆積し、その一部に単結晶半導体層を接触させ、熱処理によって単結晶半導体層の結晶性を反映させ非晶質半導体薄膜を単結晶化する半導体薄膜の結晶化方法。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

半導体装置の製造方法、半導体装置、および電気光学装置

【課題】単結晶シリコン層を貼り付けた高価な基板や、触媒金属を拡散させたシリコン膜を用いなくても、トランジスター特性の優れた薄膜トランジスターを備えた半導体装置の製造方法、半導体装置、および電気光学装置を提供すること。

【解決手段】半導体装置の製造工程では、非晶質のシリコン膜1の一部の領域にゲルマニウムを導入して熱処理を行う。その結果、核形成用元素導入領域1sに結晶核が生成するとともに、かかる結晶核を起点として結晶粒が成長する。このため、シリコン結晶粒の位置制御が可能となり、チャネル領域1hに含まれる粒界の量を制御することができる。また、ゲルマニウムは、チャネル領域形成予定領域1iやその周辺の領域1k、1mなどに拡散しない。

(もっと読む)

表示装置

【課題】表示装置の作製のコストの低減を課題の一とする。

【解決手段】複数のインバータ回路及び複数のスイッチを有し、インバータ回路は、ゲート端子及び第1端子が高電源電位を供給する配線に接続された第1の薄膜トランジスタと、第1の薄膜トランジスタの第2端子が第1端子に接続され、第2端子が低電源電位を供給する配線に接続され、ゲート端子に入力信号が供給される第2のトランジスタと、を有し、第1の薄膜トランジスタ及び第2の薄膜トランジスタは同じ極性であり、第1の薄膜トランジスタ及び第2の薄膜トランジスタは、ゲート電極に接するゲート絶縁層と、ゲート絶縁層に接する微結晶半導体層と、微結晶半導体層に接する混合層と、混合層に接する非晶質半導体を含む層と、配線とを有し、混合層において、錐形状の微結晶半導体領域と、錐形状の微結晶半導体領域を充填する非晶質半導体領域とを有する表示装置である。

(もっと読む)

薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機電界発光表示装置を提供する。

【解決手段】基板と、前記基板上に位置するバッファ層と、前記バッファ層上に位置する第1半導体層及び第2半導体層と、前記第1半導体層及び第2半導体層と絶縁されるゲート電極と、前記第1半導体層及び第2半導体層と前記ゲート電極とを絶縁するゲート絶縁膜と、前記ゲート電極と絶縁され、前記第2半導体層と一部が接続するソース/ドレインである電極とを含み、前記第1半導体層は前記第2半導体層の下部に位置し、前記第1半導体層の面積は第2半導体層の面積よりも小さいことを特徴とする薄膜トランジスタ及びその製造方法に関する。また、前記薄膜トランジスタを含む有機電界発光表示装置とその製造方法に関する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

61 - 80 / 204

[ Back to top ]