Fターム[5F110PP36]の内容

Fターム[5F110PP36]に分類される特許

41 - 60 / 204

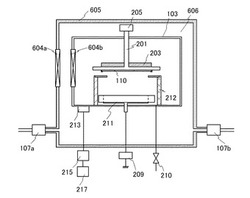

成膜装置、及び半導体装置の作製方法

【課題】不純物が混入しない酸化物半導体膜を成膜する成膜装置を提供することを課題とする。不純物が混入しない酸化物半導体膜を含む半導体装置の作製方法を提供することを課題とする。

【解決手段】成膜装置を含む環境から不純物を排除することにより、成膜装置の外部から成膜装置内へ不純物を含む気体が漏洩(リーク)する現象を防げばよい。また、当該装置を用いて成膜した、不純物が低減された酸化物半導体層を半導体装置に適用すればよい。

(もっと読む)

薄膜トランジスタ、その製造方法、及びこれを含む表示装置

【課題】不完全結晶成長領域を含まない多結晶シリコンでゲート電極または遮光部材のような金属パターン上に位置する半導体層を形成することにより、駆動特性及び信頼性を向上させる薄膜トランジスタ、その製造方法、及びこれを含む表示装置を提供する。

【解決手段】多結晶シリコンで形成された半導体層142を含む薄膜トランジスタにおいて、前記半導体層と基板110との間に前記半導体層と絶縁するように位置する金属パターンをさらに含み、前記半導体層の多結晶シリコンは、結晶成長方向と平行な結晶粒界を含み、表面における波状線の最大ピークと最小ピークとの間の距離として定義される表面粗度が15nm以下である。

(もっと読む)

多結晶シリコン層とその製造方法、該多結晶シリコン層を利用した薄膜トランジスタ及び該薄膜トランジスタを備えた有機発光表示装置

【課題】多結晶シリコン層、その製造方法、多結晶シリコン層を利用した薄膜トランジスタ及び薄膜トランジスタを備えた有機発光表示装置を提供する。

【解決手段】基板10上のバッファ層11上に非晶質シリコン層12を形成する工程と、非晶質シリコン層12上に触媒金属層を1011ないし1015原子/cm2の密度を有するように形成する工程と、触媒金属層の触媒金属が非晶質シリコン層12に拡散して非晶質シリコン層12とバッファ層11との界面でピラミッド形態の結晶化シードを形成し、結晶化シードによってシリコン結晶が成長して多結晶シリコン層22を形成するように、非晶質シリコン層12を熱処理する工程と、を含むシリコン層の結晶化方法である。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタのアクティブ層の製造方法、および表示装置

【課題】金属触媒の拡散を利用してシリコン層を多結晶半導体層に形成しても、金属触媒の濃度差によって多結晶半導体層の半導体特性が低下することを最少化する薄膜トランジスタ、薄膜トランジスタのアクティブ層の製造方法、および表示装置を提供する。

【解決手段】薄膜トランジスタは、基板上に位置する第1多結晶半導体層と、第1多結晶半導体層上に位置する第2多結晶半導体層と、第1多結晶半導体層と隣接して互いに所定の間隔で離隔している金属触媒とを含む。

(もっと読む)

酸化物半導体膜の作製方法、およびトランジスタの作製方法

【課題】結晶性の高い酸化物半導体膜の作製方法を提供することを課題の一とする。また、高い電界効果移動度を有するトランジスタの作製方法を提供することを課題の一とする。

【解決手段】基板上に酸素を意図的に含ませない雰囲気で酸化物半導体膜を形成し、酸素を含む雰囲気で熱処理をして、酸化物半導体膜を結晶化させる酸化物半導体膜の作製方法である。また、基板上に、ゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に酸素を意図的に含ませない雰囲気で酸化物半導体膜を形成し、酸素を含む雰囲気での第1の熱処理をして、酸化物半導体を結晶化させ、結晶化した酸化物半導体膜上にソース電極およびドレイン電極を形成し、結晶化した酸化物半導体膜、ソース電極およびドレイン電極上に酸素原子を含む絶縁膜を形成し、結晶化した酸化物半導体膜を第2の熱処理により酸化させるトランジスタの作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】成膜中に水素原子を含む不純物と強く結合する物質を成膜室に導入して、成膜室に残留する水素原子を含む不純物と反応せしめ、水素原子を含む安定な物質に変性することで、高純度化された酸化物半導体層を形成する。水素原子を含む安定な物質は酸化物半導体層の金属原子に水素原子を与えることなく排気されるため、水素原子等が酸化物半導体層に取り込まれる現象を防止できる。水素原子を含む不純物と強く結合する物質としては、例えばハロゲン元素を含む物質が好ましい。

(もっと読む)

半導体装置およびその作製方法

【課題】表示された画像が良好に認識できる表示装置を提供することを課題の一とする。また、その表示装置を生産性良く作製する方法を提供することを課題の一とする。

【解決手段】基板上に液晶層を介して入射する光を反射する画素電極と、透光性を有する画素電極と、透光性を有する画素電極と重なる位置に側面が反射層で覆われた構造体を設ける。構造体は、透光性を有するエッチングストップ層上に形成され、エッチングストップ層は、構造体の下に透光層として残存する。

(もっと読む)

半導体装置およびその作製方法

【課題】微小化されたトランジスタはゲート絶縁層の薄膜化を要求されるが、トンネル電流、つまりゲートリーク電流の増加により、ゲート絶縁層が酸化珪素膜の単層である場合はゲート絶縁層の薄膜化には物理的限界が生じつつある。

【解決手段】ゲート絶縁層に比誘電率が10以上のhigh−k膜を用いることで、微小化したトランジスタのゲートリーク電流を低減させる。酸化物半導体層と接する第2の絶縁層よりも比誘電率が高い第1の絶縁層としてhigh−k膜を用いることによって、酸化珪素膜で換算した場合のゲート絶縁層よりもゲート絶縁層の薄膜化ができる。

(もっと読む)

半導体装置の製造方法

【課題】格子定数が異なる複数種類の半導体素子やスピン機能素子を同一の基板上の同一の層上に混載することが可能な半導体装置の製造方法を提供しようとする。

【解決手段】シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜に開口部を設け、前記シリコン基板の一部を露出させる工程と、前記露出したシリコン基板及び前記絶縁膜上にGeを含むアモルファスの第1の半導体層を形成する工程と、前記第1の半導体層を第1の方向に延伸した構造に加工する工程と、前記第1の方向に延伸した第1の半導体層に熱処理を加えて、前記開口部から離れるにしたがってSiの濃度が減少する第1のSi1-xGex(0≦x≦1)層を形成する工程と、を含む。

(もっと読む)

表示装置とその作製方法

【課題】安定した電気的特性(例えば、オフ電流がきわめて低減されている)を有するトランジスタで構成される表示装置を提供することを目的とする。

【解決手段】トランジスタを形成するための半導体材料としてシリコン半導体よりも禁制帯幅(バンドギャップ)の広い半導体材料を用い、好ましくは、かかる半導体材料のキャリア供与体となる不純物の濃度を低減することでオフ電流の低減を図る。そのために、トランジスタの半導体層(チャネル領域を形成する層)としてエネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上の酸化物半導体を用い、該酸化物半導体に含まれるキャリア供与体となる不純物の濃度を低減させている。それにより、トランジスタのオフ電流を、室温にてチャネル幅1μm当たり10zA/μm未満、85℃にて100zA/μm未満と極めて低いレベルにまで低減させることを可能とする。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、結晶性の優れた酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図る。

【解決手段】基板上に第1の多元系酸化物半導体層を形成し、第1の多元系酸化物半導体層上に一元系酸化物半導体層を形成し、500℃以上1000℃以下、好ましくは550℃以上750℃以下の加熱処理を行って表面から内部に向かって結晶成長させ、第1の単結晶領域を有する多元系酸化物半導体層、及び単結晶領域を有する一元系酸化物半導体層を形成し、単結晶領域を有する一元系酸化物半導体層上に第2の単結晶領域を有する多元系酸化物半導体層を積層する。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のソース電極および第1のドレイン電極と、第1のソース電極および第1のドレイン電極と電気的に接続され、酸化物半導体材料が用いられている第1のチャネル形成領域と、第1のチャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、を有する第1のトランジスタと、容量素子と、を有し、第1のトランジスタの第1のソース電極または第1のドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続された半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、結晶性の優れた酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図る。

【解決手段】基板上に一元系酸化物半導体層を形成し、500℃以上1000℃以下、好ましくは550℃以上750℃以下の加熱処理を行って表面から内部に向かって結晶成長させ、単結晶領域を有する一元系酸化物半導体層を形成し、単結晶領域を有する一元系酸化物半導体層上に単結晶領域を有する多元系酸化物半導体層を積層する。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の駆動能力の向上を図ることを課題の一とする。

【解決手段】半導体装置は、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタの第1の端子は、第1の配線と電気的に接続され、第1のトランジスタの第2の端子は、第2の配線と電気的に接続され、第2のトランジスタのゲートは、第3の配線と電気的に接続され、第2のトランジスタの第1の端子は、第3の配線と電気的に接続され、第2のトランジスタの第2の端子は、第1のトランジスタのゲートと電気的に接続され、第1のトランジスタ及び第2のトランジスタは、酸化物半導体によりチャネル領域が形成され、第1のトランジスタ及び第2のトランジスタのチャネル幅が1μmあたりのオフ電流が1aA以下である。

(もっと読む)

半導体装置

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングトランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチングトランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半導体装置である。

(もっと読む)

表示装置およびそれを用いた電子機器

【課題】本発明の一態様は、酸化物半導体において高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面から内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化物材料を用いて高移動度のトランジスタを形成し、それを用いて同一基板上にドライバ回路を形成する。

(もっと読む)

光変調素子、結晶化装置、結晶化方法、薄膜半導体基板の製造装置、薄膜半導体基板の製造方法、薄膜半導体装置、薄膜半導体装置の製造方法および表示装置

【課題】半導体膜から粒径の大きな結晶相の半導体を得る工程において、以降の工程で、アライメントマークとして利用可能なマーク構造を、同一の露光工程において半導体膜に形成する。

【解決手段】この発明は、光を変調して結晶化のための光強度分布を形成する光強度変調構造SPと、光強度変調構造と一体にまたは独立に設けられ、光を変調して所定形状のパターンを含む光強度分布を形成するとともに結晶化領域の予め定められた位置を示すマーク形成構造MKと、を有することを特徴とする光変調素子3に関する。この光変調素子によれば、絶縁基板上に所定厚さに堆積された半導体膜の任意の位置に、結晶核を形成し、その結晶核から所定の方向に結晶を成長させるとともに、半導体膜の任意の位置にアライメントマークAMを、同一工程で形成できる。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】駆動回路及び画素部を有し、駆動回路は、デュアルゲート型の薄膜トランジスタを用いて構成され、画素部はシングルゲート型の薄膜トランジスタを用いて構成される表示装置である。該表示装置おけるデュアルゲート型の薄膜トランジスタは、半導体層が微結晶半導体領域及び一対の非晶質半導体領域で形成され、ゲート絶縁層及び絶縁層が半導体層の微結晶半導体領域に接する。

(もっと読む)

41 - 60 / 204

[ Back to top ]