Fターム[5F110PP36]の内容

Fターム[5F110PP36]に分類される特許

161 - 180 / 204

半導体装置の製造方法、半導体装置、電気光学装置及び電子機器

【課題】 半導体デバイスの3次元形成において、特性バラツキの小さな高性能薄膜トランジスタを得ることを可能とする半導体装置の製造方法を提供する。

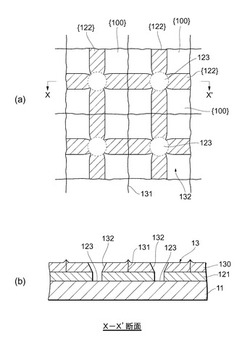

【解決手段】 少なくとも一方の表面が単結晶性または略単結晶性を有する基板(11)上に半導体膜の結晶化の際の起点となる凹部(123)を形成する凹部形成工程と、前記凹部が形成された前記基板上に半導体膜(130)を形成する半導体膜形成工程と、前記半導体膜に熱処理を行い、前記起点部を略中心とする略単結晶粒(13)を形成する熱処理工程と、前記半導体膜をパターニングし、ソース領域、ドレイン領域及びチャネル形成領域となるべきトランジスタ領域(133)を形成するパターニング工程と、前記トランジスタ領域上にゲート絶縁膜(14)及びゲート電極(15)を形成して薄膜トランジスタを形成する素子形成工程と、を含み、前記素子形成工程では、前記基板が有する単結晶または略単結晶の結晶面[111]以外の方向に薄膜トランジスタを形成する。

(もっと読む)

結晶質半導体膜およびその製造方法

【課題】 電気的特性が良好で、かつ、電気的特性のばらつきを抑制した結晶質半導体膜および前記結晶質半導体膜を容易に製造するための製造方法を提供する。

【解決手段】 本発明の結晶質半導体膜の製造方法は、多結晶半導体膜(120)を用意する工程と、多結晶半導体膜(120)の少なくとも一部の領域に所定の元素(130)を注入することにより、多結晶半導体膜(120)の結晶化率よりも低い結晶化率を有する非晶質化領域を多結晶半導体膜(120)の少なくとも一部の領域に形成する工程であって、所定のエネルギービーム(150)に対する非晶質化領域の吸収率が所定の方向に沿って連続的に変化するように所定の元素(130)を注入する、工程と、非晶質化領域に所定のエネルギービーム(150)を照射することにより、非晶質化領域を結晶化する工程とを包含する。

(もっと読む)

亜鉛酸化物をベースとした半導体材料を含む薄膜トランジスタ

薄膜トランジスタは、亜鉛酸化物含有半導体材料を含んでいる。このトランジスタはさらに、この材料と接触していて互いに離れた第1の接点手段または電極と第2の接点手段または電極を備えている。さらに、製造中に基板の温度が300℃を超えない薄膜トランジスタ・デバイスの製造方法も開示されている。  (もっと読む)

(もっと読む)

半導体薄膜の製造方法、電子デバイス及び液晶表示デバイス

【課題】 基板面内の結晶粒の位置や結晶粒径を容易に制御することができる半導体薄膜の製造方法を提供する。

【解決手段】 半導体薄膜の製造方法において、第1の透明基板2上に第1の下地層31を形成する工程と、第1の下地層31の表面に凸部33及び凹部34を形成する工程と、第1の下地層31に対して熱伝導率が異なり、凸部33及び凹部34を覆い、表面が平坦な第2の下地層32を第1の下地層31の表面上に形成する工程と、第2の下地層32の表面上に半導体薄膜を形成する工程と、半導体薄膜にエネルギビームを照射し、凸部33又は凹部34に対応する第1の下地層31及びの第2の下地層32の一部を結晶生成核35として、半導体薄膜(510)を結晶化する工程とを備える。

(もっと読む)

ナノワイヤ・チャネルおよびシリサイド化下部コンタクトを有する垂直型FET

【課題】 下部コンタクトに対するアクセス抵抗を低減させ、ゲート長が制御された、ナノワイヤ・チャネルを含む垂直型FETを提供する。

【解決手段】 FETチャネルを形成するナノワイヤを有する垂直型FET構造を開示する。ナノワイヤを、導電性シリサイド層の上に形成する。ナノワイヤは、周囲のゲートによって制御される。上部および下部の絶縁プラグがゲート・スペーサとして機能し、ゲート−ソースおよびゲート−ドレイン静電容量を低減させる。

(もっと読む)

半導体装置、電気光学装置、電子デバイス、及び半導体装置の製造方法

【課題】大粒径の略単結晶粒に半導体装置のチャネル形成領域がアライメント精度良く形成されている半導体装置、それを用いた電気光学装置と電子デバイス、及び半導体装置の製造方法を提供することを目的とする。

【解決手段】基板20上に第一アライメント・マーク21を形成する。結晶成長の起点となるグレイン・フィルタ26の位置は、第一アライメント・マーク21を基準に決定する。グレイン・フィルタ26上に半導体膜を形成し、その後半導体膜を結晶化して略単結晶半導体膜を形成する。略単結晶半導体膜をパターニングする際には、第一アライメント・マーク21の位置を基準とする。

(もっと読む)

半導体装置の製造方法

【課題】高性能な半導体装置を容易に製造することができる製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、実質的に非晶質シリコンからなる第1非晶質シリコン層と、第1非晶質シリコン層の結晶化を促進するための触媒を含み、第1非晶質シリコン層に積層された触媒層とを有する積層を形成する工程S1と、第1非晶質シリコン層を触媒を用いて結晶化させることにより第1結晶化シリコン層を形成する第1結晶化工程S2と、第1結晶化シリコン層の上に、実質的に非晶質シリコンからなる第2非晶質シリコン層を形成する工程S4と、第2非晶質シリコン層を結晶化させることにより第2結晶化シリコン層を形成する第2結晶化工程S5とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 良好な電気的特性のトランジスタが得られるようにし、これによって半導体装置の微細化や高密度化を可能にし、さらには3次元に積み重ねることをも可能にした、半導体装置の製造方法とこの製造方法によって得られる半導体装置を提供する。

【解決手段】 基体1上に形成された結晶性半導体膜3のうち第1の部分以外の少なくとも第2の部分及び第3の部分に不純物を注入する第1の工程と、第2の部分および第3の部分にそれぞれソース及びドレインを形成する第2の工程とを備える。第2の工程において、少なくとも第2の部分および第3の部分に対して加熱処理を施すことにより、第1の部分の少なくとも一部をシードとする第2の部分及び第3の部分の固相エピタキシー過程を誘起する。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 単結晶半導体層の結晶品質を向上させつつ、単結晶半導体層を絶縁体上に安価に形成する。

【解決手段】 選択エピタキシャル成長を行うことにより、非晶質半導体層3と接触するように開口部5内に埋め込まれた単結晶半導体層6を形成した後、エッチングガスまたはエッチング液をシリコン酸化膜2、4に接触させることにより、シリコン酸化膜2、4をエッチング除去して、単結晶半導体基板1と非晶質半導体層3との間に空隙7を形成し、単結晶半導体層6を種として非晶質半導体層3の熱処理を行うことにより、非晶質半導体層3が単結晶化された単結晶化半導体層8を形成してから、単結晶半導体基板1と単結晶半導体層8との間の空隙7に埋め込み絶縁層9を形成する。

(もっと読む)

半導体装置の製造方法、集積回路、電気光学装置、及び電子機器

【課題】結晶方位が一定でない結晶性半導体膜表面に機械的化学的研磨を行った際、結晶性半導体膜を平坦化し、半導体装置の特性を向上させることを可能とする、半導体装置の製造方法、そしてこの製造方法により得られた集積回路、電気光学装置、及び電子機器を提供する。

【解決手段】面方位が2以上有る結晶性半導体膜20の表面を化学的機械的研磨により平坦化、及び薄膜化した後、平坦化結晶性半導体膜21を用いて半導体素子を形成する半導体装置の製造方法である。化学的機械的研磨における研磨液として、水素イオン濃度がPH9.0以下のアルカリ溶液を用いる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 チャネル幅を十分に大きくすることができ、これにより得られるトランジスタの能力向上を図った半導体装置の製造方法と、これによって得られる半導体装置とを提供する。

【解決手段】 単一の結晶粒(略単結晶粒42)に、ソース領域11及びドレイン領域12と、チャネル領域13とを有してなるトランジスタ10が少なくとも一つ形成されてなる半導体装置である。チャネル領域13は、略単結晶粒42がエッチングされて、フィン形状のチャネル部15を複数並列した状態に形成されてなる。各チャネル部15のそれぞれの表面部にはゲート絶縁膜16が設けられ、各チャネル部15のそれぞれのゲート絶縁膜16の一部を覆って、ゲート電極14が設けられている。

(もっと読む)

ポリシリコン薄膜トランジスタ基板の製造方法及び液晶表示装置

【課題】結晶化されたポリシリコンの結晶粒が突出して荒れた表面を平坦化して半導体層の電気的特性を向上させることができるポリシリコン薄膜トランジスタ基板の製造方法及びそれによって製造された薄膜トランジスタ基板を含む液晶表示装置を提供する。

【解決手段】ポリシリコン結晶粒が形成された基板をローディングする段階と、ポリシリコン結晶粒の間の結晶粒界で突出している結晶粒を化学的機械的研磨によって除去して研磨された基板を形成する段階と、研磨された基板を洗浄して洗浄された基板を形成する段階と、洗浄された基板をアンローディングする段階とを有する。

(もっと読む)

成膜方法、電子デバイス用基板、電子デバイスおよび電子機器

【課題】本発明の目的は、高い密着性および膜強度を有し、かつ優れた特性を発揮する無機酸化物膜を容易かつ安価に形成し得る成膜方法、この無機酸化物膜を備える電子デバイス用基板、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の成膜方法は、基板(基材)2上に無機酸化物粒子81aを堆積させて、無機酸化物粒子81aの集合物81を膜状に形成する第1の工程と、無機酸化物粒子81aを溶解し得る溶剤82aを集合物81に供給し、無機酸化物粒子81aの表面を溶解させ、無機酸化物粒子81aの溶解物で無機酸化物粒子81a同士の間を充填または無機酸化物粒子81aの表面を被覆する第2の工程と、溶解物を析出させた析出物82bで、集合物81を安定化する第3の工程とを有するものである。また、第3の工程の後、析出物82bを酸化物82cに変化させる処理を施す第4の工程を有するのが好ましい。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】 浅いソース,ドレイン接合位置を保ちつつ接合リークを低く抑えることができ

、且つコンタクト抵抗も低く保つ。

【解決手段】

SOI−MOSFETにおいて、絶縁膜102の上に形成され、チャネル領域を除いて

除去された第1のシリコン層103と、シリコン層103上にゲート絶縁膜200を介し

て形成されたゲート電極300と、シリコン層103のチャネル長方向の両側の絶縁膜1

02に設けられた溝の底面及び側面に形成され、側面の一部でシリコン層103に接する

ように形成された第2のシリコン層600と、第2のシリコン層600からなるソース,

ドレイン領域601,602上に形成されたシリサイド層631,632と、シリコン層

103と接するシリコン層600の側面部に位置するシリサイド層631,632に形成

された、AsとOを1019cm−3以上の濃度で含む拡散抑制領域とを備えた。

(もっと読む)

半導体装置及びその作成方法

【課題】MOSFETに匹敵する性能を有した半導体装置を提供する。

【解決手段】絶縁表面を有する基体上に非晶質珪素膜を成膜し、非晶質珪素膜上に選択的にマスク絶縁膜を形成して結晶化を助長する金属元素を導入させ、第1の加熱処理により非晶質珪素膜の少なくとも一部を結晶性珪素膜にし、マスク絶縁膜を除去し、パターニングすることにより島状の結晶性珪素膜を形成し、ハロゲン元素を含む雰囲気中において第2の加熱処理を行うことにより、島状の結晶性珪素膜中の金属元素をゲッタリング除去すると共に、ゲイト絶縁膜として用いる熱酸化膜を島状の結晶性珪素膜の表面に形成し、熱酸化膜上にゲイト電極を形成し、一導電性を付与する不純物イオンを注入して島状の結晶性珪素膜にソース領域、ドレイン領域を形成し、ソース領域及び前記ドレイン領域上面に金属膜を形成し、ソース領域とドレイン領域をシリサイド化することを特徴とする。

(もっと読む)

薄膜半導体装置の製造方法

【課題】 面方位が制御され、しかも単結晶の結晶構造を有し、これによって移動度等の電気的特性(半導体特性)に優れた薄膜半導体装置を製造し得る、方法を提供する。

【解決手段】 基板1上に下地膜2を形成する工程と、下地膜2上にシリコンの結晶化を促進する触媒金属3を点状に配する工程と、触媒金属3を覆って基板1上に非晶質シリコンを成膜するとともに、非晶質シリコン膜4と触媒金属3とを反応させて金属シリサイド5を形成する工程と、金属シリサイド5を形成した非晶質シリコン膜4を加熱して固相成長させ、固相成長粒6を形成する工程と、非晶質シリコン膜4を溶融・結晶化させることによって所定の面方位を有する単結晶シリコン粒7を、固相成長粒6を種結晶として形成する工程と、を含む薄膜半導体装置の製造方法。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタ基板、電子機器及び多結晶半導体薄膜の製造方法

低しきい電圧値、高キャリア移動度及び低リーク電流等の性能を簡単に実現できるTFT等を提供する。TFTは、小熱容量部と大熱容量部とを有する多結晶Si膜からなり、小熱容量部が少なくともチャネル部として用いられものである。そして、多結晶Si膜は、小熱容量部が完全溶融するとともに大熱容量部が完全溶融しないエネルギ密度のレーザアニールによる結晶粒膜によって形成されている。小熱容量部と大熱容量部との界面から成長した粗大結晶粒によってチャネル部が構成されるので、一般的なレーザアニール装置を用いて低しきい電圧値、高キャリア移動度及び低リーク電流等の性能を簡単に実現できる。  (もっと読む)

(もっと読む)

半導体装置および電子機器

【課題】優良な多結晶薄膜半導体装置を比較的低温で製造する。

【解決手段】多結晶半導体膜形成後、希ガス元素イオンを半導体膜に注入する。その後溶融結晶化を行う。

(もっと読む)

単結晶シリコン薄膜の形成方法及び薄膜トランジスタの形成方法

【課題】パターニングされた金属マスクと粒界フィルタ領域とを利用して大規模な単結晶シリコン薄膜を形成することにより、高品質の薄膜トランジスタチャンネル領域を形成する方法を提供する。

【解決手段】単結晶シリコン薄膜形成の形成方法は、非晶質シリコン層をパターニングし、結晶化が始まる第1シリコン領域41、第1シリコン領域41の一側中央に位置し、第1シリコン領域41より狭幅の細長い第2シリコン領域42、及び第2シリコン領域42と接して第2シリコン領域42より広幅の第3シリコン領域43を形成する工程と、第1シリコン領域41上に部分的に金属マスク34を形成する工程と、パターニングされた非晶質シリコン層にレーザビームを照射し、金属マスク34の下部にある非晶質シリコンを除外した残りの非晶質シリコン層を全体的に溶融させた後で冷却することによって結晶化する工程と、を含む。

(もっと読む)

結晶質半導体膜の製造方法、結晶質半導体膜、半導体装置および表示装置

【課題】 電気的特性が優れた大きな結晶粒を有する結晶質半導体膜の製造方法を提供する。

【解決手段】 本発明による結晶質半導体膜の製造方法は、結晶核形成部(2a)と、素子形成部(2b)と、狭小部(2c)とを含む半導体膜(2)が形成された基板(1)を用意する工程と、絶縁膜(3)を形成する工程と、絶縁膜(3)を用いてキャップ膜(3C)を形成する工程であって、結晶核形成部(2a)に対する所定の波長の光の反射率が、端部よりも中央において高くなるように、キャップ膜部分(3aC)の屈折率を変化させる工程と、所定の波長の光によって、キャップ膜部分(3aC)を介して結晶核形成部(2a)を照射して、結晶核形成部(2a)を結晶化する工程と、結晶核形成部(2a)において結晶化された結晶から、狭小部(2c)を介して素子形成部(2b)を結晶化する工程とを包含する。

(もっと読む)

161 - 180 / 204

[ Back to top ]