Fターム[5F110QQ02]の内容

Fターム[5F110QQ02]に分類される特許

61 - 80 / 934

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を不活性ガス雰囲気化で加熱し、その後、酸化物半導体膜を酸素雰囲気化で加熱する。本工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物半導体膜より意図的に排除し、酸化物半導体膜を高純度化することができる。不純物を排除する際、酸化物半導体を構成する主成分材料である酸素が欠損する場合があるが、酸素雰囲気化で加熱することによって、酸素を供給することができる。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信

頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】絶縁表面上において、ゲート絶縁膜を間に挟んでゲート電極上に酸化物半導

体膜を形成し、酸化物半導体膜上に、チタン、モリブデンまたはタングステンを含む第1

の導電膜を形成し、第1の導電膜上に、電気陰性度が水素より低い金属を含む第2の導電

膜を形成し、第1の導電膜及び第2の導電膜をエッチングすることでソース電極及びドレ

イン電極を形成し、酸化物半導体膜、ソース電極及びドレイン電極上に、酸化物半導体膜

と接する絶縁膜を形成する半導体装置の作製方法。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の

影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置

を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電

極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トラン

ジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を

用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼

性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジ

カルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中

の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の

変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

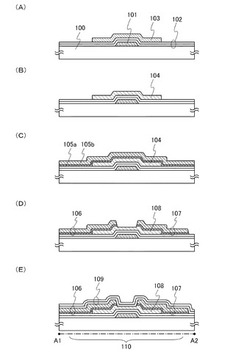

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】第1のトランジスタ及び第2のトランジスタを有するメモリセルを有し、第1のトランジスタは第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタは酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される不揮発性メモリによって解決する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。半導体装置に設けられる該薄膜トランジスタは多階調マスクによって形成されたレジストマスクを用いて作製する。

(もっと読む)

半導体装置、表示装置

【課題】グローバルシャッタ方式で電荷の蓄積を行うイメージセンサにおいて、蓄積期間

終了時から最後の行を読み出すまでの期間、蓄積電荷保持部からの電荷の流出を極力抑制

することのできる半導体装置の提供を目的とする。

【解決手段】画素がマトリクス状に複数配置されたCMOSセンサ型のイメージセンサに

おいて、画素部の電荷蓄積制御トランジスタ及びリセットトランジスタにチャネル形成領

域が酸化物半導体で形成されたトランジスタを使用し、マトリクス状に配置された全ての

画素で信号電荷蓄積部のリセット動作を行った後、全ての画素でフォトダイオードによる

電荷の蓄積動作を行い、行毎に画素から信号の読み出し動作を行うことで歪みの無い撮像

を可能とする。

(もっと読む)

液晶表示装置

【課題】液晶表示装置の消費電力を低減すること及び表示の劣化を抑制すること。また、温度などの外部因子による表示の劣化を抑制すること。

【解決手段】各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。なお、酸化物半導体層を高純度化することで、トランジスタの室温におけるオフ電流値を10aA/μm以下且つ85℃におけるオフ電流値を100aA/μm以下とすることが可能である。そのため、液晶表示装置の消費電力を低減すること及び表示の劣化を抑制することが可能になる。また、上述したようにトランジスタは、85℃という高温においてもオフ電流値を100aA/μm以下とすることが可能である。そのため、温度などの外部因子による液晶表示装置の表示の劣化を抑制することができる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

記憶装置

【課題】回路面積を小さくする。

【解決手段】記憶データとしてデータを記憶するメモリセルと、出力信号線と、電圧が与えられる配線と、を具備し、メモリセルは、記憶データと検索データの比較演算を行い、演算結果に応じて導通状態又は非導通状態になる比較回路と、記憶データの書き込み及び保持を制御する電界効果トランジスタと、を備え、比較回路が導通状態のときに、出力信号線の電圧値が配線の電圧と同等の値になる記憶装置。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

61 - 80 / 934

[ Back to top ]