Fターム[5F110QQ02]の内容

Fターム[5F110QQ02]に分類される特許

21 - 40 / 934

半導体装置の作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置の作製方法を提供する。

【解決手段】GRTA装置を用いて、第1の酸化物半導体膜に熱を加え、熱が加えられた第1の酸化物半導体膜に、酸素を添加して第2の酸化物半導体膜とし、GRTA装置を用いて、酸素が添加された第2の酸化物半導体膜に熱を加える。GRTA装置は、高温のガスを用いて加熱処理を行う装置であって、当該GRTA装置を用いると短時間での高温加熱処理が可能となる。

(もっと読む)

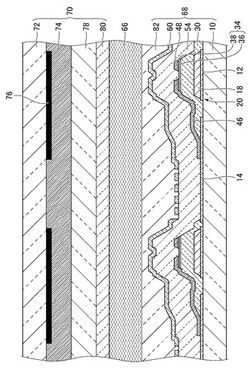

液晶表示装置及びその製造方法

【課題】フォトリソグラフィ工程を増やすことなく液晶表示装置を製造することを目的とする。

【解決手段】液晶表示装置は、第1透明電極14の端部に載る第1絶縁層30と、第1絶縁層30下のゲート電極18と、第1絶縁層30上の半導体層34と、半導体層34上から第1透明電極14上に至るように形成されて第1透明電極14に電気的に接続する第1配線46と、第1配線46から間隔をあけて半導体層34上から引き出された第2配線48と、第1配線46、第2配線48、半導体層34及び第1透明電極14を覆う第2絶縁層54と、第2絶縁層54上に形成された第2透明電極60と、第2透明電極60の上に配置された液晶層66と、を有する。第1透明電極14と第2透明電極60の間に印加される電圧によって、基板10の面方向に電界を加えて、液晶層66の液晶分子を基板10と平行な面内で回転させる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

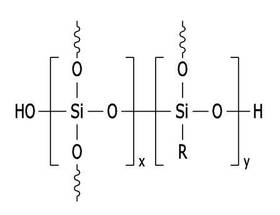

保護膜溶液組成物、薄膜トランジスター表示板及び薄膜トランジスター表示板の製造方法

【課題】保護膜溶液組成物を提供すること。

【解決手段】下記の化学式1で表わされる有機シロキサン樹脂を含む保護膜溶液組成物:

・・・化学式1

(式中、Rは1乃至25個の炭素を有する飽和炭化水素または不飽和炭化水素から選ばれた少なくとも一つの置換基であり、x、yはそれぞれ1乃至200であり、各波線は水素原子、xシロキサン単位またはyシロキサン単位との結合を示すか、あるいは、xシロキサン単位、yシロキサン単位またはこれらの組み合わせを含む他の有機シロキサン鎖のxシロキサン単位またはyシロキサン単位との結合を示す)。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

薄膜トランジスタアレイ基板の製造方法

【課題】 有機樹脂膜を有するTFTアレイ基板の製造工程において、ブラシ洗浄の際に異物が有機平坦化膜表面にキズを生じさせることがある。このようにキズが生じた有機平坦化膜上に、画素電極となる透明電極膜を成膜した場合、キズ上の透明電極膜も断線してしまい、画素電極に信号が伝わらず表示不良を引き起こすことがある。

【解決手段】 有機平坦化膜を塗布する工程と、中間調露光を用いて有機平坦化膜に凹凸を形成する工程と、凹凸が形成された有機平坦化膜表面をロールブラシを用いて洗浄する工程と、洗浄工程後に、有機平坦化膜上に画素電極を構成する透明導電膜を成膜する工程とを備えた薄膜トランジスタアレイ基板の製造方法を提供する。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制すること。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜において、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域は、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さくする。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

表示装置

【課題】高開口率を有し、容量の大きな保持容量を有する表示装置を提供する。

【解決手段】第1導電膜によるゲート電極と、第1導電膜上の第1絶縁層によるゲート絶縁膜と、第1絶縁層上にゲート電極と重なる第1半導体層と、第1半導体層上かつゲート電極に重なる第2絶縁層によるチャネル保護膜と、第1半導体層と重なりソース領域及びドレイン領域に分離された導電性の第2半導体層と、第2半導体層上の第2導電膜によるソース電極及びドレイン電極とを含む薄膜トランジスタと、第2導電膜上に形成された第3絶縁層と、第3絶縁層上の第3導電膜により形成され、ソース電極またはドレイン電極の一方と接続する画素電極と、第1絶縁層上の容量配線と、容量配線上の第3絶縁層を挟んで、画素電極の重畳領域に形成される保持容量とを有する表示装置及びその作製方法。

(もっと読む)

半導体装置

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

液晶表示装置

【課題】製造コストを削減するとともに歩留まりを向上し、かつプロセス設計が容易である液晶表示装置を提供すること。

【解決手段】液晶表示装置1において、半導体層ASIと半導体層ASIの液晶材側の面に形成された金属層Mとの積層部分であり、かつ画素電極MITの液晶材側の面に重なる部分である重なり部50を含むソース電極SD2を有し、第2の絶縁層PAS2は、ソース電極SD2の液晶材側の面から重なり部の50端部、及び画素電極MITの一部を開口するように形成されており、ソース電極SD2の液晶材側の面から重なり部50の端部上、及び画素電極MIT上に、ソース電極SD2の液晶材側の面から重なり部50の端部、及び画素電極MITを導通させる導体膜70が形成されている。

(もっと読む)

電子装置およびその製造方法

【課題】開口部を形成されることにより、大きなバンドギャップを有するグラフェンシートを有する電子装置を提供する。

【解決手段】基板と、前記基板上に形成されたグラフェンシート23と、前記グラフェンシートの一端に形成されたソース電極23Sと、前記グラフェンシートの他端に形成されたドレイン電極23Dと、前記グラフェンシート上ゲート絶縁膜を介して形成され、前記グラフェンシートにゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極を結ぶ方向を横切って形成された複数の開口部23Aよりなる開口部列と、を備え、前記複数の開口部はいずれも、三つのジグザグ端により画成されて正三角形の形状を有し、前記ジグザグ端のうち二つは、前記ソース電極とドレイン電極を結んだ方向に対し30°の角度をなし、もう一つのジグザグ端は90°の角度をなし、それぞれの正三角形の向きを揃えて形成されている。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

表示装置

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

半導体装置

【課題】新規な構成を有する半導体装置である。

【解決手段】第1の素子を有し、第2の素子を有し、トランジスタを有し、容量を有し、第1の素子の出力は、第2の素子の入力と電気的に接続され、第2の素子の出力は、第1の素子の入力と電気的に接続され、第1の素子の入力は、入力端子と電気的に接続され、第1の素子の出力は、出力端子と電気的に接続され、トランジスタのソース及びドレインの一方は、容量の一方の電極と電気的に接続され、トランジスタのソース及びドレインの他方は、入力端子と電気的に接続され、トランジスタのチャネル形成領域は、結晶を有する酸化物半導体を有する。結晶を有する酸化物半導体を有するトランジスタはリーク電流が非常に小さいため、データを保持することができる。

(もっと読む)

酸化物半導体層、半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであって、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極との接触抵抗を下げることができる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

21 - 40 / 934

[ Back to top ]