Fターム[5F140AA12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | SD領域の接合容量の低減 (90)

Fターム[5F140AA12]に分類される特許

1 - 20 / 90

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置

【課題】バルク半導体基板上に形成されるトンネルトランジスタ同士を電気的に分離することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板内に形成された第1および第2の素子分離絶縁膜とを備える。さらに、前記装置は、前記第1および第2の素子分離絶縁膜間の前記半導体基板上に、ゲート絶縁膜を介して形成されたゲート電極を備える。さらに、前記装置は、前記半導体基板内に前記ゲート電極を挟むように形成された、第1導電型の第1の主端子領域および前記第1導電型とは逆導電型の第2導電型の第2の主端子領域を備える。さらに、前記装置は、前記半導体基板内に前記第1および第2の素子分離絶縁膜に接するように形成され、前記第1および第2の主端子領域の下面よりも深い位置に上面を有する、前記第2導電型の第1の拡散層を備える。

(もっと読む)

窒化物半導体装置

【課題】スイッチングノイズ発生を抑制できるノーマリオフ形の窒化物半導体装置の提供。

【解決手段】本発明の実施形態の窒化物半導体装置は、AlxGa1−xN(0≦x<1)からなる第1の半導体層4と、AlyGa1−yN(0<y≦1、x<y)からなる第2の半導体層5と、導電性基板2と、第1の電極6と、第2の電極8と、制御電極7と、を備える。第2の半導体層は第1の半導体層に直接接合する。第1の半導体層は、導電性基板に電気的に接続される。第1の電極及び第2の電極は、第2の半導体層の表面に電気的に接続される。制御電極は、第1の電極と第2の電極との間の第2の半導体層の前記表面上に設けられる。第1の電極は、Si−MOSFET102のドレイン電極8aに電気的に接続される。制御電極は、前記MOSFETのソース電極6aに電気的に接続される。導電性基板は、前記MOSFETのゲート電極7aに電気的に接続される。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

スイッチング素子及びこれを用いた電源装置

【課題】ソース電極とドレイン電極間の容量を低減し、スイッチングロスを減らすことができるスイッチング素子、及び該スイッチング素子を搭載した効率が向上した電源装置の提供。

【解決手段】Si基板1と、該Si基板1上に形成されたソース電極8及びドレイン電極9を有してなり、ソース電極8及びドレイン電極9の配置方向と直交する方向の層中であって、ソース電極8及びドレイン電極9のいずれか一方のみと接している領域に、p型領域とn型領域が接している部分24であるpn接合を少なくとも1つ有するスイッチング素子である。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

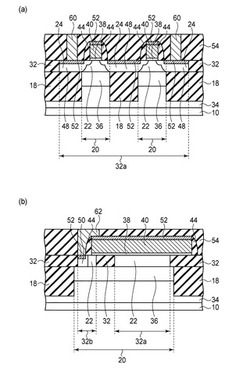

半導体装置およびその製造方法

【課題】MOSトランジスタのソース及びドレイン電極に生じる寄生容量を低減する。高速動作が可能な半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタを備える。MOSトランジスタは、1対の第1、第2及び第3の不純物拡散領域を有する。第2の不純物拡散領域は、第1の不純物拡散領域を挟むように半導体基板内に設けられた第1導電型の不純物拡散領域であり、第1の不純物拡散領域よりも第1導電型の不純物濃度が高くなる。第3の不純物拡散領域は、1対の第1の不純物拡散領域に接すると共に第2の不純物拡散領域に接しないように、半導体基板内に設けられた第2導電型の不純物拡散領域である。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

半導体装置の製造方法

【課題】ソース/ドレイン領域と基板との間の容量の低下を防止でき、パンチスルー現象を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極の上面及び側面を覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をマスクとして前記半導体基板の表面に溝部を形成する工程と、前記溝部の底面上に、該溝部の側壁の上部の露出を残す厚さで第3絶縁膜を形成する工程と、前記露出された溝部の側壁の上部を起点としたエピタキシャル成長により、前記第3絶縁膜上に前記半導体のエピタキシャル層を形成する工程と、前記エピタキシャル層に不純物を導入してソース/ドレイン領域を形成する工程と、を有することを特徴とする

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【目的】コンタクト領域を確保し、ドレイン接合容量とリーク電流を減少させることができる半導体装置およびその製造方法を提供する。

【解決手段】ゲート電極5上のシリコン酸化膜6をマスクにドレイン領域7に斜めトレンチ10を形成して、ドレイン領域7の幅をコンタクト領域を形成できる最小幅にすることで、ドレイン接合容量とリーク電流を減少させる。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

半導体装置

【課題】寄生容量を増やさずにソフトエラー率を低減することのできる半導体装置を提供する。

【解決手段】半導体基板の主表面に形成された第1導電型ウェルと、第1導電型ウェルの表面に形成されたトランジスタと、半導体基板の主表面に形成された素子分離絶縁領域と、第1導電型ウェルの表面に前記トランジスタと素子分離絶縁領域を隔てて形成され、底面の深さがおおよそ当該素子分離絶縁領域の底面と等しく、第1導電型ウェルより不純物濃度が高い第1導電型高濃度領域と、第1導電型高濃度領域の表面に形成されたウェルコンタクト電極と、を備える。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

水素化ホウ素クラスターイオンの注入によるイオン注入装置及び半導体製造方法

【課題】イオン化チャンバ内の電子ビーム通路に均一な磁場を生成する磁場装置を提供する。

【解決手段】電子衝撃イオン源用の磁場装置において、イオン化チャンバ内の電子ビーム通路に均一な磁束線119を生成させるために、一対の永久磁石510A、510Bにより生成された磁束が、磁気ヨークアセンブリ500を経て、電子ビーム通過用の一対の整列した開口530A、530Bを有する磁極片520A、520Bの間の間隙を通って戻るようにする。

(もっと読む)

延長型ドレイン電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 拡張型ドレイン絶縁ゲート電界効果トランジスタ(104又は106)が、第1ウエル領域(184A又は186A)の一部によって構成されているチャンネル(322又は362)ゾーンによって横方向に分離されている第1及び第2ソース/ドレインゾーン(324及び184B又は364及び186B/136B)を包含している。

【解決手段】 ゲート誘電体層(344又は384)が該チャンネルゾーンの上側に存在している。該第1ソース/ドレインゾーンは、通常は、ソースである。通常はドレインである該第2S/Dゾーンは、少なくとも部分的には第2ウエル領域(184B又は186B)で構成されている。該半導体ボディのウエル分離部分(136A又は212U/136B)が該ウエル領域の間を延在しており且つ各ウエル領域よりも一層軽度にドープされている。該ウエル領域の構成は、該半導体ボディのIGFETの部分における最大電界をして上部半導体表面の十分に下側、典型的には該ウエル領域同士が互いに最も近い箇所におけるか又はその近くで発生させる。該IGFETの動作特性は動作時間と共に安定である。

(もっと読む)

ソース/ドレイン延長部又は/及びハローポケットと組み合わせて空のウエルを使用した電界効果トランジスタの構成及び製造

【課題】 混合信号適用例を含むアナログ及びデジタル適用例用のIGFETを与える半導体製造プラットフォームに適した対称的及び非対称的の両方の絶縁ゲート電界効果トランジスタ(「IGFET」)が、高性能を達成する上で空のウエル領域を使用する。

【解決手段】 各空のウエルの上部近くにおいては半導体ウエルドーパントが比較的少量である。各IGFET(100,102,112,114,124又は236)は、空のウエル(180,182,192,194,204又は206)のボディ物質のチャンネルゾーンによって横方向に分離された一対のソース/ドレインゾーンを有している。ゲート電極が該チャンネルゾーン上方でゲート誘電体層の上側に位置している。各ソース/ドレインゾーン(240,242,280,282,520,522,550,552,720.722、752又は752)が主要部分(240M,242M,280M,282M,520M,522M,550M,552M,720M,722M,752M又は752M)及び一層軽度にドープした横方向延長部(240E,242E,280E,282E,520E,522E,550E,552E,720E,722E,752E又は752E)を有している。代替的に又は付加的に、該ボディ物質の一層高度にドープしたポケット部分(250又は290)が該ソース/ドレインゾーンの内の一方に沿って延在する。存在する場合には、該ポケット部分は典型的に該IGFETを非対称的装置とさせる。

(もっと読む)

L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体

【課題】 非対称的電界効果トランジスタ(102)の製造は、半導体ボディのボディ物質のチャンネルゾーン(284)の上方でそれからゲート誘電体層(300)によって垂直方向に分離されているゲート電極(302)を画定することとなる。

【解決手段】 該ゲート電極をドーパント阻止用シールドとして使用して、半導体ドーパントを該ボディ物質内に導入させて、一層高度にドープしたポケット部分(290)を画定する。該ゲート電極に沿ってスペーサ(304T)を設ける。該スペーサは、(i)該ゲート電極に沿って位置されている誘電体部分、(ii)該半導体ボディに沿って位置されている誘電体部分、及び(iii)該他の2つのスペーサ部分の間の空間をほぼ占有するフィラー部分(SC)、を包含している。該ゲート電極及び該スペーサをドーパント阻止用シールドとして使用して、半導体ドーパントを該半導体ボディ内に導入させて、一対のソース/ドレイン部分(280M及び282M)を画定する。該フィラースペーサ部分を除去して該スペーサをL形状(304)へ変換させる。一対の電気的コンタクト(310及び312)を夫々該主要ソース/ドレイン部分に対して形成する。

(もっと読む)

1 - 20 / 90

[ Back to top ]