Fターム[5F140AA31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | サージ入力対策 (54)

Fターム[5F140AA31]に分類される特許

1 - 20 / 54

半導体装置およびその製造方法

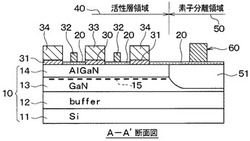

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置

【課題】チップ面積を増大させずにスナップバック現象を抑制することのできる、IGBTと他の半導体素子とが一体化して配置された半導体装置を提供する。

【解決手段】IGBTとドリフト層を有する他の半導体素子とを備えた半導体装置であって、IGBTのドリフト層と他の半導体素子のドリフト層とが互いに接しており、IGBTのエミッタ層と他の半導体素子のドリフト電界を発生させる電圧が印加される一方の極性層とが互いに導電的に接続されており、IGBTのコレクタ層と他の半導体素子の他方の極性層とが互いに導電的に接続されており、IGBTのドリフト層の他の半導体素子のドリフト層との境界から離れた領域に絶縁層を介して対向する領域をドリフト方向に沿って延伸し、Nチャネル型IGBTではコレクタ側からエミッタ側に向けて電流が流され、Pチャネル型IGBTではエミッタ側からコレクタ側に向けて電流が流される配線部が設けられている。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 素子分離にシャロートレンチ分離領域を有するESD保護用のN型MOSトランジスタにおいて、前記ESD保護用のN型MOSトランジスタのドレイン領域の一部分のみが前記ESD保護用のN型MOSトランジスタのゲート絶縁膜を介して前記ESD保護用のN型MOSトランジスタのゲート電極と重なり合う重畳部を形成する半導体装置とした。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アンテナ効果によるゲート酸化膜の破壊等を防止するとともに、半導体装置の動作の遅延を抑制すること。

【解決手段】本発明の一態様に係る半導体装置は、前段出力トランジスタA1に金属配線A2aを介して接続された入力トランジスタゲート電極A9を有する入力トランジスタA3と、入力トランジスタゲート電極A9に抵抗素子A4を介して接続されたダミートランジスタA5を備える。抵抗素子A4は、入力トランジスタA3の後段に設けられ、金属配線A2aに接続されている。抵抗素子A4とダミートランジスタA5は、金属配線A2bを介して接続されている。

(もっと読む)

半導体装置

【課題】小型の静電破壊保護トランジスタを有する半導体装置を提供する。

【解決手段】第1導電型の半導体層12に、ゲート絶縁膜13を介して形成されたゲート電極14と、ゲート電極14のゲート幅方向Yに沿って形成された第2導電型の第1不純物拡散層15と、ゲート幅方向Yに沿って第1不純物拡散層15と対向配置された本体部16aと、本体部16bからゲート電極14と反対側に突出した複数の凸部16bとを有し、ゲート電極14のゲート長方向Xの幅Wd1が第1不純物拡散層15のゲート長方向Xの幅Ws1より大きい第2導電型の第2不純物拡散層16と、を備えた絶縁ゲート電界効果トランジスタ17を具備する。

(もっと読む)

静電気放電保護装置及び方法

【課題】静電気放電保護装置及び方法を提供する。

【解決手段】本発明の実施例は、静電気放電(ESD)保護装置、及び、ESD保護装置を形成する方法に関する。一実施例は、ESD保護装置で、基板に配置されたpウェルと、基板に配置されたnウェルと、基板中のpウェルとnウェルの間に配置された高電圧nウェル(HVNW)と、pウェルに配置されたソースn+領域と、nウェルに配置された複数のドレインn+領域と、からなる。

(もっと読む)

分離されたNMOSベースのESDクランプセルのためのシステムおよび方法

本発明は、ICチップをESDから保護するための保護回路に関する。集積回路チップのためのESD保護回路は、分離されたNMOSトランジスタを備えていて、これは、バックゲートを基板から分離している分離領域と、バックゲート上に形成された第1および第2ドーピング領域およびゲートとを有している。ESD保護回路は、分離領域を第1電気ノードに接続する第1端子と、第2ドーピング領域を第2電気ノードに接続する第2端子とを更に備え得る。第1電気ノードは、第2電気ノードより高い電圧レベルを有していてもよく、かつゲートおよびバックゲートは、第2端子に接続され得る。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法、静電放電保護素子

【課題】製造効率を向上すると共に、内部回路の保護を的確に行う。

【解決手段】サージ電圧が入力パッドPADに入力された際に、ゲート電極501が、Pウェル201にて絶縁層301を介して対面する部分201Bに、キャリアを誘起させるように構成する。これにより、ESD保護素子101において、寄生バイポーラトランジスタの直流電流増幅率hFEを上昇させ、スナップバック開始電圧Vt1を低下させる。

(もっと読む)

半導体装置

【課題】MOSトランジスタのESD耐量を向上することが可能な半導体装置を提供する。

【解決手段】半導体装置100は、MOSトランジスタ1と、多結晶シリコンからなる多結晶シリコンダイオードが複数直列に接続されて構成された第1のダイオード回路116と、第1のダイオード回路の複数の多結晶シリコンダイオードの逆方向降伏電圧の総和よりも低い逆方向降伏電圧を有し、単結晶シリコンからなる第1の単結晶シリコンダイオード18と、多結晶シリコンからなる多結晶シリコンダイオードが複数直列に接続されて構成された第2のダイオード回路117と、第2のダイオード回路の複数直列に接続された多結晶シリコンダイオードの逆方向降伏電圧の総和よりも低い逆方向降伏電圧を有し、単結晶シリコンからなる第2の単結晶シリコンダイオード19を備える。

(もっと読む)

トランジスタ型保護素子、半導体集積回路およびその製造方法

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、ゲート電極4、ソース領域5、ドレイン領域6および抵抗性降伏領域8を有する。抵抗性降伏領域8はドレイン領域6に接し、ゲート電極4直下のウェル部分と所定の距離だけ離れたN型半導体領域からなる。ドレイン領域6または抵抗性降伏領域8に接合降伏が発生するドレインバイアスの印加時に抵抗性降伏領域8に電気的中性領域(8i)が残るように、抵抗性降伏領域8の冶金学的接合形状と濃度プロファイルが決められている。

(もっと読む)

半導体装置

【課題】ESD保護素子としてMISトランジスタを備えた半導体装置において、MISトランジスタの面積の増大を招くことなく、MISトランジスタ内の動作均一性を高める。

【解決手段】半導体基板10に形成されたMISトランジスタを備えた半導体装置であって、MISトランジスタは、半導体基板10に形成されたドレイン拡散層15と、半導体基板10上にチャネル幅方向に沿って互いに間隔を空けて配置され、ドレイン拡散層15をチャネル幅方向に沿って互いに分割する複数の分割体14と、半導体基板10上に分割体14を覆うように形成され、ドレイン拡散層15のチャネル幅方向に応力を生じさせる応力膜17とを備えている。

(もっと読む)

半導体装置

【課題】高耐圧を有する半導体装置において、製造工程を追加することなく、求められる機能を満たしたESD保護素子を提供する。

【解決手段】高耐圧を有する半導体装置をノイズやサージから守るESD保護素子において、ゲート電極33の両端に形成されたドレイン側でないLOCOS酸化膜21bの下に形成される拡散層14bの導電型をP型にすることにより、ドレインの表面ブレークダウンにより生じる電流がソース側N型高濃度拡散層15a下を流れる量を制限して、寄生NPNバイポーラ動作の保持電圧を高くすることが可能となり、工程追加無しに、内部素子に必要な拡散層や絶縁膜を用いてESD保護素子を設定することが可能となる。定常状態においてはオフ状態にあるが、サージやノイズが半導体装置に印加された場合には、内部素子が破壊に至る前にESD保護素子が動作して大電流を放出し、その後再びオフ状態に戻るという機能を満たす。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】入力電圧ライン11と誘導性負荷Lとの間に接続される第1のスイッチング素子M1を有するハイサイドスイッチング素子と、誘導性負荷Lと基準電圧ラインとの間に並列接続される第2のスイッチング素子M2と第3のスイッチング素子M3とを有するローサイドスイッチング素子と、を備え、ローサイドスイッチング素子における誘導性負荷Lに接続される端子にサージが印加されたとき、サージ電流は第3のスイッチング素子M3を介して基準電圧ラインへと放電される。

(もっと読む)

1 - 20 / 54

[ Back to top ]