Fターム[5F140AA39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 微細化 (812)

Fターム[5F140AA39]に分類される特許

801 - 812 / 812

半導体装置の製造方法およびその方法で得られる半導体装置

本発明は、シリコンの半導体本体がその表面に拡張領域を含む第1の導電型のソース領域及びドレイン領域と、前記ソース領域と前記ドレイン領域の間に前記第1の導電型とは反対の第2の導電型のチャネル領域と、前記チャネル領域上のゲート誘電体により前記半導体本体の表面から分離されているゲート領域と、を有し、第2の導電型で前記チャネル領域より高濃度のドーピング濃度であるポケット領域が前記拡張領域の下に形成され、前記ポケット領域は前記半導体本体に重イオンを注入することで形成され、注入後適温での第1のアニール処理およびより高い温度で早い立ち上がりの第2のアニール処理が行われる電界効果トランジスタを備える半導体装置の製造方法に関する。本発明によれば、その方法は、2つのアニール処理の間に、半導体本体の表面からポケット注入領域まで延びる半導体本体の表面領域にアモルファスシリコンを意図的に存在させることを特徴とする。これは、例えば適時に第1のアニール処理を中断すること、または第1と第2のアニール処理の間に不活性イオンを注入することで適切な領域をアモルファス化することにより得られる。このようにして、将来のCMOS装置の利点であるポケット領域7のきわめて急峻かつ狭いドーピングプロファイルが得られる。  (もっと読む)

(もっと読む)

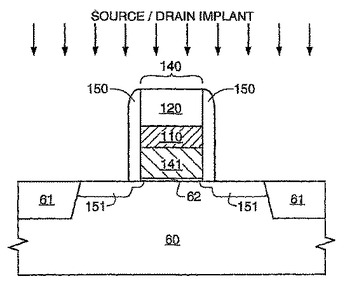

シリサイドをソース/ドレインに用いた半導体素子

半導体素子において、非常に深い位置に達するゲルマニウムイオン注入及びゲルマニウムの活性化をニッケルシリサイド形成用のニッケルの堆積の前に行なう。ゲルマニウムを活性化させることにより、イオン注入領域の格子定数が、シリコンであることが好ましい母体基板の格子定数よりも大きくなる。このような変化が加えられた格子によって、ニッケルダイシリサイドの形成を防止することができるという効果が得られる。その結果、ニッケルシリサイドスパイクを防止することができる。  (もっと読む)

(もっと読む)

FETゲート電極用のCVDタンタル化合物(TaおよびNを含む化合物の化学的気相堆積方法および半導体電界効果デバイス)

【課題】電界効果デバイスのゲート材料を提供すること。

【解決手段】電界効果デバイスのゲート材料として用いられるTaおよびNの化合物であって、さらに別の元素を含む可能性があり、約20mΩcmより小さな比抵抗を有し、約0.9より大きなN対Taの元素比を有する化合物が開示される。そのような化合物の代表的な実施態様であるTaSiNは、誘電体層および高k誘電体層を含むSiO2上の一般的なCMOSプロセス温度で安定であり、n型Siの仕事関数に近い仕事関数を有する。第3アミルイミドトリス(ジメチルアミド)Ta(TAIMATA)などのアルキルイミドトリス(ジアルキルアミド)Ta化学種をTa前駆体として用いる化学的気相堆積方法によって、金属性Ta−N化合物を堆積する。この堆積は共形であり、これらのTa−N金属化合物のCMOSプロセスフローへの融通の利く導入を可能にする。TaNまたはTaSiNを用いて加工されたデバイスは、ほぼ理想的な特性を示す。

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

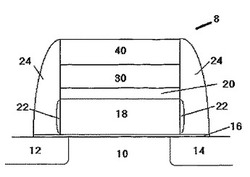

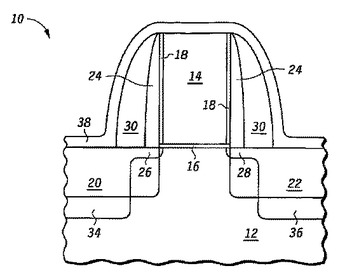

減少されたゲート高さを有するトランジスタを製造する方法

【課題】減少されたゲート高さを有する集積回路トランジスタを形成する方法およびシステムを開示すること。

【解決手段】本方法は、基板、基板の上のゲート導体(13)、およびゲート導体(13)の上の少なくとも1つの犠牲層(14〜16)を有する積層構造を形成する。このプロセスは、積層構造を基板から延びる少なくとも1つのゲート・スタックにパターン形成し、ゲート・スタックに隣接してスペーサ(60)を形成し、ゲート・スタックに隣接してソースおよびドレイン領域(71)を形成するようにスペーサで保護されていない基板の領域にドーピングし、そして、スペーサ(60)および犠牲層(14〜16)を除去する。

(もっと読む)

マスキング方法

本発明はマスキング方法を包含する。1つの実施において、ホウ素ドープアモルファスカーボンを含むマスキング材料が、半導体基板上に形成されたフィーチャーを覆って形成される。マスキング材料は少なくとも約0.5原子パーセントのホウ素を含む。マスキング材料は実質的に異方的にエッチングされ、ここでそのエッチングはホウ素ドープアモルファスカーボンを含む異方的にエッチングされたサイドウォールスペーサをフィーチャーのサイドウォール上に形成するのに有効である。次に、スペーサに最も近い基板が、ホウ素ドープアモルファスカーボンを含むスペーサをマスクとして用いながら加工される。スペーサに最も近い基板を加工した後、ホウ素ドープアモルファスカーボンを含むスペーサが基板からエッチングされる。他の実施および面も考えられる。 (もっと読む)

集積化金属珪化物ゲート電極を有するトランジスタの形成方法

集積化した金属珪化物トランジスタゲート電極を有するトランジスタを半導体アセンブリ内に形成する方法を提供する。トランジスタゲートは部分的に、金属を溝内に存在させた状態でエピタキシャルシリコンと反応させることにより製造する。前記溝内で前記金属珪化物上にトランジスタゲート分離キャップ層を形成する。任意ではあるが溝スペーサを設けて所定の製造処理の臨界的な寸法上の制約を低減させ、従って、形状寸法が臨界的な寸法よりも小さいトランジスタを形成しうるようにすることができる。  (もっと読む)

(もっと読む)

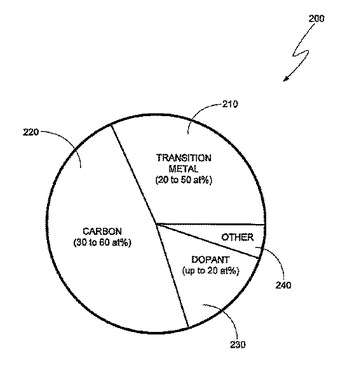

ゲート電極として使用される遷移金属合金およびこれらの合金を取り入れた装置

高温で顕著に変化しないn型またはp型の仕事関数を有する遷移金属合金の実施例を示した。示された遷移金属合金は、トランジスタのゲート電極として使用しても良く、ゲート電極の一部を構成しても良い。これらの遷移金属合金を用いて、ゲート電極を形成する方法についても示した。  (もっと読む)

(もっと読む)

電気試験データに基づいてゲート絶縁層の特性および特徴を制御するための方法、これを実施するためのシステム

本発明は、一般に、電気試験データ(46)に基づいてゲート絶縁層(16)の特性および特徴を制御する各種方法、ならびにこれを実施するためのシステムを対象としている。例示的な一実施形態では、上記方法は、少なくとも1つの半導体デバイスに少なくとも1つの電気試験を実施するステップと、以降形成する半導体デバイスに少なくとも1つのゲート絶縁層(16)を形成するために実施する少なくとも1つのプロセス操作の少なくとも1つのパラメータを、電気試験から得られた電気データに基づいて決定するステップと、決定されたパラメータを含む少なくとも1つのプロセス操作を実施して、ゲート絶縁層(16)を形成するステップとを有する。  (もっと読む)

(もっと読む)

多成分誘電体膜を形成するためのシステム及び方法

【課題】半導体用途における誘電体膜を形成するためのシステム及び方法、特に、混合気化前駆体を用いて基板上に多成分誘電体膜を作製するためのシステム及び方法を提供する。

【解決手段】本発明は、気化した前駆体の混合物が、原子層堆積(ALD)処理における単一パルス段階中にチャンバ内に一緒に存在して多成分膜を形成するような気化前駆体の混合をもたらすためのシステム及び方法を提供する。気化前駆体は、少なくとも1つの異なる化学成分から成り、そのような異なる成分が単層を形成して多成分膜を生成することになる。本発明の更に別の態様では、組成勾配を有する誘電体膜が提供される。

(もっと読む)

801 - 812 / 812

[ Back to top ]