Fターム[5F140AC20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 単一電子素子 (10)

Fターム[5F140AC20]に分類される特許

1 - 10 / 10

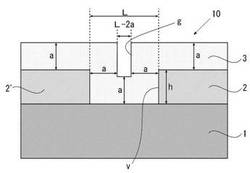

微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子

【課題】10nm程度の溝を有する微細構造物を安価で簡便かつ高精度に作製可能な微細構造物の製造方法、該微細構造物の製造方法により製造される微細構造物、及び該微細構造物を有する電界効果型半導体素子を提供すること。

【解決手段】本発明の微細構造物の製造方法は、トップダウン形成法により、基板上に少なくとも2つの凸状の形状からなる第1の構造体を形成する第1の構造体形成工程と、ボトムアップ形成法により、前記第1の構造体が形成された基板上に形成材料を堆積させ、隣接する前記第1の構造体の中間位置に凹状の溝を有する第2の構造体を形成する第2の構造体形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】間接遷移型の半導体を用いた場合でも、単一の電子の転送により単一の光子が生成できるようにする。

【解決手段】p型領域102とn型領域103とに挾まれた領域の半導体層101に導入された第1不純物原子106および第2不純物原子107からなる不純物原子対を備える。ここで、不純物原子対は、p型領域102とn型領域103とが対向して配置されている方向(第1方向)で、p型領域102とn型領域103とに挾まれた領域(チャネル領域)に配置される。また、第1不純物原子106および第2不純物原子107は、上記チャネル領域のゲート電極105の側の界面より30nmの範囲に導入されている。

(もっと読む)

単電子ターンスタイルデバイスおよびその製造方法

【課題】より小さな単電子島が作製でき、また、高い精度を必要とせずにトップゲートが配置できるようにする。

【解決手段】形成しようとする細線の延在方向に対して直交して開口部104を挟む2つの箇所に、対向して配置される2つの溝部105を形成する。溝部105は、絶縁層101に到達するまで形成する。次に、酸化シリコン層103を介してシリコン層102の上層部を熱酸化し、シリコン層102をより薄くする。この酸化工程により、開口部104の対向する2つの曲線状の縁部に対応する曲線状の境界部の内側近傍において、層厚方向にくびれるくびれ部107が形成され、くびれ部107においては、シリコン層102の層厚がより薄くなり、層厚方向の量子サイズ効果によりトンネルバリアが形成されるようになる。

(もっと読む)

単一電荷トンネル素子

【課題】不揮発性メモリ素子としても使用可能な、単一電荷トンネル素子、特に単一電子トランジスタ、を提供する。

【解決手段】強磁性物質から成る単一電荷トンネル素子を従来のようにゲート電圧の印加により電気モードにおいて制御するのみならず、回転する配向磁場の印加により磁気モードにおいても制御する。即ち、該配向磁場の印加により該強磁性物質の化学ポテンシャルが変化し、クーロンブロッケード異方性磁気抵抗効果が生じる。その結果として得られる該素子の抵抗値とその変化を、論理的な1,0の書込み信号と、その切り替えに用いる。該磁気モードのヒステリシス性により、不揮発性メモリ効果が発現される。

(もっと読む)

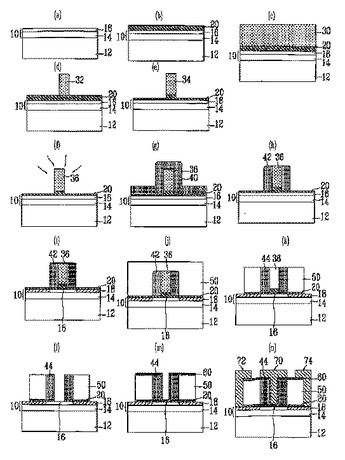

半導体素子の製造方法

本発明は、リソグラフィ工程を経たフォトレジストの特性を変化させてダミー構造物を形成し、これをゲート電極形成工程に適用した半導体素子の製造方法に関することで、半導体基板上の最上部にバッファー層を形成するステップと、前記バッファー層の上部に無機物フォトレジストを塗布してリソグラフィを通じてフォトレジストパターンを形成するステップと、前記形成されたパターンに特定ガスを使用して熱処理を行うステップと、前記熱処理された構造物の上部に均一な厚さの絶縁膜を蒸着した後に前記パターンが露出されるように前記蒸着された膜をエッチングするステップと、前記工程を経た構造物に絶縁膜を蒸着し、前記パターンが露出されるように前記絶縁膜をエッチングするステップと、前記露出されたパターンを除去するステップと、前記パターンが除去された位置にゲート酸化膜を形成するステップと、前記形成されたゲート酸化膜の上部にゲート電極を形成するステップと、を含む。本発明によれば、ナノ素子を製作するための構造を形成する時、リソグラフィを通じて形成された膜の特性が後続熱処理を通じて改善されるので、多様な素子を製作するための構造を容易に形成することができる。  (もっと読む)

(もっと読む)

電子装置、電子装置の製造方法、電子回路及び電子機器

【課題】 特性を安定にでき、製造コストが安価で、高集積化を行い易く、また、効果的に消費電力の低減を行うことができる電子装置とその製造方法を提供すること。

【解決手段】 電子装置は、絶縁体101の中に、金属で形成された第1領域102及び第2領域103と、この第1領域102と第2領域103で挟まれた第3領域104を備える。この第3領域は、第1及び第2領域102,103を形成する金属元素と同じ金属元素で形成されて、直径が20nm以下の微粒子を有する。第1領域102及び第2領域103は、第3領域104よりも、金属濃度が高くて電気抵抗が小さい。第1領域102と第2領域103とに電圧が印加されて、第3領域104を単一の電荷がトンネルする。第1領域102と、第2領域103と、第3領域104とは、互いに同じ金属元素を含むので、互いの境界に形成される障壁を安定にできる。

(もっと読む)

半導体装置、半導体装置の製造方法、セルアレイ及びセルアレイの製造方法

【課題】 スイッチ機能が十分に得られ、常温においても十分にスイッチ動作ができ、微細化を図ることができるスイッチング素子を提供すること。

【解決手段】 基板101上に形成されたゲート絶縁膜102上に、第2絶縁膜105で隔てられた第1電極103と第2電極104を形成する。第1電極103は、ゲート絶縁膜102の表面に接する側の部分が鋭角断面を有するように、側面が傾斜している。ゲート絶縁膜102中に、20nm以下の直径を有すると共に、第1電極3と第2絶縁膜105との境界が含まれる平面と略同一の平面上に配列された金属微粒子106を形成する。第1絶縁膜2中の金属微粒子6の数を、第1絶縁膜2の膜厚と、第1絶縁膜2への金属元素の注入及びアニール条件とで制御できるので、微細加工の最小加工寸法の制約を受けない。また、ゲート長を、ゲート絶縁膜102の厚みによって設定できるので、微細加工の最小加工寸法の制約を受けない。

(もっと読む)

半導体装置及びその駆動方法

【課題】高い精度で電子の転送が可能でより高温で動作可能であり、かつより容易に製造ができる半導体装置を提供する。

【解決手段】半導体層101と、半導体層101の表面より形成されたp型領域102と、半導体層101の表面よりp型領域102と離間して形成されたn型領域103と、半導体層101の表面に形成されたゲート絶縁層104と、p型領域102とn型領域103との間のゲート絶縁層104の上に形成されたゲート105とを備える。加えて、p型領域102とn型領域103とに挟まれた半導体層101の表面より30nm以内の領域に導入された1個の不純物106を備えている。不純物106は、p型領域102とn型領域103とに挟まれたチャネル領域に導入されている。

(もっと読む)

ナノワイヤの製造方法

【課題】 太さが数ナノメータから数十ナノメータで、長さが1マイクロメータ以上のナノワイヤを、自己組織化により効率的に、かつ、確実に製造する方法を提案すること。

【解決手段】 表面が清浄な結晶面である基板(例えば、Siの単結晶の[100]面、または[110]面、または[111]面)を準備する基板準備過程と、ナノワイヤを作るための材料(例えば、ErCl3)を上記基板の表面に付着させる(例えば、スピンココーティング法、またはレーザアブレーション法による)材料供給過程と、上記基板の上記材料が付着された表面の前に微小空間を形成する(例えば、スペーサ式微小空間形成、または凹部式微小空間形成による)微小空間形成過程と、上記微小空間が前面に形成された上記基板を真空中で所定温度に保つアニール過程とからなる、ナノワイヤの製造方法とした。

(もっと読む)

ショットキー障壁貫通単電子トランジスタ及びその製造方法

【課題】PADOXのような工程を用いず、トンネル障壁の高さ及び幅を人為的に調節することができる上、電流駆動能力をさらに向上させることができるショットキー障壁貫通単電子トランジスタ及びその製造方法の提供。

【解決手段】ショットキー障壁貫通単電子トランジスタは、基板100上に形成された絶縁層110と、ソース/ドレイン領域120a/120bの少なくとも一部分はシリサイド化されてチャネル領域120bとショットキー接合される。また、ゲート絶縁膜130、ゲート電極140、側壁絶縁膜150、層間絶縁膜パターン160、及び露出した前記ゲート電極140及び前記ソース/ドレイン電極120a/120b上に形成された金属配線170を備える。

(もっと読む)

1 - 10 / 10

[ Back to top ]