Fターム[5F140BB04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSVC(垂直表面垂直電流) (285)

Fターム[5F140BB04]に分類される特許

281 - 285 / 285

半導体装置およびその製造方法

【課題】 閾値の変動を回避するとともに、電気的ストレスに対する信頼性の高いMOSトランジスタを備えた半導体装置を提供する。

【解決手段】 素子領域を画定する素子分離領域(12)が設けられた半導体基板(11)と、前記半導体基板の前記素子領域に離間して設けられたソース/ドレイン領域(25)と、前記半導体基板の前記素子領域上に設けられたゲート絶縁膜(13,14)と、前記ゲート絶縁膜上に設けられ、半導体を含むゲート電極(15)とを具備する半導体装置である。前記ゲート絶縁膜は、金属および酸素を含有する第1の絶縁膜(13)と、この第1の絶縁膜上に形成され、シリコンおよび酸素を含有する第2の絶縁膜(14)とを含み、前記第2の絶縁膜は、前記ゲート電極との界面における前記金属の含有量が6.6atomic.%未満であることを特徴とする。

(もっと読む)

半導体集積回路

【課題】 保護ダイオードの逆方向耐圧よりも低電圧で動作する保護回路を有する半導体集積回路を実現する。

【解決手段】 静電保護回路には、N+ドレイン層D1とN+多結晶シリコン膜16が接続され、N+多結晶シリコン膜16をゲート、N+ドレイン層D1をドレイン、第1のNウエル層11をソース、第1のPウエル層13をチャネルとする縦型トレンチMOSトランジスタTR1が設けられている。N+多結晶シリコン膜16と第1のPウエル層13、第1のNウエル層11、及びP型シリコン基板10の間に容量C1が設けられている。一方、P型シリコン基板10と第2のNウエル層12の間にダイオードDi1が設けられている。

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

高耐圧用半導体素子及びその製造方法

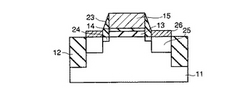

本発明は高耐圧用半導体素子およびその製造方法に関するものであり、本発明ではゲート電極パターンを半導体基板の底部に埋め込まれて形成すると共に、このゲート電極パターンの両方の側部にソース/ドレイン拡散層のための低濃度不純物層及び高濃度不純物層を順次に積層形成し、これにより、高濃度不純物層がゲート電極パターンと別途の離隔距離を確保しなくても、自身に必要な一連の電圧降下領域を容易に確保できるように誘導することで、高濃度不純物層及びゲート電極パターンの離隔による素子のサイズ増加を事前に防止することができる。

このような本発明の実施によって、高濃度不純物層及びゲート電極パターンの離隔必要性が効果的に除去される場合、最終完成する素子のサイズは大幅に減り、結局、素子のサイズ増加による製造コストの上昇問題点も自然に解決される。  (もっと読む)

(もっと読む)

FETゲート電極用のCVDタンタル化合物(TaおよびNを含む化合物の化学的気相堆積方法および半導体電界効果デバイス)

【課題】電界効果デバイスのゲート材料を提供すること。

【解決手段】電界効果デバイスのゲート材料として用いられるTaおよびNの化合物であって、さらに別の元素を含む可能性があり、約20mΩcmより小さな比抵抗を有し、約0.9より大きなN対Taの元素比を有する化合物が開示される。そのような化合物の代表的な実施態様であるTaSiNは、誘電体層および高k誘電体層を含むSiO2上の一般的なCMOSプロセス温度で安定であり、n型Siの仕事関数に近い仕事関数を有する。第3アミルイミドトリス(ジメチルアミド)Ta(TAIMATA)などのアルキルイミドトリス(ジアルキルアミド)Ta化学種をTa前駆体として用いる化学的気相堆積方法によって、金属性Ta−N化合物を堆積する。この堆積は共形であり、これらのTa−N金属化合物のCMOSプロセスフローへの融通の利く導入を可能にする。TaNまたはTaSiNを用いて加工されたデバイスは、ほぼ理想的な特性を示す。

(もっと読む)

281 - 285 / 285

[ Back to top ]