Fターム[5F140BB04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSVC(垂直表面垂直電流) (285)

Fターム[5F140BB04]に分類される特許

141 - 160 / 285

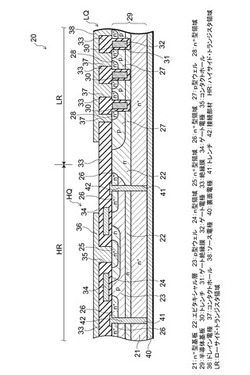

半導体装置及びその製造方法

【課題】小型で配線抵抗が小さい半導体装置及びその製造方法を提供する。

【解決手段】半導体基板29の領域HRの上層部分に横型のMOSFETからなるハイサイド・トランジスタHQを形成すると共に、領域LRに縦型のMOSFETからなるローサイド・トランジスタLQを形成する。次に、ハイサイド・トランジスタHQのソース領域(n+型領域26)を貫通し、ローサイド・トランジスタLQのドレイン領域(n+型基板21)に相当する深さまで到達する接続部材42を形成し、半導体基板29の下面を研削して接続部材42を露出させ、半導体基板29の下面上に、接続部材42及びローサイド・トランジスタLQのドレイン領域(n+型基板21)の双方に接続された裏面電極40を形成する。これにより、半導体チップ20が作製される。この半導体チップ20は、DC−DCコンバータの出力回路を構成する。

(もっと読む)

半導体素子の製造方法

【課題】垂直型トランジスタの形成時に、ビットライントレンチの形成工程をを単純化することができる半導体素子及びその製造方法を提供する。

【解決手段】垂直型トランジスタの形成のため、ソース/ドレーン領域に用いられる第1垂直型ピラー120と、チャンネルに用いられる第3垂直型ピラー125と、第1ビットラインインプラント領域140と、第3垂直型ピラー125の側壁を取り囲むサラウンドゲート130とで垂直型トランジスタ150を形成した後、ビットライントレンチの形成のためギャップフィル特性に優れたSOC(Spin On Carbon)膜160を形成する。SOC膜160は低温処理が可能であり、垂直型トランジスタ150に加えるストレスを最小化して倒れ問題を防止することができ、高温アニーリング工程で発生する表面の粗化現象がないので、CMP工程を省略することができる。

(もっと読む)

半導体素子のリセスゲート及びその製造方法

【課題】リセスゲート及びこれを含む半導体素子の製造方法を提供する。

【解決手段】半導体素子のリセスゲートは、基板110と、金属層165と、ポリシリコン層と、ポリシリコン層に隣接し、金属層165から離隔され、形成されたソース領域及びドレーン領域と、を含む。半導体素子の形成方法は、基板110の上にソース/ドレーン120層を形成する段階と、リセス112を形成し、第1導電層パターン145を形成する段階と、第1導電層パターン145上に第2導電層を形成する段階、ソース/ドレーン層120と重畳されるように第2導電層パターン156を形成する段階と、前記第2導電層パターン156と、前記ソース/ドレーン層120上に絶縁層を蒸着する段階と、第2導電層パターン156上にキャップを形成するように絶縁層を平坦化する段階と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子とコンタクトプラグとが高精度で位置合わせされた半導体装置の製造方法を提供する。

【解決手段】半導体基板のエッチング速度が絶縁層2のエッチング速度よりも速くなるように、裏面側から、半導体基板内の突起状領域に対応する位置の異方性エッチングを行い、第1構造体が露出するまで開口2を設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の消費電力が増加してしまうのを抑制することが可能な半導体装置を提供する。

【解決手段】このパワーMOSFET100(半導体装置)は、シリコン基板1に形成され、不純物が導入された埋込ドレイン層2と、埋込ドレイン層2に到達するようにシリコン基板1に形成されるとともに、その内側面に絶縁膜12が形成された溝部11と、溝部11の下端部からさらに下方に突出するように形成された溝部13と、溝部11および溝部13に埋め込まれた導電性部材14とを備えている。また、埋込ドレイン層2と導電性部材14とが接している。

(もっと読む)

半導体素子及びその製造方法

【課題】チャネルが上下方向に形成されるトランジスタアレイ内における各トランジスタの駆動電圧の伝達効率を増大させるための半導体素子及びその製造方法を提供すること。

【解決手段】本発明の半導体素子は、複数の柱パターンと、各々の前記柱パターンを囲むゲート絶縁膜と、各々の前記ゲート絶縁膜を囲み、かつ、隣接する前記ゲート絶縁膜間を連接する導電膜とを備え、該導電膜は、ゲート電極及び配線として機能することを含む。

(もっと読む)

垂直チャネルトランジスタを備える半導体素子の製造方法

【課題】上部ピラーを取り囲むハードマスクパターン及びスペーサの損失を最小化して上部ピラーへのアタックを防止できる垂直チャネルトランジスタを備える半導体素子の製造方法の提供。

【解決手段】上方にハードマスクパターンを有する上部ピラーPa及び下部ピラーPbAを半導体基板上に形成するステップと、下部ピラーを取り囲むサラウンドゲート電極304を形成するステップと、前記ピラー間を埋め込む絶縁膜を形成するステップと、ワードライン形成用マスクパターンを用いて、上部ピラーの一部が露出するまで前記絶縁膜を1次エッチングして初期トレンチを形成するステップと、該初期トレンチを含む結果物の全面にバッファ層309を形成するステップと、前記初期トレンチの底面の前記バッファ層を除去するステップと、前記サラウンドゲート電極が露出するまで前記絶縁膜を2次エッチングして最終トレンチを形成するステップとを含む。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

垂直チャネルトランジスタの製造方法及び半導体素子のピラー製造方法

【課題】エッチング工程を利用しなくとも、垂直チャネルとして作用するピラーを安定的に構築できる垂直チャネルトランジスタの製造方法を提供すること。

【解決手段】本発明の垂直チャネルトランジスタの製造方法は、基板上に犠牲膜22を形成するステップと、犠牲膜22にコンタクトホール23を形成するステップと、コンタクトホール23を埋め込み、犠牲膜22の表面上まで横方向に延長されたピラーを形成するステップと、犠牲膜22を除去するステップと、ピラーの露出した側壁と基板の露出した部分との上にゲート絶縁膜29を形成するステップと、少なくともピラーの露出した側壁上に形成されたゲート絶縁膜29の一部を取り囲むゲート電極30を形成するステップとを含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、設計の自由度が向上され、かつ、ゲート容量の増加を防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体基板1に、第一の導電型の活性領域41、42を形成し、チャネル用シリコン柱4b、4cを含む複数のシリコン柱4a〜4dを形成した後、第二の導電型の第一半導体領域7aを形成する工程と、容量増加防止用絶縁膜10を設けてゲート電位供給用シリコン柱4a、4dを形成する工程と、前記チャネル用シリコン柱4b、4cの周囲にゲート絶縁膜11を設ける工程と、ゲート電位供給用電極12bとゲート電極12aを形成し、接続する工程と、第一層間絶縁膜13を形成する工程と、前記チャネル用シリコン柱4bの高さを低くする工程と、第二の導電型の第二半導体領域7bを形成する工程と、を有する半導体装置100の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

集積回路の製造方法

【課題】異なる基材領域又はいくつかのトレンチの底部及び各側壁部を覆う異なる酸化被膜の形成に異なる酸化処理を備える、集積回路を製造する方法を提供する。

【解決手段】表面を有する半導体基板10を準備するステップと、少なくとも一つの注入種が、前記表面の第二の部分区域14と比較すると前記表面の第一の部分区域12に近接して特に注入されるようなイオン注入処理を実行するステップと、前記表面の前記第一の部分区域を覆う第一の膜厚を有する第一の酸化被膜32と前記表面の前記第二の部分区域を覆う第二の膜厚を有する第二の酸化被膜36とを形成するように、単一の酸化処理を実行するステップであって、前記第一の膜厚が前記第二の膜厚と異なるステップと、を備える。

(もっと読む)

垂直型及び水平型ゲートを有する半導体素子及び製造方法

【課題】垂直型及び水平型ゲートを有する半導体素子及び製造方法を提供する。

【解決手段】本発明のある態様の半導体素子は、高濃度第1導電型の半導体基板と、前記半導体基板上に形成された低濃度第1導電型のエピタキシャル層と、前記エピタキシャル層の所定領域に互いに隔たって形成された複数個の第2導電型のベース領域と、一方の側の端部または両側端部の前記ベース領域を除く前記各ベース領域内に形成された複数個の高濃度第1導電型のソース領域と、前記各ベース領域間の前記エピタキシャル層に形成された複数個の高濃度第1導電型のドレイン領域と、前記各ソース領域とベース領域を貫通して形成される複数個のトレンチと、前記各トレンチ内に形成された第1ゲート電極と、前記各ドレイン領域と前記ベース領域間に形成されるフィールド酸化膜と、前記各ソースと前記ドレイン領域間の前記ベース領域上に形成される複数個の第2ゲート電極と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 装置規模の拡大を最小限に抑制しながら、高い耐圧性を維持するとともに、現実的な製造プロセスの下で容易に製造が可能な半導体装置を提供する。

【解決手段】 第1絶縁膜3aを貫通するように基板面に直交する深さ方向に形成される導電膜14aと、第2絶縁膜3bの直上層から底面に達するまで一の外側壁に沿って深さ方向に形成される導電膜14bと、導電膜14bの底面の深さ位置から絶縁膜3a及び3bに挟まれた領域に係る基板2の上面位置に亘って、少なくとも導電膜14bの底面及び絶縁膜3bと接触していない側の外側壁と接触して形成される絶縁膜13bと、絶縁膜13bと3bに挟まれた領域内において底面から上面に向かって、第1導電型の第1不純物拡散領域6、第2導電型の第2不純物拡散領域5a、第1導電型の第3不純物拡散領域7、及び高濃度の前記第1導電型の第4不純物拡散領域17bを備える。

(もっと読む)

半導体装置及びその製造方法並びにデータ処理システム

【課題】トレンチゲート型トランジスタのサブスレショルド特性の向上を図りつつ、ゲートトレンチの幅が縮小された高性能な半導体装置を提供する。

【解決手段】ゲートトレンチ16の底部16bは、STI14から相対的に遠い第1の底部16b1と、STI14から相対的に近い第2の底部16b2を有している。そして、活性領域10aのうち、ゲートトレンチの第2の底部16b2を構成する部分は、側壁チャネル領域10dを構成し、ゲート電極18とSTI14との間に挟まれた薄膜SOI構造を有している。一方、ゲートトレンチの第1の底部16b1を構成する部分は、副チャネル領域10eとして機能する。第2の底部16b2の曲率半径は第1の底部16b1の曲率半径よりも大きい。ゲートトレンチ16の幅方向の略中央部分においては、トレンチの底面が略平坦であるのに対し、幅方向の端部においては、トレンチの底面がほぼ全体的に湾曲している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート−ソース間耐圧の向上を図る。

【解決手段】N型のエピタキシャル層6の表層部には、P型のボディ領域10が形成されている。エピタキシャル層6には、その表面から掘り下がったトレンチ11が、ボディ領域10を貫通して形成されている。ボディ領域10の表層部において、トレンチ11の側方には、N+型のソース領域12が形成されている。トレンチ11の底面および側面には、ゲート絶縁膜14が形成され、このゲート絶縁膜14を介して、トレンチ11にゲート電極15が埋設されている。ゲート電極15の表面は、ソース領域12の表面よりも一段低く形成されている。ゲート電極15の表面の周縁部上には、トレンチ11の側面の上端部に対向する周壁膜16が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型絶縁ゲート型電界効果トランジスタのソースコンタクト抵抗を低減する。

【解決手段】半導体装置40では、半導体基板1の上部に、第1のソース層2aが設けられ、第1のソース層2a内に第1のソース層2aより深く、凹部3を有する第2のソース層2bが設けられる。凹部3上には、積層された第1の層間絶縁膜4a、ゲート電極膜5、及び第2の層間絶縁膜4bを貫通するようにゲート開口部が設けられる。側面にゲート絶縁膜6が設けられたゲート開口部には、第3のソース層2c、チャネル部7、及びドレイン層8が積層埋設される。第3のソース層2cは、下部が第2のソース層2bと接するように、凹部3上及びゲート開口部に埋設される。第1の層間絶縁膜4aと凹部3の間に突起状のゲート絶縁膜凸部6aが設けられる。

(もっと読む)

トレンチゲート型トランジスタ及びその製造方法

【課題】トレンチゲート型トランジスタにおいて、ゲート容量の低減、結晶欠陥の発生の抑止、及びゲート耐圧の向上を図る。

【解決手段】N−型半導体層12にトレンチ14を形成する。トレンチ14において、底部及びその近傍には、角部12A,12Bで丸みを帯びて均一に厚いシリコン酸化膜15Aが形成される。一方、トレンチ14の側壁の上方には、シリコン酸化膜15Aよりも薄く、角部12C,12Dで丸みを帯びたシリコン酸化膜15Bが形成される。さらに、トレンチ14内から外側に延びるゲート電極18が形成される。厚いシリコン酸化膜15Aによりゲート容量が低減され、その上方の薄いシリコン酸化膜15Bにより優れたトランジスタ特性が確保される。また、角部12A,12Bの丸みにより、結晶欠陥が発生しにくくなると共に、ゲート電界が分散されてゲート耐圧が向上する。

(もっと読む)

トレンチゲート型トランジスタ及びその製造方法

【課題】トレンチゲート型トランジスタにおいて、ゲートリーク電流の発生を防止すると共に、ゲート容量を低減する。

【解決手段】トレンチ17内には、ゲート酸化膜13Bが形成され、トレンチ17の端部にゲート酸化膜13Bと接してトレンチ酸化膜16が形成されている。トレンチ酸化膜16は、ゲート酸化膜13Bより厚い膜厚を有している。トレンチ17内には、ゲート酸化膜13Bを覆って、ゲート電極18が形成されている。また、N−型半導体層12の表面には、トレンチ17の側壁のゲート酸化膜13Bに接してボディ層19が形成されている。このように、ゲート電極18のトレンチ17の引き出し部18Sに、厚いトレンチ酸化膜16を形成したので、ゲートリーク電流の発生を防止すると共に、ゲート容量を低減することができる。

(もっと読む)

半導体装置、半導体装置の製造方法並びにデータ処理システム

【課題】完全空乏化型のトランジスタ特性を維持しつつ、良好なS値と大きなドレイン電流が得られる縦型SGT構造を有する半導体装置を提供する。

【解決手段】本発明の半導体装置は、完全空乏化が可能な太さに形成された複数の半導体の基柱5と、複数の基柱5の各々の外周面に設けられたゲート絶縁膜10と、複数の基柱5の隙間を埋めて複数の基柱5の各々の外周面を覆うゲート電極11と、を備えていることを特徴とする。

(もっと読む)

半導体装置

【課題】縦型MOSトランジスタが密集するアレイ部において、設計自由度の高いゲート電極への電位供給手段を有した半導体装置を提供する。

【解決手段】第1の導電型のゲート電極(2)を共有した複数の角柱縦型MOSトランジスタを有する半導体装置であって、角柱縦型MOSトランジスタが第1の角柱(3,4,5)の周りに形成されたゲート絶縁膜(18)を介して前記ゲート電極と対峙して成り、該ゲート電極への電位供給(6)を、前記第1の角柱と同時に形成され、かつ、ゲート電極の導電型と同じ第1の導電型であり、少なくとも一部分のゲート絶縁膜を除去した部分で前記ゲート電極に接している第2の柱(8)を介して行う。

(もっと読む)

141 - 160 / 285

[ Back to top ]