Fターム[5F140BB04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSVC(垂直表面垂直電流) (285)

Fターム[5F140BB04]に分類される特許

201 - 220 / 285

半導体装置

【課題】ディスクリート半導体のチップにおいて、電流経路上の第1電極および第2電極を、半導体基板の第1主面側に設け、フリップチップ実装を可能にしたものが知られている。しかし、基板内を水平方向にも電流が流れるため、基板が矩形の場合には水平方向の電流経路が増加し、抵抗が増加する問題があった。

【解決手段】基板内の水平方向の電流経路を、基板(チップ)の短辺に沿った方向に形成する。例えば、入力端子側となる素子領域と、出力端子側となる電流の取りだし領域を、チップの短辺に沿って並べるレイアウトを採用する。更に、入出力端子にそれぞれ接続する第1バンプ電極および第2バンプ電極を設け、これらをチップの短辺に沿って配置する。これにより、基板内の水平方向の電流経路はその幅が広く長さが短く形成されるので、基板の水平方向の抵抗を低減することができる。

(もっと読む)

ヘテロ構造を有する細長い単結晶ナノ構造に基づくトンネル効果トランジスタ

【課題】トンネル電界効果トランジスタ(TFET)は、金属酸化物電界効果トランジスタ(MOSFET)の後継者と考えられるが、シリコンベースのTFETは一般に低いオン電圧、トンネルバリアの大きな抵抗による欠点が問題となる。より高いオン電流を得るために、異なった半導体材料(例えばゲルマニウム(Ge))からなるヘテロ構造を備えた細長い単結晶ナノ構造ベースのTFETが用いられる。

【解決手段】TFETのソース(又は代わりにドレイン)領域として機能する、異なった半導体材料からなる細長い単結晶ナノ構造を導入する。ヘテロ部分の導入は、シリコンとゲルマニウムの間の格子不整合が高い欠陥界面とならないように行われる。従来のMOSFETに匹敵する、静的電力の低減と同様に動的電力の低減が行われる。細長い単結晶ナノ構造のSi/GeTFETによる超高密度オンチップトランジスタを用いた、多層の論理が期待される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

集積化トランジスタ素子及びその形成方法

【課題】集積化トランジスタ素子を提供する。

【解決手段】集積化トランジスタ素子は半導体基板1と;前記半導体基板に形成されるピラー1aと;前記ピラー1aを取り囲むゲートトレンチと;前記ピラー1aの上部領域に形成される第1ソース/ドレイン領域D1、Sと;前記ゲートトレンチの底面の上に形成され、かつ前記ピラーIaの下部領域を取り囲むゲート誘電体40と;前記ゲートトレンチ内の前記ゲート誘電体の上に形成され、かつ前記ピラーの下部領域を取り囲むゲート50と;そして前記ゲートトレンチに隣接する前記半導体基板1の上部領域に形成される少なくとも一つの第2ソース/ドレイン領域と、を備える。

(もっと読む)

半導体装置

【課題】トレンチ構造を有する半導体装置において、トレンチの終端コーナー部への電界集中を防ぎ、それによってデバイスの耐圧低下を防止すること。

【解決手段】交差する複数のトレンチ63,64のうち、最外周のトレンチ64の幅はその内側のトレンチ63の幅よりも狭いこと、また、最外周のトレンチ64はその内側のトレンチ63よりも浅いこと、それによって、トレンチ終端コーナー部におけるゲート酸化膜やゲート電極の特異点をなくし、トレンチ終端コーナー部への電界集中を緩和するか、またはなくし、トレンチ終端コーナー部での耐圧低下を防止する。

(もっと読む)

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

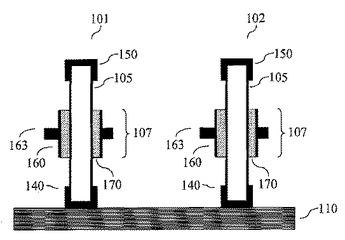

垂直型電界効果トランジスタ・アレイ及びその製造方法

【課題】 性能が向上した垂直型電界効果トランジスタ・アレイを提供すること。

【解決手段】 垂直型電界効果トランジスタの半導体構造体、及び垂直型電界効果トランジスタの半導体構造体を製造する方法が、半導体ピラーのアレイを提供する。半導体ピラー・アレイ内の各半導体ピラーの各垂直部分は、隣接する半導体ピラーまでの分離距離より広い線幅を有する。代替的に、アレイは、随意的に上記の線幅及び分離距離の制限の中で、異なる線幅を有する半導体ピラーを含むことができる。半導体ピラーのアレイを製造する方法は、エッチング・マスクとして用いられる前に少なくとも1つのスペーサ層が環状に増大される、フォトリソグラフィを用いて最小寸法に作られたピラー・マスク層を用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極間の寸法を低減し得る半導体装置を提供する。

【解決手段】半導体装置は、半導体基板(5)と、半導体基板(5)に埋設された複数のゲート電極11a〜11cと、複数のゲート電極11a〜11cの各々の上に設けられた第1の絶縁層(12a〜12c)と、半導体基板(5)の表面に形成された導電層(13)と、導電層(13)上に設けられた導体層15とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型トランジスタのカットオフ時のリーク電流を低減する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板と前記半導体基板の内部に形成された第1の不純物拡散領域と前記第1の不純物拡散領域の上方に形成された柱状半導体層と前記柱状半導体層の側方に形成されたゲート絶縁膜と前記ゲート絶縁膜の側方に形成されたゲート電極と前記不純物拡散領域の上方で前記ゲート電極に接して形成された絶縁体からなる層間膜と前記柱状半導体層の上方で前記ゲート電極に接して形成された絶縁体からなるスペーサと前記柱状半導体層の上方に形成された第2の不純物拡散領域とを具備し前記柱状半導体層の略中央に絶縁膜を有する。

(もっと読む)

ダイレクトトレンチポリシリコンコンタクトを備える横型トレンチMOSFETおよびその形成方法

横型トレンチMOSFETは、装置セグメントとゲートバスセグメントとを含むトレンチを備える。トレンチのゲートバスセグメントは、基板を覆って存在する誘電体層に形成される導電性プラグによってコンタクトされ、これにより従来の表面ポリシリコンブリッジ層が不要となる。導電性プラグは、誘電体層にある実質的に垂直な穴に形成される。ゲートバスセグメントは、トレンチの装置セグメントよりも幅が広くてもよい。この方法は、トレンチ中の導電性材料がエッチングされる間にシャロートレンチアイソレーション(STI)を形成するステップを含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置において半導体素子間の分離を好適に達成するとともに半導体装置の小型化を図ること。

【解決手段】半導体基板1と、半導体基板1上に形成されたエピタキシャル層2と、半導体基板1とエピタキシャル層2との間に形成された埋め込み層3と、エピタキシャル層2表面から埋め込み層3に達する第1のトレンチ7と、第1のトレンチ7内に埋め込まれるとともに埋め込み層3と接続されたドレイン取出電極8bと、ドレイン取出電極8bを電極とした半導体素子と、エピタキシャル層2表面からその半導体素子を囲むように設けられた第2のトレンチ5とを備え、第2のトレンチ5内の少なくとも側壁を絶縁膜6aで被覆した。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電流の局所集中による半導体基板への部分放電を抑制し得る半導体装置を提供する。

【解決手段】半導体装置は、半導体基板(1,5)と、半導体基板(1,5)に埋め込まれたゲート電極(9A,9B)と、ゲート電極(9A,9B)の更に内側に埋め込まれた導電体(15A,15B)と、導電体(15A,15B)と接続されるように半導体基板(1,5)の内部に形成された配線層(3)と、ゲート電極(9A,9B)と導電体(15A,15B)との間に配置された絶縁膜(14)とを備える。導電体(15A,15B)は、半導体基板(1,5)の表面よりも高くなるように形成されている。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域の構造を最適化することにより、高いIon/Ioff比を達成する電界効果トランジスタを含む半導体装置を提供する。

【解決手段】第1のゲート電極107と第2のゲート電極108は、チャネル領域101の両側に対向するように、第1のゲート絶縁膜103と第2のゲート絶縁膜104を介して、それぞれ形成され、ソース領域111および前記ドレイン領域121は、第1のゲート電極107と第2のゲート電極108の両側に、チャネル領域101を挟んで形成され、第1のゲート絶縁膜103とチャネル領域104との界面に垂直な方向のソース領域111の厚さ(TSis)が、同じ方向のチャネル領域101の厚さ(TSic)よりも厚く、かつ、ソース領域111と、第1、第2のゲート電極107、108が、ゲート長方向に離間している電界効果トランジスタを含む半導体装置。

(もっと読む)

III族窒化物半導体を用いたノーマリオフ型電界効果トランジスタ及びその製造方法

【課題】ゲート電圧の閾値を従来よりも高くするとともに、所望の閾値電圧とすることができるIII族窒化物半導体を用いたノーマリオフ型電界効果トランジスタを提供する。

【解決手段】アクセプタとドナーを含んで成長されたIII族窒化物半導体層3と、III族窒化物半導体層3上に形成されてそのアクセプタの濃度とドナーの濃度に基づいて所定の閾値電圧となる厚さに制御されたゲート絶縁膜5と、ゲート絶縁膜5上に形成されたゲート電極8と、ゲート電極8の一側方に間隔をおいてチャネル層3上に形成されたソース電極6と、ゲート電極8から他側方に間隔をおいてチャネル層3の上に形成されたドレイン電極7とを有し、閾値電圧を高くする。

(もっと読む)

集積回路装置およびその製造方法

【課題】トランジスタの浮遊ボディ効果が避けられ、且つ高密度な集積回路装置を提供。

【解決手段】縦型MOSトランジスタにおいて、第1導電型の基板1上に配置された一連の層SF、SF*を備え、前記一連の層は、第1のソース・ドレイン領域用の下層U、第1導電型でドープされ、チャンネル領域となる中間層Mおよび第2のソース・ドレイン領域用の上層Oからなる。第1導電型でドープされた接続構造体Vが、チャンネル領域を基板1と電気的に接続するために前記一連の層SF、SF*の第1の表面上に配置される。トランジスタのゲート電極が、前記一連の層SF、SF*の第2の表面上に配置される。接続構造体Vは、一連の層SF、SF*と、同一の又は別の一連の層SF、SF*との間に配置できる。接続構造体V等の寸法は、リソグラフィ寸法以下となり得る。製作された回路は、記憶セル配列に好適。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタに用いられる多結晶シリコン膜のみならず、多結晶質の膜からなるゲート電極を形成する工程において、当該ゲート電極に発生する結晶粒を容易に評価することのできる検査技術を提供する。

【解決手段】半導体基板の主面上に形成された多結晶シリコン膜の表面を原子間力顕微鏡を用いてプローブ走査し、入力信号と出力信号との位相遅延を測定することによって得られた位相遅延を濃淡の位相モード像で表した後、位相モード像を画像処理して多結晶シリコン膜のシリコン結晶粒13の大きさを算出する。得られたシリコン結晶粒13の大きさから、多結晶シリコン膜を加工して形成されるゲート電極のライン端ラフネスまたはライン幅ラフネスを評価する。

(もっと読む)

埋め込みビットラインの形成方法

【課題】選択的無電解蒸着法を利用した埋め込みビットラインの形成方法を提供する。

【解決手段】埋め込みビットラインの形成方法は、基板をエッチングして形成されたビットライン用溝に無電解金属層を選択的に形成し、シリサイド工程を行ってビットライン用溝の内部にシリサイド膜を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トレンチ横型パワーMOSFETにおいて、装置の信頼性を高めること。

【解決手段】半導体基板1の表面層にトレンチ5を形成する。トレンチ5は、半導体基板1の表面層を第1メサ領域41と第2メサ領域42に分割し、かつ第1メサ領域41と第2メサ領域42を交互に配置させる。第1メサ領域41および第2メサ領域42は、それぞれソース電流およびドレイン電流の引き出しをおこなう。第2メサ領域42は、半導体基板1からの深さが、第1メサ領域41よりも深くなっている。

(もっと読む)

高圧バイポーラCMOS−DMOS集積回路装置およびこれを形成するためのモジュール式方法

エピタキシャル層を含まない基板においてさまざまな半導体装置を製造するために全低温プロセスが用いられる。装置は分離されていないラテラルDMOS、分離されていない拡張されたドレインまたはドリフトされたMOS装置、ラテラルトレンチDMOS、分離されたラテラルDMOS、JFETおよび空乏モード装置、ならびにP−Nダイオードクランプおよびレクチファイヤおよび接合端子を含む。プロセスが高温処理の必要をなくし、「注入されたままの」ドーパントプロファイルを使用するので、残りの装置を生成するのに使用されるプロセスを変更する必要なしに、装置がICに加えられたり省略されたりすることを可能にするモジュール式アーキテクチャを構成する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】TLPMと保護素子を集積すること。TLPMとともに保護素子を作製すること。

【解決手段】複数のトレンチ5により、p型半導体基板1上のn型ウェル領域2aの表面層を、第1メサ領域33、第2メサ領域34および第3メサ領域35に分割する。第1メサ領域33、第2メサ領域34および第3メサ領域35に、それぞれn型ソース領域7、n型ドレイン領域6およびp型コレクタ領域4bを設ける。n型ウェル領域2a内で、トレンチ5の底面にn型拡張ドレイン領域3a,3bを設ける。n型ソース領域7とn型拡張ドレイン領域3bの間にp型チャネル領域4aを設ける。このような構造により、コレクタ電極9bとソース電極10の間に、p型コレクタ領域4bと、n型ウェル領域2aおよびn型拡張ドレイン領域3bと、p型チャネル領域4aと、n型ソース領域7からなるPNPNサイリスタ構造の保護素子を設ける。

(もっと読む)

201 - 220 / 285

[ Back to top ]