Fターム[5F140BB04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSVC(垂直表面垂直電流) (285)

Fターム[5F140BB04]に分類される特許

61 - 80 / 285

半導体装置および半導体装置の製造方法

【課題】ピラー型MOSトランジスタに関し、チャネルがフローティング状態になることを防止できる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置200は、基板11に立設された、トランジスタ用の第一のピラー1と、前記第一のピラー1に隣接された、前記第一のピラー1のチャネル16と同じ導電型の連結部14と、前記第一のピラー1に連結部14を介して隣接された、前記チャネル16と同じ導電型の、前記第一のピラー1のチャネル16電位制御用の第二のピラー2と、を有し、前記第二のピラー2上面に、電位を与える構造を有することを特徴とする。

(もっと読む)

窒化物半導体素子

【課題】ゲート絶縁膜の絶縁破壊を抑制または防止できる構造を有する窒化物半導体素子を提供する。

【解決手段】電界効果トランジスタ1(窒化物半導体素子)は、窒化物半導体の積層構造部3と、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、ガードリング層11とを含む。積層構造部3は、n型GaN層4,5、p型GaN層6およびn型GaN層7を積層して構成されている。ゲート絶縁膜15は、n型GaN層5、p型GaN層6およびn型GaN層7に跨るように、積層構造部3の壁面9に形成されている。ゲート電極16は、ゲート絶縁膜15を挟んでp型GaN層6に対向している。ガードリング層11は、p型GaN層6における壁面9に間隔を開けて対向するようにn型GaN層5上に形成されたp型GaN層からなる。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを備えた半導体装置において、トランジスタのGIDLを抑制する。

【解決手段】縦型トランジスタを備えた半導体装置に関する。縦型トランジスタは、半導体領域と、半導体領域上に設けられた柱状領域と、柱状領域の側面を覆うように設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、柱状領域の上部に設けられた第1の不純物拡散領域と、半導体領域内に柱状領域を囲むように設けられた第2の不純物拡散領域と、を有する。第1の不純物拡散領域は、柱状領域の側面と離間するように設けられている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

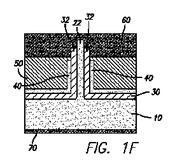

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

半導体装置、半導体チップ及び半導体装置の製造方法

【課題】製造工程中にピラー径の変動が小さいピラー型MOSトランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板対して垂直に立設する第1のピラー及び第2のピラーの側面にゲート絶縁膜を介して形成されたゲート電極と、第1のピラーの先端部及び基端周囲領域に形成された上部拡散層及び下部拡散層と、を備え、第2のピラーのゲート電極と隣接する第1のピラーのゲート電極とは接続されており、第1のピラーのゲート電極には第2のピラーのゲート電極を介して電位が供給され、第1のピラーと、該第1のピラーに隣接する第2のピラーの少なくとも一部とは平面視して、第1のピラー及び第2のピラーの側面を構成する面のうち、熱酸化速度及び/又はエッチング速度が最大の面に対して45°の方向に沿って配置されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ内に形成されたビット線の底面からのリーク電流を低減する。また、トレンチのアスペクト比を大きく増加させることなく、その後の工程でトレンチ内の空間に安定して成膜して、高アスペクト比による加工性の低下といった問題が生じない半導体装置を提供する。

【解決手段】半導体基板内にトレンチを形成する。このトレンチ内壁の底面上に第一の絶縁膜を形成する。また、トレンチ内壁の側面上に熱酸化により第一の絶縁膜よりも膜厚が薄い第二の絶縁膜を形成する。トレンチ内の第一の絶縁膜上に、ビット線を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置及びデータ処理システム

【課題】第1配線の比抵抗が小さく、シリサイド異常成長が抑制された半導体装置の製造方法の提供。

【解決手段】第1溝を半導体基板1に設けた後、第1溝内に、シリコンとの間でシリサイドを形成しない材料からなる導体層6と半導体層10とを含む第1配線11を形成して、半導体層と半導体基板とを直接に接触させる工程と、半導体層に含まれるドーパントを半導体基板に拡散させて第1不純物拡散領域13を形成する工程と、第1溝と交差する方向に延在する第2溝を半導体基板に設けることで、第1不純物拡散領域を包含して半導体基板に立設されたピラー部1bを形成する工程と、第2溝の側壁面にゲート絶縁膜16を形成してから、ゲート絶縁膜を介してピラー部に対向する第2配線17を第2溝内に形成する工程と、ピラー部の先端部に、第2不純物拡散領域19を形成する工程と、を具備してなる半導体装置の製造方法を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

半導体装置およびその製造方法

【課題】拡散層と拡散層に接続されるコンタクトとの接触抵抗を低減した半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置の製造方法は半導体基板にピラー部を設ける工程と、前記ピラー部の基端部近傍に第1の不純物拡散領域を形成する工程と、ピラー部の側面を被覆する第1の絶縁膜を形成するとともに、第1の絶縁膜を介してピラー部の側面に対向する電極層を形成する工程と、ピラー部及び第1の絶縁膜の周囲を埋める第2の絶縁膜を形成する工程と、第1の層間膜を除去して前記ピラー部の先端面を露出させる工程と、ピラー部の先端部に第2の不純物拡散領域を形成する工程と、第1の絶縁膜をエッチングして前記ピラー部の先端部の側面を露出させる工程と、ピラー部の先端面及びピラー部の先端部の側面を覆うようにコンタクトプラグを形成する工程と、を具備してなる。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】同一半導体チップ内に形成されたNチャネルパワーTDMOSトランジスタとPチャネルパワーTDMOSトランジスタの双方のオン電流に対するオン抵抗の低減を図る。

【解決手段】NチャネルパワーTDMOSトランジスタ用トレンチ4の長辺側とPチャネルTDMOSトランジスタ用トレンチ4の長辺側を45°傾けて形成する。これによりNチャネル側のトレンチ4の長辺側の側壁を(100)面とし、Pチャネル側のトレンチ4の長辺側の側壁を(110)面として、Nチャネル側の電流担体である電子及びPチャネル側の電流担体である正孔の移動度を高くする。移動度を高くすることによりチャネル部分の導電率を高める。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】微細なトレンチを採用するトレンチDMOSFETにおいて、ドレイン−ソース間の絶縁破壊電圧を高くするため、低濃度のドリフト層の形成領域を如何に確保するかが課題となる。

【解決手段】TNDMOS形成のためのトレンチT1の底部のN型ウエル層2の表面から内部に延在し、P型ボディ層3と接続するN型埋め込みドリフト層5を形成する。次にトレンチT1の両側壁にゲート電極7a、スペーサー8aを重畳して形成する。次に、ゲート電極7a及びスペーサー8aをマスクとしてリン等をイオン注入しN型埋め込みドリフト層5内にN+型ドレイン層11を形成する。これによりN+型ドリフト層11からP型ボディ層3底部まで延在する低濃度のN型埋め込みドリフト層5を確保する。なお、N+型ドレイン層11を形成しないで、トレンチT1の両側壁に、N型埋め込みドリフト層5を共通のドレイン層とする2つのTDMOSを形成しても良い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

パンチスルーアクセスを有する縦型不揮発性スイッチおよびその製造方法

不揮発性メモリセルにアクセスするための半導体装置が提供される。いくつかの実施形態においては、半導体装置は、ソース、ドレインおよびウェルを含む半導体層の縦型スタックを有する。半導体装置へのドレイン−ソースバイアス電圧の印加は、ウェルにわたってパンチスルー機構を生成し、ソースとドレインとの間の電流の流れを発生させる。  (もっと読む)

(もっと読む)

半導体装置

【課題】長い直線状のトレンチ1内に、ゲート絶縁膜17を介して第1ゲート電極2等を有するTDMOSトランジスタについて、増大するゲート抵抗と寄生容量に基づくゲート遅延の問題を、ゲート絶縁膜17に損傷を与えることなく改善する。

【解決手段】トレンチ1の側壁に、第1ゲート電極2等の材料となるポリシリコン膜22の膜厚の2倍未満の幅と奥行きからなるトレンチ凸部1aを形成する。トレンチ凸部1aはポリシリコン膜22で埋め込まれるのでその表面に形成された層間絶縁膜19に、トレンチ凸部1a部分のポリシリコンのみが露出する第1ゲートコンタクト4等を形成する。該第1ゲートコンタクト4等と接続する第1ゲート配線電極G1等を一定間隔の元、複数本形成する。

(もっと読む)

シャロートレンチアイソレーションプロセス

【課題】トレンチ構造の歪み導入要素によりに歪み導入されたチャネルを持つMOSトランジスタのリーク電流を改善する。

【解決手段】MOSトランジスタ106のチャネル領域108に、第1トレンチ構造55a、第2トレンチ構造55bによる歪み導入要素だけでなく、別の歪み導入要素として、MOSトランジスタ106表面上にコンフォーマルに設けられた窒化シリコンキャップ層130を設ける。別の態様では、チャネル領域108内の歪みは、ガス種、例えば水素、酸素、ヘリウムまたは別の希ガスをゲート110またはチャネル領域108の下の領域内に注入することによって導入される。

(もっと読む)

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られるデバイス

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られる電子構造体について記載する。こうした構造体は、金属−酸化物−半導体(MOS)構造を含むことができ、構造体はMOS電界効果トランジスタ(MOSFET)または光電子スイッチに用いることができる。  (もっと読む)

(もっと読む)

61 - 80 / 285

[ Back to top ]