Fターム[5F140BB04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901) | 段差部に形成されたもの (818) | VSVC(垂直表面垂直電流) (285)

Fターム[5F140BB04]に分類される特許

81 - 100 / 285

半導体装置および半導体装置の製造方法

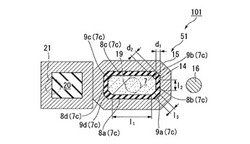

【課題】突出部の側面が凹凸状とされ、前記側面を覆うようにゲート酸化膜を形成したときに、実効的なチャネル長が増加して、ピラー型MOSトランジスタの電流駆動能力が低下するという課題があった。

【解決手段】基板と、前記基板の一面から垂直方向に突出された突出部7とを備え、突出部7の先端側の上部拡散層と、基端側の下部拡散層と、側面7cを覆うゲート絶縁膜14と、ゲート絶縁膜14を覆うゲート電極15と、を有し、チャネルが前記垂直方向となるピラー型MOSトランジスタ51を具備し、突出部7が平面視八角形状であり、突出部7の側面7cが{100}面からなる4つの主表面8a、8b、8c、8dと、{110}面および{111}面からなり、前記主表面8a、8b、8c、8dよりも面積が小さい4つの副表面9a、9b、9c、9dとからなる半導体装置101を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体記憶装置

【課題】縦型トランジスタSGTで構成されたCMOS型6T−SRAMにおいて、小さいSRAMセル面積と安定した動作マージンを実現する。

【解決手段】6個のMOSトランジスタを用いて構成されたスタティック型メモリセルにおいて、前記メモリセルを構成するMOSトランジスタは、基板上に形成され、ドレイン、ゲート、ソースが垂直方向に配置され、ゲートが柱状半導体層を取り囲む構造を有し、前記基板は第1の導電型を持つ第1の活性領域と第2の導電型を持つ第2の活性領域からなり、それらが基板表面に形成されたシリサイド層を通して互いに接続されることにより小さい面積のSRAMセルを実現する。また、基板上に配置される第1のウェルと同一の導電型を持つドレイン拡散層のそれぞれを第1のウェルと反対の導電型を持ち、第1のウェルより浅い第2のウェル及び第3のウェルで囲むことにより、基板へのリークを抑制する。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

半導体装置

【目的】ゲート酸化膜の薄膜化が生じないようにして、ゲート耐圧の低下を防止することこができる半導体装置を提供する。

【解決手段】閉ループで蛇行した1条の第1トレンチ3と、この第1トレンチ3を囲む閉ループの第2トレンチ25と、第1トレンチ3と第2トレンチ25を接続する第3トレンチ71と、第1トレンチ3の曲線部とこれに対向する直線部を接続する第4トレンチ72とをそれぞれ形成し、第3トレンチ71に第1ゲートポリシリコン配線19、第4トレンチ72に第2ゲートポリシリコン配線20を形成する。第1、第2ゲートポリシリコン配線19、20を形成する第3、第4トレンチ71、72にトレンチ終端部がないために、第1、第2ゲートポリシリコン配線19,20下のゲート絶縁膜10が薄くならずゲート耐圧の低下を防止できる。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

非平面な基板表面を有する基板を処理する方法

非平面的な表面を有する基板を共形的に処理する技術を開示する。この技術は、複数の段階を備える。第1段階では、基板の幾つかの面が効果的に処理される。第2段階では、これらの面が更に処理されるのを防ぐ又は制限するべく処理が行われる。第3段階では、基板のその他の面が処理される。ある適用例では、第1段階及び第2段階において、粒子の流れに垂直又は実質的に垂直な面が処理され、その他の面は、第3段階において処理される。ある実施形態では、第2段階は、基板への膜の堆積工程を含む。 (もっと読む)

半導体装置およびその製造方法

【課題】ウェル電位固定用のウェル給電用素子を設ける際に、縦型MOSトランジスタ間に素子分離用の埋込絶縁層を必要とせず、素子分離用の埋込絶縁層の形成に必要な面積を削減して、半導体装置の高集積化を図る。

【解決手段】半導体基板1に形成された第1導電型のウェル2内に、ウェル給電用素子Xと縦型MOSトランジスタYとが備えられ、ウェル給電用素子Xは、ウェル2と同じ導電型のボディ領域からなるピラー部P1を有し、ピラー部P1の上部には、第1導電型のウェル2の濃度よりも高い濃度を有する第1導電型の第1不純物拡散層13を備え、縦型MOSトランジスタYは、ウェル2と同じ導電型のボディ領域からなるピラー部P2を有し、かつ縦型MOSトランジスタYのピラー部P2の上部には、第2導電型の第2不純物拡散層7を備えることを特徴とする半導体装置を採用する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】柱状部の密度が疎な領域でも基板の主面をエッチングすることなく、ゲート電極の加工を行って、トランジスタ特性を安定に保つ半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】主面1aを有し、半導体材料からなる基板1と、基板1の主面1aに設けられ、主面1aに対して略垂直方向に伸長した形状を有する、前記半導体材料からなる柱状部2と、柱状部2の側面2cに形成された第1の絶縁膜6と、前記基板1の主面1aに形成され、第1の絶縁膜6の膜厚より少なくとも膜厚が厚い厚膜部を有する第2の絶縁膜16と、第1の絶縁膜6および第2の絶縁膜16の上に設けられ、前記柱状部2の側面2cから基板1の主面1aにかけて形成された導電層15と、を備える半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラー型SGTを複数並列に接続する際に、配線層を設ける必要のない半導体装置を提供する。

【解決手段】3Dピラー型SGTの上部主電極領域が選択エピタキシャル成長半導体層を含み、少なくとも2つの隣接する3Dピラー型SGTを、各々の選択エピタキシャル成長半導体層を接触させて並列接続する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極材料のエッチバックが不均一であっても、縦型MOSトランジスタのゲート長のばらつきを小さくして、トランジスタ特性のばらつきを小さくした半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】半導体基板10と、半導体基板10から突出され、先端側に大径部31が設けられ、大径部31の基端側に小径部33が設けられ、かつ、大径部31の周端面31cよりも小径部33の周端面1cが後退されて段部1dが設けられたピラー部1と、ピラー部1の周端面1cに備えられた第1の絶縁膜2と、第1の絶縁膜2を介して少なくとも一部が段部1dに埋められた電極部3と、ピラー部1の基端側および先端側に設けられた不純物拡散領域15、16と、を具備し、電極部3の段部1dに埋められた部分の高さが、ピラー部1の全周に渡って均一の高さとされている半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

垂直置換ゲートトランジスタと集積可能な容量の構造及び作製法

【課題】垂直MOSFETデバイス及び容量に関連したプロセス及び構成を提供する。

【解決手段】半導体デバイスは半導体材料の第1の層と、第1の層中に形成された第1のソース/ドレイン領域を有する電界効果トランジスタを含む。チャネル領域は、第1の層上に形成され、第2のソース/ドレイン領域235はチャネル領域上に形成される。集積回路構造は底部プレート266、誘電体層258及び最上部容量プレート259を有する容量を更に含む。作製方法において、電界効果トランジスタのソース領域及びドレイン領域から成るグループから選択された第1のデバイス領域が、半導体層上に形成される。第1の電界効果トランジスタゲート領域265が、第1のデバイス領域上に形成される。間にはさまれた誘電体層を有する最上部及び底部層も、半導体層上に形成される。別の実施例において、容量層は半導体層中に形成された溝又は窓内に形成される。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

半導体装置、および該半導体装置の製造方法

【課題】半導体装置の製造方法においてゲート酸化膜厚のばらつきを抑えてシリコン柱を細くする。

【解決手段】基板10上にシリコン柱11を形成する第1の工程と、シリコン柱11の側面の上端部および下端部を覆う保護膜を形成する第2の工程と、第2の工程の後、シリコン柱11の側面の保護膜で覆われていない部分に異方性エッチングにてくびれ部を形成する第3の工程と、第3の工程の後、保護膜を除去する第4の工程と、第4の工程の後、くびれ部が形成されたシリコン柱11の側面を覆うゲート酸化膜12を形成する第5の工程と、ゲート酸化膜12を覆うゲート電極13を形成する第6の工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクトプラグとゲート電極との間のショートおよび/またはコンタクトプラグとシリコンピラーとの間のショートを防止した半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】基板1上に立設された第一のシリコンピラー2と、その側面を覆う絶縁膜5と、絶縁膜5を覆うとともに、その先端部6aが第一のシリコンピラー2の先端部2aよりも基板1よりに位置してなるゲート電極6と、からなる縦型Tr部101と、基板1上に立設された第二のシリコンピラー2’と、その側面を覆う絶縁膜5’と、絶縁膜5’を覆うとともに、その先端部6’aが第二のシリコンピラー2’の先端部2’aよりも基板1から離れた側に位置してなり、ゲート電極6に接続されてなるゲートコンタクト電極6’と、からなるゲートコンタクト部102と、を有する半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】微細化された3次元的なデバイスを実現し得る、半導体装置の製造方法を提供する。

【解決手段】開示される、本発明の一実施形態による、半導体装置の製造方法によれば、ライン・アンド・スペース状の第2の層12を、第2の層12が延在する方向と交わる方向に延びるライン・アンド・スペース状の第8の層25をマスクとしてエッチングすることにより、二次元的に配列される第2の層12を得、これにより下地層をエッチングすることにより、二次元的に配列されるピラーを形成することができる。

(もっと読む)

81 - 100 / 285

[ Back to top ]