Fターム[5F140BF53]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 平面形状、配置 (630) | くし歯状、分割 (154)

Fターム[5F140BF53]に分類される特許

1 - 20 / 154

化合物半導体装置及びその製造方法

半導体装置

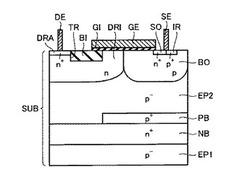

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

窒化物半導体装置

【課題】スイッチングノイズ発生を抑制できるノーマリオフ形の窒化物半導体装置の提供。

【解決手段】本発明の実施形態の窒化物半導体装置は、AlxGa1−xN(0≦x<1)からなる第1の半導体層4と、AlyGa1−yN(0<y≦1、x<y)からなる第2の半導体層5と、導電性基板2と、第1の電極6と、第2の電極8と、制御電極7と、を備える。第2の半導体層は第1の半導体層に直接接合する。第1の半導体層は、導電性基板に電気的に接続される。第1の電極及び第2の電極は、第2の半導体層の表面に電気的に接続される。制御電極は、第1の電極と第2の電極との間の第2の半導体層の前記表面上に設けられる。第1の電極は、Si−MOSFET102のドレイン電極8aに電気的に接続される。制御電極は、前記MOSFETのソース電極6aに電気的に接続される。導電性基板は、前記MOSFETのゲート電極7aに電気的に接続される。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置及び半導体装置の検査方法

【課題】狭いゲート電極間にコンタクトを配置することなく、オーバーラップ容量を測定する。

【解決手段】この半導体装置は、下記のような第1TEGパターン(不図示)を備えている。第1TEGパターンは、素子分離領域500と、素子分離領域500に形成された開口部(不図示)と、開口部上に設けられ、互いに平行に延伸した複数のゲート電極300と、開口部のゲート電極300で覆われていない部分に形成された拡散領域200と、を備えている。ここで、ゲート電極300の一方の端部は、開口部の外縁よりも内側に配置されている。また、第1コンタクト240は、ゲート電極300の一方の端部と、開口部の外縁の間に位置して、拡散領域200に接続している。一方、第2コンタクト340は、ゲート電極300に接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】ドレイン電流が大きく、且つ、製造が容易な半導体装置及びその製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置は、基板と、基板の上に設けられたゲート電極と、ゲート電極の下に設けられたチャネル領域と、第1の不純物を有し、チャネル領域の一方の側に隣接して設けられ、且つ、チャネル領域とともに第1の境界を成すソース領域と、第2の不純物を有し、チャネル領域の他方の側に隣接して設けられ、且つ、チャネル領域とともに第2の境界を成すドレイン領域とを有する。ゲート電極のソース領域側の側面はゲート長方向に沿って延びる凸部を有し、ドレイン領域側の側面はゲート幅方向と平行である。第1の境界及び第2の境界は、ゲート電極のソース領域側の側面及びドレイン領域側の側面に対応する形状を有し、基板の表面上における第1の境界は、第2の境界の長さに比べて長い。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

半導体装置

【課題】Finger形状のソース電極、ドレイン電極と接続される各N+型ソース層、N+型ドレイン層を取り囲むようにP+型コンタクト層が構成される場合でも、サージ電圧印加時に各Finger部の寄生バイポーラトランジスタが均一にオンする。

【解決手段】互いに平行に延在する複数のN+型ソース層9、N+型ドレイン層8を取り囲むようにP+型コンタクト層10を形成する。N+型ソース層9上、N+型ドレイン層8上及びN+型ソース層9が延在する方向と垂直方向に延在するP+型コンタクト層10上にそれぞれ金属シリサイド層9a、8a、10aを形成する。金属シリサイド層9a、8a、10a上に堆積された層間絶縁膜13に形成されたコンタクトホール14を介して、該各金属シリサイド層と接続するFinger形状のソース電極15、ドレイン電極16及び該Finger形状の各電極を取り囲むP+型コンタクト電極17を形成する。

(もっと読む)

半導体装置の製造方法、並びにデータ処理システム

【課題】チャネル領域を拡大することが可能な半導体装置の製造方法を提供する。

【解決手段】素子分離用の溝部3を形成した後、素子分離絶縁膜4として、当該溝部3に埋め込まれた状態で基板2の面上を覆うシリコン酸化膜26,31を形成する工程と、シリコン酸化膜26,31上に少なくとも埋め込みゲート用の溝部10を形成する位置に開口部を有するマスクパターンを形成する工程と、マスクパターンの開口部を通してシリコン酸化膜31を異方性エッチングにより選択的に除去することによって、当該シリコン酸化膜31に第1の溝部9と同じ幅及び深さとなる第2の溝部10を形成する工程と、第2の溝部10の底面及び側面に位置するシリコン酸化膜26,31を等方性エッチングにより選択的に除去することによって、当該第2の溝部10を活性領域6に形成される第1の溝部9よりも深く、且つ、第1の溝部9よりも大きい幅とする工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

半導体装置

【課題】MOSトランジスタにおける基板電位をソース領域及びドレイン領域とは異なる電位にすることができ、かつ基板電位の浮きを防止できる半導体装置を提供する。

【解決手段】ゲート電極17に対してチャネル長方向の位置であってチャネル幅方向でドレイン領域11d,11dに挟まれた位置のN型ウェル5によって基板電位用領域11bが形成されている。基板電位用領域11b、基板電位用領域11bよりも濃いN型不純物濃度をもつ基板電位用コンタクト領域9bが形成されている。基板電位用コンタクト領域9bは、基板電位用領域11bとドレイン領域11dのPN接合が所望のPN接合耐圧を得ることができる寸法Lでドレイン領域11dとは間隔をもって配置されている。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有し、第1導電型のバックゲートコンタクト領域を有さない第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

1 - 20 / 154

[ Back to top ]