Fターム[5F140BG41]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極形成後の処理 (1,641)

Fターム[5F140BG41]の下位に属するFターム

Fターム[5F140BG41]に分類される特許

61 - 80 / 99

半導体装置およびその製造方法

【課題】 本発明は、PチャネルMISトランジスタとNチャネルMISトランジスタ双方のしきい値電圧が低い半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、N型およびP型半導体領域上に、HfおよびZrから選ばれる金属元素、Si並びにOを含むゲート絶縁膜を形成する工程と、ゲート絶縁膜上に真空仕事関数4.8eV以上の金属を有する金属膜を形成する工程と、金属膜/ゲート絶縁膜/N型またはP型半導体領域の積層構造を還元雰囲気で熱処理する工程と、その後、P型半導体領域上の金属膜およびゲート絶縁膜を第2酸素拡散防止膜で被覆する工程と、その後、積層構造を酸素雰囲気で熱処理する工程と、その後、N型半導体領域上の金属膜およびゲート絶縁膜を第1酸素拡散防止膜で被覆する工程とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】可及的に簡略な構成で、かつ高集積度、高性能の半導体装置を得ることを可能にする。

【解決手段】半導体基板1上に板状に設けられた第1導電型の第1半導体領域3と、第1半導体領域の第1側面に設けられた第1強誘電体絶縁膜4と、第1強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第1ゲート電極6と、第1半導体領域の第2側面に設けられた第2強誘電体絶縁膜5と、第2強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第2ゲート電極7と、第1及び第2ゲート電極に挟まれるように第1半導体領域に形成されるチャネル領域と、チャネル領域の両側の第1半導体領域に設けられた第2導電型の第1ソース・ドレイン領域8と、を備え、第1半導体領域の厚さが第1半導体領域の不純物濃度で決まる空乏層の最大厚さの二倍よりも薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造方法が容易なデュアルメタルゲート構造を実現することができ、CMOSデバイス等の特性向上に寄与する。

【解決手段】 基板上に、pチャネルMISトランジスタ51とnチャネルMISトランジスタ52を具備した半導体装置であって、pチャネルMISトランジスタ51のゲート電極32の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は80%以上であり、nチャネルMISトランジスタ52のゲート電極53の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は60%以下である。

(もっと読む)

金属系膜の脱炭素処理方法、成膜方法および半導体装置の製造方法

【課題】 半導体装置の電気的特性を損なうことがないように、金属系膜中の炭素濃度を低減できる脱炭素処理方法および成膜方法を提供する。

【解決手段】 半導体基板であるSi基板1上に、ゲート絶縁膜2を形成し、次いでゲート絶縁膜2上に、W(CO)6ガスを含む成膜ガス用いたCVDによって、W系膜3aを形成する。その後、還元性ガスの存在下で酸化処理し、W系膜3a中のWは酸化させずにCのみを選択的に酸化させてW系膜3a中に含まれるC濃度を減少させる。その後、必要に応じて熱処理を施した後、レジスト塗布、パターニング、エッチング等を行い、さらにイオン注入等によって不純物拡散領域10を形成し、MOS構造の半導体装置を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10において、ソース領域40およびドレイン領域50が形成された半導体基板30と、ソース領域40およびドレイン領域50に挟まれた半導体基板30上に形成された絶縁膜60と、絶縁膜60上に形成されたゲート電極80と、絶縁膜60とゲート電極80との界面に形成された金属含有粒子70と、金属含有粒子70のうち界面の縁部60aからはみ出していた金属含有粒子が変化した絶縁粒子72と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リークの問題なく、Niシリサイドプロセスを適用できる半導体装置、及びその製造方法を提供する。

【解決手段】ソース・ドレイン拡散層9の表層部に、Ni2Siであるシリサイド膜11を形成する。続いて、シリコン基板1の全面に、アモルファスシリコン膜12を堆積後、2nd−RTAを行う。2nd−RTAによるシリサイド反応の進行時に消費されるシリコンが、シリサイド膜11下部のシリコン基板1のみではなく、上部のアモルファスシリコン膜12からも供給されるため、シリサイド反応をアモルファスシリコン膜12側にも進めることができる。その結果、シリコン基板1側へのシリサイドの侵入を抑制し、接合リークを低減することができる。

(もっと読む)

半導体素子のトランジスタ形成方法

【課題】複数のゲートスタックの稠密度とは関係なしに、均一な厚さのスペーサ酸化膜を一層迅速に形成できる半導体素子の形成方法を提供する。

【解決手段】半導体基板100上に複数のゲートスタック110を形成する段階と;前記半導体基板100上に気体状態のトリメチルアルミニウム及びトリス(tert-アルコキシ)シラノールを交互に供給することで、前記複数のゲートスタック110上にスペーサ酸化膜118を形成する段階と;を含んで半導体素子のトランジスタ形成方法を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレベーテッドソースドレイン構造を備えたMOSFETのゲート電極とソースドレインとの寄生容量を低く抑えることの可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極と離間して形成され、前記半導体基板表面よりも表面が高いエレベーテッドソースドレイン領域と、前記ゲート電極と前記エレベーテッドソースドレイン領域との間に形成された凹部と、前記凹部の前記半導体基板に形成されたソースドレインエクステンション領域と、前記ゲート電極及び前記凹部の底面及び側面に形成された第1のゲート側壁絶縁膜と、前記第1のゲート側壁絶縁膜上に形成された第2のゲート側壁絶縁膜とを備えた半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】レーザアニールを行う前に、パターン上にレーザ光を全反射する反射パターンを形成することで、レーザアニールの際のパターン損傷、消失等の発生防止を可能にする。

【解決手段】パターン(ゲート電極)13が形成された半導体基板11にレーザ光Lを照射する工程を備えた半導体装置の製造方法において、前記レーザ光Lを照射する前に、前記パターン13上に絶縁膜19を形成する工程と、前記パターン13上の前記絶縁膜19との界面において前記レーザ光Lを全反射するもので傾斜面を有する反射パターン21を形成する工程を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 金属材料からなるゲート電極を有するnチャネル型MISトランジスタおよびpチャネル型MISトランジスタの製造工程を簡略化する。

【解決手段】 ゲート絶縁膜5上に堆積したルテニウム膜をパターニングすることによって、nチャネル型MISトランジスタおよびpチャネル型MISトランジスタのそれぞれのゲート電極を同時に形成する。次に、それぞれのゲート電極に酸素を導入することによって、仕事関数が大きいゲート電極6Aに変換する。その後、nチャネル型MISトランジスタのゲート電極6Aを水素アニールで選択的に還元することによって、仕事関数の小さいゲート電極6Bに変換する。

(もっと読む)

レニウム系膜の成膜方法、ゲート電極の形成方法、半導体装置の製造方法、およびコンピュータ読取可能な記憶媒体

【課題】表面への酸化膜の形成が抑制されたレニウム系膜を成膜することができるレニウム系膜の成膜方法を提供すること。

【解決手段】基板上にレニウム系膜を形成する工程(第1工程)と、形成されたレニウム系膜の表面にアルコール類を接触させる工程(第2工程)とによりレニウム系膜を成膜する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】シリコン基板の表面から非常に浅い領域に高濃度の不純物を導入することができる半導体装置の製造方法を提供する。

【解決手段】p型シリコン基板1上の所定の位置に形成された所定形状のゲート絶縁膜4とゲート電極5を含むゲート構造のゲート長方向両側に浅い接合のソース/ドレイン領域を形成する半導体装置の製造方法であって、ソース/ドレイン領域の形成領域を、所定の深さにエッチングするエッチング工程と、p型シリコン基板1上に所定の組成の30Si層を堆積させ、ソース/ドレイン領域の形成領域に30Si層21を選択エピタキシャル成長させる30Si層形成工程と、p型シリコン基板1に中性子線50を照射して、30Si層21中に所定の濃度の31Pを形成する中性子線照射工程と、を含む。

(もっと読む)

半導体素子の製造方法

【課題】ゲートパターン形成後に行うライト酸化時に、タングステンシリサイド膜などのシリサイド膜の側面が膨出する現象を防止することができる半導体素子の製造方法を提供すること。

【解決手段】半導体基板21上にゲート絶縁膜23を形成するステップと、ゲート絶縁膜23上にポリシリコン膜24、シリサイド膜25及びハードマスク形成用膜の順に積層するステップと、ハードマスク26を形成するステップと、ハードマスク26をエッチングバリアとしてシリサイド膜25をエッチングし、側面にアンダーカット状凹部25Aを形成するステップと、ハードマスク26をエッチングバリアとして、ポリシリコン膜24をエッチングして、ゲートラインを形成するステップと、ライト酸化により、ポリシリコン膜24及びシリサイド膜25の側面を酸化するステップとを含む。

(もっと読む)

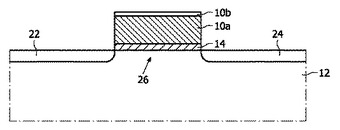

ポリシリコン電極を有する半導体デバイス

MOSトランジスタなどの半導体デバイスを製造する方法。本デバイスは、ポリシリコンのゲート(10)および、半導体基板(12)内に形成されチャネル領域(26)で分離されたドーピング領域(22,24)を備える。後の熱アニールの間にドーパント・イオンが拡散することを阻害するために、半導体基板の露出面を、例えばイオン衝撃によって、アモルファス化する。活性化およびポリシリコン再成長のためのサーマルバジェットが低いことは、ソース/ドレイン領域における急峻なドーピングプロファイルを確実にするために好ましい。結果として、ゲート電極の上部(10b)は、アモルファスのままである。ポリシリコンの下部を用いて低抵抗の接点を作成するために、ゲート電極の上部を除去する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 シリサイド膜の底面とpn接合界面との間の距離を広く保つことが可能であり、しかも制御性よく半導体装置を製造することが可能な製造方法を提供する。

【解決手段】 第1導電型の半導体領域81上に形成された第2導電型の半導体領域87上に第1のシリサイド膜89を形成する工程と、第1のシリサイド膜上に(Si−H)基を含むシリコン化合物膜90を塗布によって形成する工程と、熱処理により第1のシリサイド膜に含まれる金属とシリコン化合物膜に含まれるシリコンとを反応させて第2のシリサイド膜91を形成する工程とを備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ポリメタルゲート構造とデュアルゲート構造とを採用するCMOS LSIにおいて、ゲート電極の一部を構成する高融点金属膜の酸化と、ゲート電極の他の一部を構成するp型多結晶シリコン膜中のホウ素の拡散とを共に抑制することのできるライト酸化処理技術を提供する。

【解決手段】水素ガスおよび酸素ガスと水素ガスとから触媒により合成された水蒸気を含む混合ガスを半導体ウエハ1Aの主面に供給し、エッチングによって削られたゲート電極の端部下のゲート絶縁膜のプロファイルを改善する熱処理を、ゲート電極の一部を構成する高融点金属膜が実質的に酸化されず、かつゲート電極の他の一部を構成するp型多結晶シリコン膜中のホウ素がゲート酸化膜を通って基板に拡散しない低熱負荷条件下で行う。

(もっと読む)

半導体素子の製造方法

【課題】タングステンの異常酸化を発生させず且つ素子の電気的特性の劣化を防止することが可能な半導体素子の製造方法を提供する。

【解決手段】半導体基板上の一領域上に、金属膜を含むゲートを形成する段階と、前記金属膜の酸化を誘発させないLPCVD法によって全表面上にLPCVD酸化膜を形成する段階とを含む。

(もっと読む)

非SiO2ゲート誘電体を有するMOSデバイスの製造方法

多結晶シリコン層(20)がゲート誘電体(10)上に堆積され、次いでその一部分が再酸化されて、当該ポリSi層と下側のゲート誘電体との間に酸化物(30)の薄層を形成するようにする。続いて、ポリSi層が完全シリサイド化形態(50)に変換され、FUSIゲートを生成させる。ゲート誘電体は、例えばHf含有材料であるhigh−k材料、又はSiON、或いは別の非SiO2誘電体とすることができる。障壁酸化物層(30)は、好ましくは1nm未満の厚みである。 (もっと読む)

半導体素子の製造方法

【課題】高誘電体膜の結晶化によるエッチングレートの低下を回避する。

【解決手段】先ず、下地基板11を用意して、下地基板上に、高誘電率材の高誘電体非結晶膜50を形成する。次に、高誘電体非結晶膜上に、高誘電率材の非結晶化温度を成膜温度としてアモルファスシリコン膜60を形成する。次に、フォトリソグラフィ法及びドライエッチングにより、アモルファスシリコン膜を加工してゲート電極形成用膜62を形成する。次に、ゲート電極形成用膜62をマスクとしたウェットエッチングにより、ゲート電極形成用膜で覆われた高誘電体非結晶膜の部分を残存させ、露出した高誘電体非結晶膜の部分を除去する。次に、ゲート電極形成用膜に対して熱処理を行うことにより、アモルファスシリコンをポリシリコンに改質して、ゲート電極64にする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】サイドウォールスペーサーを形成した際に削られた半導体基板部分を埋め込むことでエクステンション領域を半導体基板表面上に形成することを可能とし、短チャネル効果を抑制することを実現する。

【解決手段】半導体基板101上にゲート絶縁膜102を介して形成されたゲート電極103の側面にサイドウォールスペーサー104が形成され、半導体基板101上に堆積されたエクステンション領域109、110と、この上に形成されたソース・ドレイン112、113とを備えた半導体装置1において、サイドウォールスペーサー104を形成した際に削られた半導体基板101部分を埋め込むように第1エピタキシャル層107、108を形成し、第1エピタキシャル層上にこれとは逆導電型の第2エピタキシャル層からなるエクステンション領域109、110が形成されたものである。

(もっと読む)

61 - 80 / 99

[ Back to top ]