Fターム[5F140BJ26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | コンタクト構造 (1,444)

Fターム[5F140BJ26]の下位に属するFターム

プラグを有するもの (1,074)

コンタクトホールの形状、配置 (234)

引出し電極を有するもの (70)

Fターム[5F140BJ26]に分類される特許

61 - 66 / 66

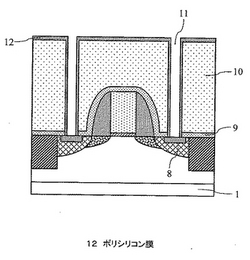

半導体装置の製造方法

【課題】 微細且つ電気的特性に優れた半導体装置の製造方法を提供する。

【解決手段】 層間絶縁膜10をマスクとしたストッパー膜9のドライエッチングによって、拡散層領域8に至るコンタクトホール11を形成する。この際、ストッパー膜9のオーバーエッチングによって、コンタクトホール11の底面をシリコン基板1の表面よりリセスする。続いて、シリコン基板1の表面を洗浄した後、コンタクトホール11の内面を覆うようにして層間絶縁膜10の上にポリシリコン膜12を形成する。ポリシリコン膜12の膜厚は、コンタクトホール11の底面がシリコン基板1の表面に対してリセスした深さより大きく、シリサイド化で消費されるシリコンの厚さより小さくなるようにする。これにより、オーバーエッチングおよびシリサイド化によってシリコン基板1から消失するシリコンの量を低減させることができる。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイスも提供される。  (もっと読む)

(もっと読む)

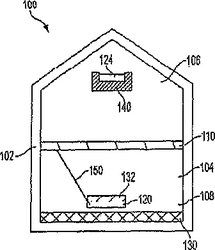

垂直導電パワー電子デバイス及びその実現方法

【課題】出力抵抗、熱抵抗、サイズ及びゲート変化値を低減した垂直導電電子パワーデバイスを提供する。

【解決手段】半導体基板10上のエピタキシャル層40内にゲート領域20、ソース領域25、ドレイン領域30、及び第1メタライゼーション・レベルによるゲート部21、ソース部26、ドレイン部31、及び第2メタライゼーション・レベルによるゲート端子/パッド、ソース端子/パッド65、ドレイン端子/パッドを具える。このデバイスは、基板10に対して垂直に延びドレイン領域30の第1領域及び第2領域の両方の下に配置されたシンカーSの格子によって形成されるシンカー構造45を具えて、このシンカー構造は、ソース領域25から基板10を通ってドレイン領域30に向かう電流用の導電チャンネルとして作用する。

(もっと読む)

半導体装置及びその製造方法

【課題】 サイドウォールのエッチングを抑えて、加工マージンを確保する。

【解決手段】 ゲート電極の側壁にサイドウォールを有するトランジスタを覆うように、下から順番に第1のシリコン窒化膜、第1のシリコン酸化膜、第2のシリコン窒化膜及び第2のシリコン酸化膜を形成する。トランジスタのソース・ドレイン領域とゲート電極の両方にまたがる領域に開口を有するフォトレジストをマスクとし、第2のシリコン窒化膜をエッチングストッパとして第2のシリコン酸化膜をドライエッチングし、第2のシリコン窒化膜をドライエッチングし、第1のシリコン窒化膜をエッチングストッパとして第1のシリコン酸化膜をドライエッチングし、第1のシリコン窒化膜をドライエッチングして、コンタクトホールを形成する。コンタクトホールに導電物質を埋め込むことにより、トランジスタのソース・ドレイン領域とゲート電極の両方に達するシェアードコンタクトを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】電流容量の増大とラッチアップ耐量の向上を図ることができる横型IGBTなどの半導体装置およびその製造方法を提供する。

【解決手段】貼り合わせ酸化膜2を介して支持基板1上にn型半導体層3が形成されたSOI基板100のn型半導体層3に貼り合わせ酸化膜2に接するように形成されるp型ベース層4と、このp型ベース層4と離してn型半導体層3に貼り合わせ酸化膜2に接するように形成されるnバッファ層5と、p型ベース層4内に形成される第1トレンチ6と、n型バッファ層内に形成される第2トレンチ7と、p型ベース層4の表面層に第1トレンチ6の開口部近傍に接するように形成されるn型エミッタ層10と、n型バッファ層5の表面層に第2トレンチ7と接するように形成されるp型コレクタ層11と、n型エミッタ層10とn型半導体層3に挟まれたp型ベース層4上にゲート酸化膜12を介して形成されるゲート電極13と、第2トレンチ6内部を充填して形成されるエミッタ電極14と、第2トレンチ7内部を充填して形成されるコレクタ電極15とを有する構成とする。

(もっと読む)

半導体装置

【課題】オン抵抗の低減とESD耐量などのサージ耐量の向上を図ることができる半導体装置を提供する。

【解決手段】p型半導体基板1の表面層にストライプ状のnウェル領域2を形成し、このnウェル領域2の表面層にストライプ状のpウェル領域3を形成し、このpウェル領域3の表面層にストライプ状のnソース領域4とストライプ状のpコンタクト領域5を形成し、このnソース領域4上とpコンタクト領域5上にストライプ状のソース電極11を形成し、nウェル領域2の表面層にpウェル領域3と離してストライプ状のnドレイン領域8を形成し、このnドレイン領域8に囲まれるように四角形のpアノード領域15を複数個形成し、nドレイン領域8上とpアノード領域15上にドレイン電極10を形成する。pウェル領域3(nソース領域4)と対向する四角形のpアノード領域15の辺とはドレイン電極10は接しないようにする。

(もっと読む)

61 - 66 / 66

[ Back to top ]