Fターム[5F140BJ26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | コンタクト構造 (1,444)

Fターム[5F140BJ26]の下位に属するFターム

プラグを有するもの (1,074)

コンタクトホールの形状、配置 (234)

引出し電極を有するもの (70)

Fターム[5F140BJ26]に分類される特許

41 - 60 / 66

電力用半導体装置および電源回路

【課題】横形パワーMOSFETのチップ面積当たりのオン抵抗を低減する。

【解決手段】本発明の横形パワーMOSFETは、外部ソース電極と接続してある低抵抗p型半導体基板上のp型半導体領域の中の半導体表面から前記p型半導体領域までを貫通する低抵抗打抜き導電領域を設け、この低抵抗打抜き導電領域で挟まれる半導体領域にドレイン電極と電気的に接続される2個以上のn型ドレイン領域を形成し、アクティブ領域上の外部ドレイン領域を設ける。

(もっと読む)

立体的形状の活性領域を含むCMOS構造体

【課題】 複数の結晶方位の半導体基板領域を有するCMOSデバイス及びCMOS構造体、及び、そのようなCMOSデバイス及びCMOS構造体を製造するための方法を提供する。

【解決手段】 CMOS構造体は、半導体基板内の第1の活性領域を用いて配置された第1のデバイスを含み、第1の活性領域は、平坦であり、第1の結晶方位を有する。CMOS構造体はまた、半導体基板内の第2の活性領域を用いて配置された第2のデバイスを含み、第2の活性領域は、立体的形状であり、第1の結晶方位の存在しない第2の結晶方位をもつ。第1の結晶方位及び第2の結晶方位は、典型的には電荷キャリア移動度に関して、第1のデバイス及び第2のデバイスの性能を最適化することを可能にする。立体的形状の第2の活性領域はまた、単一厚さを有する。CMOS構造体は、立体的形状の第2の活性領域を形成するための結晶学的特異性エッチャントを用いて製造することができる。

(もっと読む)

半導体装置

【課題】SRAMやフラッシュメモリ等のメモリやロジックに用いられる、コンタクトや配線をできるだけ省略し、構造を簡略化することによって半導体装置の高集積化を図り、かつ、生産性を向上させるMOS型半導体装置を提供する。

【解決手段】MOS型半導体装置10では、半導体基板11と、半導体基板11にウェル領域12を備え、かつ、ゲート15とソース13/ドレイン14とを有し、ソース13の上部を形成するソース電極133が、ソース13を形成する拡散領域131を通過して、ウェル領域12又はボディ領域111に貫通していて、かつ、ドレイン14の上部を形成するドレイン電極は、ウェル領域12又はボディ領域111を貫通していない。

(もっと読む)

半導体装置およびその製造方法

【課題】接合リークの増大を抑制できるとともに、狭いゲート電極間におけるコンタクトの不良の発生、および層間絶縁膜の埋め込み不良の発生を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】まず、ゲート電極4をマスクとしたイオン注入によりLDD領域5が形成される。ゲート電極4の側面に第1のサイドウォール7が形成された後、これらをマスクとしてソース・ドレイン領域8が形成される。ソース・ドレイン領域8上にシリサイド領域を形成する前に、第1のサイドウォール7の側面に第2のサイドウォール10が形成される。ソース・ドレイン領域8にシリサイド領域11が形成された後、第2のサイドウォール10が除去される。これにより、第1のサイドウォール7とシリサイド領域11との間のソース・ドレイン領域8に非シリサイド領域12が設けられる。

(もっと読む)

パターン形成方法

【課題】デバイスの信頼性を高めることが可能な、微細なパターンに接続するコンタクトホールのパターン形成方法を提供すること。

【解決手段】パターン形成方法は、絶縁層20の第1のコンタクトホール11を形成すべき領域を含んだ第2のコンタクトホール13を形成しない領域の上にブロック膜21を形成する工程と、ブロック膜21及び絶縁層20の上に、第1、第2のコンタクトホール11,13を形成するための開口を有するレジスト膜30を形成する工程と、レジスト膜30をマスクとしてエッチングすることにより、ブロック膜21及び絶縁層20の中に第1のコンタクトホール11を、絶縁層20の中に第2のコンタクトホール13を、それぞれ形成し、絶縁層20上面からの深さが第2のコンタクトホール13より第1のコンタクトホール11の方が浅く、第1のコンタクトホール11が半導体基板1に接触しないように形成する工程とを含む。

(もっと読む)

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

半導体デバイスを製造する方法及びそのような方法で得られる半導体デバイス

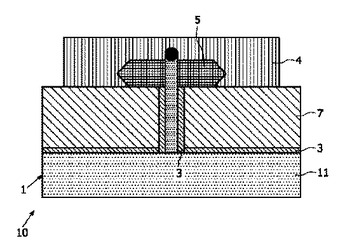

本発明は、少なくとも1つの半導体素子を備える半導体本体(1)を備える半導体デバイス(10)を製造する方法に関し、半導体本体(1)の上には、メサ形状半導体領域(2)が形成され、マスキング層(3)が、メサ形状半導体領域(2)の上に蒸着され、その頂部でメサ形状半導体領域(2)の側面と境界を接するマスキング層(3)の一部(3A)が取り除かれ、導電性接続領域(4)が、結果として得られる構造の上に形成され、メサ形状半導体領域(2)のための接点を形成する。本発明によれば、マスキング層(3)の部分(3A)の除去後、導電性接続領域(4)の形成前に、メサ形状半導体領域(2)が、マスキング層(3)の部分(3A)の除去によって自由にされるメサ形状半導体領域(2)の側面で追加的半導体領域(5)によって広げられる。このようにして、極めて低い接触抵抗を有するデバイス(10)が簡単な方法で得られる。好ましくは、メサ形状半導体領域(2)は、VLSのようなさらなるエピタキシアル成長プロセスによってナノワイヤによって形成される。追加的領域(5)は、例えば、MOVPEによって得られ得る。

(もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トレンチ横型パワーMOSFETにおいて、装置の信頼性を高めること。

【解決手段】半導体基板1の表面層にトレンチ5を形成する。トレンチ5は、半導体基板1の表面層を第1メサ領域41と第2メサ領域42に分割し、かつ第1メサ領域41と第2メサ領域42を交互に配置させる。第1メサ領域41および第2メサ領域42は、それぞれソース電流およびドレイン電流の引き出しをおこなう。第2メサ領域42は、半導体基板1からの深さが、第1メサ領域41よりも深くなっている。

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイドをゲート電極、ソース電極またはドレイン電極に使用した半導体装置の接合リーク電流の増加を防止する。

【解決手段】ゲート領域1aとソース領域1b及びドレイン領域1c形成後の半導体基板の表面に形成された自然酸化膜2が、イオンの半導体基板への侵入が表面から2nm以下に抑制されるように制御したスパッタエッチングにより除去され、自然酸化膜2が除去された表面にニッケル3またはニッケル化合物が成膜され、アニールにより、ゲート領域1a、ソース領域1bまたはドレイン領域1cにニッケルシリサイド4が形成される。この結果、ゲート領域1a、ソース領域1bまたはドレイン領域1c内に、スパイクの形成を防ぎ、リーク電流が低減する。

(もっと読む)

半導体装置

【課題】複数の半導体素子が集積された半導体装置にあって、それら半導体素子における電流分布の偏りを好適に抑制することのできる半導体装置を提供する。

【解決手段】半導体基板の上表面に延設されたトレンチ溝7A,7Bと、これらトレンチ溝7A,7Bの内部に埋め込まれたドレイン引出電極15A,15Bとを備えた半導体素子を複数併設して半導体装置を構成した。こうした半導体装置において、半導体素子の形成領域S全体の下方における半導体基板の内部に、半導体素子の形成領域Sの下方全体にわたる面状のN型埋込拡散層3をドレイン引出電極15A,15Bと接続された状態で埋込形成するようにした。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の低抵抗化を図る。

【解決手段】本発明の半導体装置は、第1金属膜18に当接するように半導体層に形成された貫通孔10と、前記貫通孔10の側壁部に形成された絶縁膜12と、前記絶縁膜12が形成されていない前記貫通孔10の底部の第1金属膜18上と前記半導体層上に形成された第2金属膜13と、前記貫通孔10内の前記絶縁膜12及び第1金属膜18上に形成されたバリアメタル膜14と、前記バリアメタル膜14を介して前記貫通孔内に形成された配線層15とを具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高いオン電流とソース/ドレイン拡散層における低い接合リーク電流を両立可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に設けられたゲート絶縁膜3を含む。ゲート電極21は、ゲート絶縁膜上に設けられ、第1部分を含む。第1部分は、半導体と金属との化合物からなり、下面がゲート絶縁膜に達する。第1部分内の金属元素の密度は第1値である。1対のソース/ドレイン拡散層11は、ゲート電極の下方のチャネル領域を挟む。導電膜23は、半導体基板のソース/ドレイン拡散層の部分に設けられ、半導体と金属との化合物からなる。導電膜内の金属元素の密度は、第1値より小さい第2値である。

(もっと読む)

半導体装置及びその製造方法

【課題】 ドレイン電極の低抵抗化とフリップチップ実装が可能な半導体装置の製造方法を提供する。

【解決手段】 トランジスタを構成する複数の電極の少なくとも1つと電気的に接続する少なくとも1つの第1電極11bを半導体チップの表面側に備え、複数の電極の内の他の1つと電気的に接続する第2電極9を半導体チップの裏面側に備えてなる半導体装置であって、半導体チップの表面側から裏面側に貫通する貫通孔を有し、半導体チップ表面側に一部が露出し、貫通孔を介して第2電極9と電気的に接続する貫通電極11aを備える。

(もっと読む)

半導体装置

【課題】従来、バリアメタル206を敷いてアロイスパイクによる拡散層の突き抜けを抑

えていた。すると、バリアメタル206の影響でコンタクト抵抗の上昇によりPウェル2

08の電位が上昇し、NMOS100の閾値変動等が発生する。そこで、アロイスパイク

等の現象の影響を抑え、かつPウェル208の電位を制御しうる半導体装置を提供する。

【解決手段】NMOS100の幅方向にソース205、P型拡散層301を交互に位置す

るように形成し、バリアメタル206を、Pウェル208上で接合を有するソース205

上には残し、接合を有さないP型拡散層301では除去し、両領域を短絡するようアルミ

電極207を形成する。接合が形成されているソース205はバリアメタル206により

アロイスパイクが抑制され、P型拡散層301ではバリアメタルが除去されているためコ

ンタクト抵抗を下げることができ、P型拡散層301の電位が安定化される。

(もっと読む)

逆ソース/ドレイン金属コンタクトを有する電界効果トランジスタ(FET)及びその製造方法

【課題】 コンタクト間隔及び寄生容量の問題に対する解決策を提供する、改善されたFET設計を構築する。

【解決手段】 本発明は、下方の第1の誘電体層内に配置された下部と上方の第2の誘電体層内に配置された上部とを有する逆ソース/ドレイン金属コンタクトを含む電界効果トランジスタ(FET)に関する。逆ソース/ドレイン金属コンタクトの下部は、上部より大きい断面積を有する。好ましくは、逆ソース/ドレイン金属コンタクトの下部は、約0.03μm2から約3.15μm2の範囲の断面積を有し、こうした逆ソース/ドレイン金属コンタクトは、約0.001μmから約5μmの範囲の距離だけ、FETのゲート電極から間隔を空けて配置される。

(もっと読む)

半導体装置及び該半導体装置を動作させる方法

本発明は、ドレイン延長部(8)を備えるラテラルDMOSTに特に関する。既知のトランジスタにおいて、更なる金属ストリップ(20)は、ゲート電極コンタクトストリップと、ソース領域コンタクト(15)に電気的に接続されているドレインコンタクト(16)との間に位置される。本特許出願において提案される装置において、更なる金属ストリップ(20)とソースコンタクト(15,12)との間の接続部は、コンデンサ(30)を有し、更なる金属ストリップ(20)は更なる金属ストリップ(20)に電圧を供給するための更なるコンタクト領域(35)を備えている。このようにして、改善された線形性が実現可能であり、当該装置の実用性が、特に、高電力及び高周波数において改善される。好ましくは、コンデンサ(30)は、単一の半導体基体(1)内にトランジスタと一体化されている。本発明は、更に、本発明による装置(10)を動作させる方法を有する。  (もっと読む)

(もっと読む)

二重拡散型MOSFETおよびこれを用いた半導体装置

【課題】L−DMOSFET本来の特性を損なうことなく、また素子面積の増大を招くことなく、高い静電破壊耐量を得ることができるL−DMOSFETを提供する。

【解決手段】半導体基板11上に形成されたN型半導体層からなるドレイン領域13と、ドレイン領域13内に形成されたP型半導体領域からなるボディ領域15と、ボディ領域15内に形成されたN型ソース領域16と、ボディ領域15表面に形成されたゲート電極21とを含み、前記ドレイン領域13内に、ドレイン領域表面に形成されたN+型ドレインコンタクト領域18を形成すると共に、前記N+型ドレインコンタクト領域18に囲まれた領域に形成され、前記N+型ドレインコンタクト領域18と同電位となるように電気的に接続されたP型領域19を具備してなることを特徴とする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】一度のシリサイド化工程により製造でき、かつ小さなソース及びドレイン抵抗を有するフルシリサイド型電界効果トランジスタを提供する。

【解決手段】ソース電極及びドレイン電極11、12の上面が、シリサイドゲート電極2上面より高くする。シリサイドゲート電極2は、シリコンゲート電極2aへの金属の拡散により形成され、ソース電極11及びドレイン電極12は、シリコンゲート電極2より厚いシリコン層11a、12aへの金属拡散により形成する。ゲート電極2よりソース及びドレイン電極11、12が高いから、ソース及びドレイン電極11、12を上面からの金属拡散により半導体基板1の浅い領域に留まるように形成しても、ゲート電極2は完全にシリサイド化される。また、ソース及びドレイン電極が浅いので、接触抵抗が小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、シリサイドプロセスを適用したMOSFETにおいて、シリサイド膜をより大きく形成できるようにする。

【解決手段】たとえば、シリコン基板11の表面上に設けられたゲート電極16の側面には、それぞれ、内側ゲート側壁膜18および外側ゲート側壁膜21が形成されている。一方、ゲート電極16の形成位置を除く、シリコン基板11の表面部には、浅い低濃度拡散層17、および、二段構造の浅い高濃度拡散層19と深い高濃度拡散層22とが形成されている。そして、浅い高濃度拡散層19および深い高濃度拡散層22に対応するシリコン基板11の表面部には、それぞれの高濃度拡散層19,22の深さに応じて厚さの異なる二段構造のシリサイド膜23が形成されている。

(もっと読む)

垂直導電パワー電子デバイス及びその実現方法

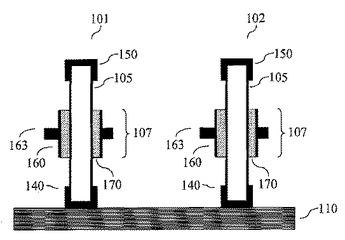

【課題】出力抵抗、熱抵抗、サイズ及びゲート変化値を低減した垂直導電電子パワーデバイスを提供する。

【解決手段】半導体基板10上のエピタキシャル層40内にゲート領域20、ソース領域25、ドレイン領域30、及び第1メタライゼーション・レベルによるゲート部21、ソース部26、ドレイン部31、及び第2メタライゼーション・レベルによるゲート端子/パッド、ソース端子/パッド65、ドレイン端子/パッドを具える。このデバイスは、基板10に対して垂直に延びドレイン領域30の第1領域及び第2領域の両方の下に配置されたシンカーSの格子によって形成されるシンカー構造45を具えて、このシンカー構造は、ソース領域25から基板10を通ってドレイン領域30に向かう電流用の導電チャンネルとして作用する。

(もっと読む)

41 - 60 / 66

[ Back to top ]