Fターム[5F140BJ26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | コンタクト構造 (1,444)

Fターム[5F140BJ26]の下位に属するFターム

プラグを有するもの (1,074)

コンタクトホールの形状、配置 (234)

引出し電極を有するもの (70)

Fターム[5F140BJ26]に分類される特許

21 - 40 / 66

半導体装置とその製造方法

【課題】本発明は、高性能でかつ閾値電圧の低い半導体装置とその製造方法を提供することを目的とする。

【解決手段】基板に形成され、NMOSトランジスタが形成されるNMOS形成領域とPMOSトランジスタが形成されるPMOS形成領域とを絶縁分離する素子分離領域と、該基板上に形成されたHigh−k材料からなるNMOSおよびPMOSのゲート絶縁膜と、該NMOSのゲート絶縁膜上に形成されたNMOSゲート電極と、該PMOSゲート絶縁膜上に形成された第1ニッケルシリサイド層と、該第1ニッケルシリサイド層上に形成され、該第1ニッケルシリサイド層よりも厚くかつ該第1ニッケルシリサイド層よりニッケル密度が大きい第2ニッケルシリサイド層と、を有するPMOSゲート電極と、該NMOSゲート電極および該PMOSゲート電極の側壁に形成されたサイドウォールスペーサとを備える。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

直列電界効果型トランジスタのパラメータフィッティング方法

【課題】 直列接続電界効果型トランジスタの回路モデルパラメータのフィッティング方法に関し、多段直列接続電界効果型トランジスタの回路モデルパラメータの効率的な抽出手順を提供し、モデル化を実施可能にする。

【解決手段】 多段直列接続電界効果型トランジスタの評価テスト用デバイスを用意し、複数のゲート電極に印加する電圧を制御して電気特性を評価し、パラメータ変数の基準値を孤立電界効果型トランジスタのモデル変数で設定し、さらに、パラメータ変数の微小変動分を加える形で回路モデルを作成し、次いで、評価した電気特性の多数のバイアス点とパラメータ変数の微小変動分の関係を、評価関数で評価し、評価関数を最小化することで微小変動分の変数の最適解を求め、最適解を多数の多段直列接続電界効果型トランジスタの評価テスト用デバイスについて求めてレイアウト変数の関数としてモデル化する。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置におけるトランジスタの熱破壊を防止し得るとともに、安全動作領域(SOA)を拡大しトランジスタ設計の自由度を高め得る半導体装置及びその製造方法を提供すること。

【解決手段】 トランジスタセルを並列にチップ内に均一に配置した半導体装置において、チップの面中央部にトランジスタセルの不動作領域を形成する。不動作領域を形成手段として、1)ソースとドレインのn型拡散層を設けない方法 2)ソースとドレインのコンタクト窓を開けない方法 3)ゲート電極を分岐してソースに接続する方法を採る。また、不動作領域の形成に代えて当該領域のトランジスタセルの閾値電圧を高くして動作電流を低くする手段を採ることもできる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース/ドレイン領域における接合部の耐圧を向上でき、寄生バイポーラトランジスタ特性の影響を低減できる半導体装置を提供する。

【解決手段】(a)に示す低耐圧トランジスタは、ソース/ドレイン領域13,14間の基板11の第1領域上に形成されたゲート絶縁膜15及び第1ゲート電極16と、ソース/ドレイン領域13,14上のシリサイド層13A,14Aとを備える。(b)に示す高耐圧トランジスタは、ソース/ドレイン領域23,24間の基板11の表面が所定の深さ除去された第2領域上に形成された、ゲート絶縁膜15より膜厚が厚いゲート絶縁膜25、及び第2ゲート電極16と、ソース/ドレイン領域23,24上のシリサイド層23A,24Aとを備える。所定の深さはゲート絶縁膜25とゲート絶縁膜15との厚さの差に相当し、シリサイド層23A,24Aの上面は基板11の第2領域とゲート絶縁膜25との界面より高い構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】「ひずみシリコン」技術を用いて形成された半導体装置において、NMOSトランジスタの電流駆動能力の向上を達成できるとともに、PMOSトランジスタの電流駆動能力の低下を抑制した半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板1の全面に、例えばPECVD法(プラズマ化学気相成長法)を用いて、厚さ20〜80nmのシリコン窒化膜を形成してライナー膜18とする。なお、ライナー膜18の成膜条件としては、成膜温度400℃以下で、Tensileストレスが0〜800MPaとなるように条件を設定する。そして、紫外線照射およびまたは300〜500℃の熱処理を行うことにより膜収縮させ、PMOS領域におけるライナー膜18では、ゲート電極4のサイドウォール窒化膜14の側面外方において、サイドウォール窒化膜14に沿って連続的、あるいは断続的にクラックCRを発生させる。

(もっと読む)

半導体装置、およびその製造方法

【課題】隣接するゲート電極間の距離が小さい場合であっても、応力膜によりチャネル領域に効果的に応力を発生させて電荷移動度を向上させることのできる半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、素子分離領域を有する半導体基板と、前記半導体基板上に各々ゲート絶縁膜を介して略並列に形成された複数のゲート電極と、前記半導体基板内の前記複数のゲート電極下の領域に各々形成された複数のチャネル領域と、前記半導体基板内の前記複数のチャネル領域を挟んだ領域に形成されたソース・ドレイン領域と、前記半導体基板および前記複数のゲート電極上を覆うように形成された第1の応力膜と、前記複数のゲート電極間の領域に形成された空隙内の少なくとも一部に形成された第2の応力膜と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】電力用半導体装置において十分な基板強度を確保しつつ低オン抵抗且つ高耐圧でスイッチング速度を向上できるようにする。

【解決手段】P型の半導体基板1に形成されたN型のリサーフ領域2と、半導体基板1の上部にリサーフ領域2と隣接したP型のベース領域3と、ベース領域3にリサーフ領域2と離隔したN型のエミッタ/ソース領域8と、ベース領域3にエミッタ/ソース領域8と隣接したP型のベース接続領域10と、エミッタ/ソース領域8の上からベース領域3の上及びリサーフ領域2の上に形成されたゲート絶縁膜6並びにゲート電極7と、リサーフ領域2にベース領域3と離隔したP型のコレクタ領域4とを有している。半導体基板1は、その抵抗値が半導体基板1に添加された不純物濃度で決まる抵抗値の2倍以上となるように結晶欠陥が導入されている。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】炭化ケイ素からなる基板上に欠陥密度の低減された活性層が形成された炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、面方位{0001}に対しオフ角が50°以上65°以下である、炭化ケイ素からなる基板2と、バッファ層21と、活性層(エピタキシャル層3、p型層4、およびn+領域5、6)とを備える。バッファ層21は、基板2上に形成され、炭化ケイ素からなる。活性層は、バッファ層21上に形成され、炭化ケイ素からなる。活性層におけるマイクロパイプ密度は基板2におけるマイクロパイプ密度より低い。また、活性層における、バーガーズベクトルの向きが[0001]である転位の密度は、基板2における当該転位の密度より高い。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、面方位{0001}に対しオフ角が50°以上65°以下である、炭化ケイ素からなる基板2と、半導体層(図1のp型層4)と絶縁膜(図1の酸化膜8)とを備える。半導体層(p型層4)は基板2上に形成され、炭化ケイ素からなる。絶縁膜(酸化膜8)は、半導体層(p型層4)の表面に接触するように形成されている。半導体層と絶縁膜との界面(チャネル領域と酸化膜8との界面)から10nm以内の領域における窒素原子濃度の最大値が1×1021cm-3以上である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極の接触抵抗の低減によって高性能化した半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体基板上に第1の金属を堆積する工程と、第1の熱処理により第1の金属と半導体基板を反応させて、前記ゲート電極両側の前記半導体基板表面に金属半導体化合物層を形成する工程と、金属半導体化合物層中に、Siの原子量以上の質量を有するイオンをイオン注入する工程と、金属半導体化合物層上に第2の金属を堆積する工程と、第2の熱処理により、第2の金属を金属半導体化合物層中に拡散させることで、金属半導体化合物層と半導体基板の界面に、第2の金属を偏析させて界面層を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

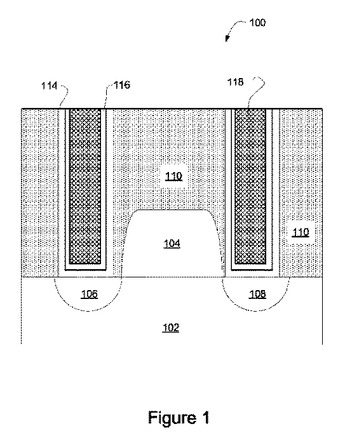

半導体装置および半導体装置の製造方法

【課題】p型MISFETまたはn型MISEFETを有する半導体装置において、p型MISFETまたはn型MISEFETのソース/ドレイン電極界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板100にp型MISFET200を備える半導体装置であって、p型MISFET200が、半導体基板100中のチャネル領域204と、チャネル領域204上に形成されたゲート絶縁膜206と、ゲート絶縁膜206上に形成されたゲート電極208と、チャネル領域204の両側の、Niを含有するシリサイド層210で形成されたソース/ドレイン電極と、ソース/ドレイン電極と半導体基板100との界面の半導体基板100側に形成された、Mg、CaまたはBaを含有する界面層230を有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 ソース/ドレイン領域にシリコン層を成長する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板上にゲート絶縁層,ポリシリコン層の積層を形成する工程と、前記ポリシリコン層の表面に第1の加速エネルギでp型不純物を高濃度にドープする工程と、前記ポリシリコン層,ゲート絶縁層をパターニングし,ゲート電極を形成すると共に,その両側に基板シリコン表面を露出する工程と,前記露出した基板シリコン表面に前記第1の加速エネルギより高い第2の加速エネルギでp型不純物を深くイオン注入する工程と、シリコン層を、前記ポリシリコン層表面上には成長させず、前記基板シリコン表面上にのみ成長する工程と、

を有する。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタと保護ダイオードの降伏電圧の差を常に一定とする半導体装置の構造及びその製造方法を提供する。

【解決手段】半導体基板1にはLDMOSが形成され、このLDMOSを静電破壊から保護するダイオードが作り込まれている。LDMOSのドレイン領域5はダイオードのカソード領域11として用いられ、LDMOSのバックゲート領域はダイオードのアノード領域14として用いられる。ダイオードのカソード領域11とLDMOSのドレイン領域5とは同じ工程で形成され、ダイオードのアノード14とLDMOSのバックゲート領域4とは同じ工程で形成される。ソース領域とドレイン領域とが半導体基板の横方向に並べられた横型MOSトランジスタと保護ダイオードとの降伏電圧の差を常に一定とすることができる。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子の熱による素子欠陥及び破壊を未然に防止するのに適した半導体素子及びその製造方法を提供する。

【解決手段】ウェハー上にトランジスタ10を形成する段階と、トランジスタ10の上部に絶縁層を形成する段階と、トランジスタ10の両側のソース/ドレイン領域のうち一方の側のソース/ドレイン領域の電気的連結のための第1コンタクトホール20及び第2コンタクトホール30を絶縁層に形成する段階と、第2コンタクトホール30の内部に相変化物質を蒸着し、温度変化によって電気的連結を選択的に遮断する相変化物質層31を形成する段階と、第1コンタクトホール20及び第2コンタクトホール30を埋め立てる段階と、を含んで半導体素子の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】ハロー領域により短チャネル効果を抑制し、且つ接合リーク電流の発生や接合容量の増加を抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、Si基板と、前記Si基板上にゲート絶縁膜を介して形成されたゲート電極と、前記Si基板の前記ゲート電極の下方に形成されたチャネル領域と、前記チャネル領域を挟んで形成されたソース・ドレイン領域と、前記チャネル領域を挟んで形成され、導電型不純物を含まない第1のエピタキシャル成長結晶からなるエピタキシャル層と、前記チャネル領域と前記エピタキシャル層の間に形成され、導電型不純物を含む第2のエピタキシャル成長結晶からなる、前記ソース・ドレイン領域と異なる導電型のハロー領域と、を有する。

(もっと読む)

21 - 40 / 66

[ Back to top ]