Fターム[5F140BK24]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース、ドレイン電極形成前の処理 (1,173)

Fターム[5F140BK24]の下位に属するFターム

コンタクトホールの形成 (1,071)

Fターム[5F140BK24]に分類される特許

101 - 102 / 102

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

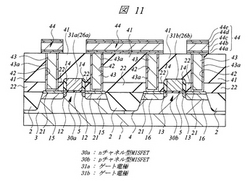

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

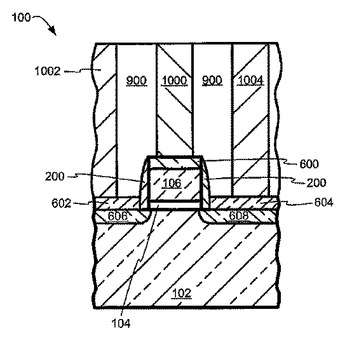

シリサイド成長ドーパント雪かき効果の使用による、デバイス中に階段接合の形成

トランジスタ(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に絶縁層(702)をたい積する。その後、絶縁層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

101 - 102 / 102

[ Back to top ]