Fターム[5F140BK24]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース、ドレイン電極形成前の処理 (1,173)

Fターム[5F140BK24]の下位に属するFターム

コンタクトホールの形成 (1,071)

Fターム[5F140BK24]に分類される特許

21 - 40 / 102

半導体装置の製造方法

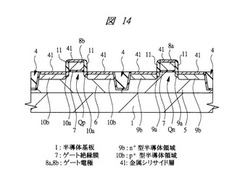

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置とその製造方法

【課題】 窒化物半導体層のヘテロ接合を有する半導体装置において、動作温度の上昇に伴うドレイン電流の減少を低減できる半導体装置とその製造方法を提供する。

【解決手段】 HEMT100は、アンドープのGaN層2とn型のAlGaN層4が順に積層されている半導体基板5と、半導体基板5の表面に形成されているソース電極6、ドレイン電極10と、ソース電極6とドレイン電極10の間に形成されているゲート電極8を備えている。半導体基板5の表面には、ソース電極6とドレイン電極10を結ぶ方向に伸びる第1側面12aと、第1側面に直交する方向に伸びる第2側面12bを形成する複数の凹部14群が形成されている。ゲート電極8は、第1側面12aと第2側面12bを被覆している。HEMT100では、メサ型の伝導チャネルが並列に接続されている。

(もっと読む)

炭化珪素半導体装置

【課題】ゲート絶縁膜の信頼性が向上した炭化珪素半導体装置を提供する。

【解決手段】第1と第2の主面を有する炭化珪素基板(101)と、炭化珪素基板の第1の主面に設けられた第1導電型の炭化珪素層(102)と、炭化珪素層の表面に設けられた第2導電型の第1の炭化珪素領域(103)と、第1の炭化珪素領域内の表面に設けられた第1導電型の第2の炭化珪素領域(104)と、炭化珪素層、第1の炭化珪素領域、及び第2の炭化珪素領域が連続して連なる部分に跨るように選択的に設けられたゲート絶縁膜(105)と、ゲート絶縁膜上に形成されたゲート電極(106)と、第2及び第1の炭化珪素領域の隣接する部分に選択的に設けられたトレンチに埋め込まれた第1の電極(108)と、炭化珪素基板の前記第2の主面に形成された第2の電極(107)とを具備する。

(もっと読む)

ダイヤモンド電界効果トランジスタ

【課題】最大ドレイン電流密度が高く、長時間の電力動作にも耐える信頼性の高い、実用的なダイヤモンド電界効果トランジスタを提供すること。

【解決手段】p型またはn型の伝導性を有するダイヤモンド結晶層1をCVD装置などで成長させる。次に、金を蒸着させ、ソース電極2、ドレイン電極3を形成する。次に、76Torrに減圧したCVDチャンバ内で、上記ダイヤモンド結晶層1に、酸素ガス、水素ガス、トリメチルアルミニウムを供給し、ソース電極2とドレイン電極3との間のゲート部に厚さ8nmのAl(OH)3またはAl1-x-yOxHy化合物からなる絶縁層4を形成する。最後に、絶縁層4上にAl金属膜6を蒸着させてゲート部を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造技術において、同一基板上に金属シリサイド膜厚の異なる領域を作り分ける。

【解決手段】シリコン基板1の主面f1の第1領域R1に第1トランジスタQ1を、同第2領域R2に第2トランジスタQ2を形成する。その後、主面f1に保護酸化膜PT1を形成し、第1ドライエッチングDE1を施すことで、第1領域R1および第2領域R2を覆う保護酸化膜PT1を除去する。その後、第1ドライエッチングDE1よりも低い高周波パワーで、かつ、炭素、水素およびフッ素の化合物を含まないガスを用いた第2ドライエッチングDE2を、第2領域R2に対して施す。その後、シリコン基板1の主面f1上に金属膜M1を堆積し、熱処理を施すことで、金属シリサイド膜scを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタのゲート電極、及びp型MISトランジスタのゲート電極の双方を精度良く実現する。

【解決手段】第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され、シリコン膜14aとシリコン膜14a上に形成された第1の金属シリサイド膜20aとからなる第1のゲート電極26aとを備え、第2のMISトランジスタは、半導体基板10における第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され、フルシリサイド化された第2の金属シリサイド膜20Bからなる第2のゲート電極26bとを備え、第1の金属シリサイド膜20aは、第2の金属シリサイド膜20Bに比べて膜厚が薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】高濃度拡散層の上部にシリサイド膜を有する半導体装置において、リーク電流の発生を防止する。

【解決手段】第1のMOSトランジスタは、活性領域300xにおける第1のサイドウォールスペーサ305aの外側方下に形成された第1の高濃度拡散層306aと、第1の高濃度拡散層306aの上部に形成された第1のシリサイド膜311aとを備え、第2のMOSトランジスタは、活性領域300xにおける第2のサイドウォールスペーサ305bの外側方下に形成された第2の高濃度拡散層306bと、第2の高濃度拡散層306bの上部に形成された第2のシリサイド膜311bとを備え、第1のシリサイド膜311a及び第2のシリサイド膜311bを構成する結晶粒の結晶粒径は、第1のサイドウォールスペーサ305aと第2のサイドウォールスペーサ305b間の間隔以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、NiSiの潜り込み成長を抑え、オフリーク電流の増加を抑制できる半導体装置を提供することを目的とする。

【解決手段】本発明の1実施形態は、シリコン基板1上に形成されるソース領域及びドレイン領域と、ソース領域とドレイン領域との間にゲート絶縁膜3を介して形成されるゲート領域とを備える半導体装置である。さらに、本発明の1実施形態は、少なくともソース領域及びドレイン領域上に成膜した所定の添加金属を含むニッケル膜10を、Ni2Si膜へと反応させる温度でアニールし、さらにNiSi膜へと反応させる温度でアニールして形成されたシリサイド膜22を備える。

(もっと読む)

半導体装置の製造方法

【課題】エッチング処理によるダメージを修復してオーミック電極を形成する。

【解決手段】半導体装置の製造方法は、p型窒化物半導体の表面に異種の表面層を形成する表面層形成工程と、その表面層の一部を除去してp型窒化物半導体の表面を露出させるエッチング工程と、エッチング工程後のp型窒化物半導体を加熱処理するアニール工程と、アニール工程後のp型窒化物半導体の表面に電極を形成する電極形成工程を備えている。前記アニール工程は、700℃から1200℃の窒素又は酸素雰囲気下で実施することを特徴とする。

(もっと読む)

接点抵抗が改善された半導体構造およびその製造方法(接点抵抗が改善された半導体構造)

【課題】 構造の接点抵抗を改善した、すなわち低下させた半導体構造を提供する。

【解決手段】 自己組織化・ポリマー技術を用いて、半導体構造の導電性コンタクト領域に存在する材料内に少なくとも1つの配列されたナノサイズ・パターンを形成する。配列されたナノサイズ・パターンを有する材料は、相互接続構造または電界効果トランジスタの半導体ソースおよびドレイン領域の導電材料である。接点領域内に整列ナノサイズ・パターニング材料が存在することによって、以降の接点形成のための全領域(すなわち界面領域)が拡大し、これによって構造の接点抵抗が低下する。接点抵抗の低下により、構造を通る電流が改善する。上述のことに加えて、本発明の方法および構造では、接合領域が不変のままであるので、構造の接合容量は影響を受けない。

(もっと読む)

ジャーマナイド薄膜、ジャーマナイド薄膜の作成方法、ジャーマナイド薄膜を備えたゲルマニウム構造体

【課題】低抵抗かつ熱的安定性に優れた、ジャーマナイド薄膜を提供する。

【解決手段】ゲルマニウム(Ge)基板11上に、Pt薄膜12が形成され、さらにPt薄膜12の上方にNi薄膜13が形成されている。その後、熱処理を加えることによって、Ge基板上にNi、Pt、Geの三元素からなる(Ni1-xPtx)Ge薄膜が形成された。ジャーマナイド薄膜を構成する結晶粒の結晶面方位が、前記ゲルマニウム基板の[110]結晶面に対して、[102]面あるいは[001]面を平行とする配向関係になっている。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、各ゲートについて均一で十分なフル・シリサイド化を実現する、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極の表層部分及びソース/ドレイン領域16a,16bの表層部分がシリサイド化されている状態において、半導体基板1にフラッシュランプアニールを施す。この処理により、ソース/ドレイン領域16a,16bには(NiPt)2Si層19bが形成された状態が保持されて、ゲート電極のみが選択的にフル・シリサイド化され、フル・シリサイドゲート電極21が形成される。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

CMOS装置の製造工程におけるコンタクト不良発生を抑制する。

【解決手段】

半導体装置の製造方法は、(a)Si基板に、n型の第1の活性領域、p型の第2の活性領域を形成する工程と、(b)活性領域に、第1、第2のゲート電極構造、第1、第2のソース・ドレイン領域をそれぞれ形成する工程と、(c)第1のソース/ドレイン領域に、凹部を形成する工程と、(d)凹部にSi−Geを含むp型の圧縮応力を有する半導体エピタキシャル層を形成する工程と、(e)半導体基板上に引張応力を有する窒化シリコンのエッチストッパ膜、層間絶縁膜を形成する工程と、(f)層間絶縁膜、エッチストッパ膜を貫通して、コンタクト孔をエッチングする工程と、(g)半導体基板上方に酸素を含むプラズマを発生する工程と、(h)コンタクト孔に導電性プラグを埋め込む工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細ショットキーMISFETのソース電極がチャネル端の表面ポテンシャルをピニングすることで発生するトランジスタ性能の劣化を防止する。

【解決手段】ショットキーMISFETを構成する、半導体基板上に形成したソース金属電極8と半導体基板中のチャネル領域11との接触で形成されるショットキー障壁高さとφB0、半導体基板のバンドギャップEGと、半導体基板の真性キャリア濃度niと、デバイスの動作温度Tと、ボルツマン係数kに対して、少なくともソース電極と接するチャネル端近傍の不純物濃度NCHを、NCH≦ni・exp((qφB0−0.5EG)/kT)の条件を満たすようにする。

(もっと読む)

半導体装置

【課題】最も外側の溝部の下端部の外側部分近傍に電界集中が発生するのを抑制することが可能な半導体装置を提供する。

【解決手段】このパワーMOSFET(半導体装置)100は、ドレイン領域2と、ドレインドリフト領域3と、ドレイン領域2の引き出し部15と、ドレインドリフト領域3上に形成されたベース領域9と、ベース領域9上に形成されたソース領域10と、ソース領域10およびベース領域9と一方側面61aが隣接するように形成された溝部6a内に、ゲート絶縁膜7を介して形成されたゲート電極8と、溝部6aと引き出し部15との間において、溝部6aの他方側面62aと隣接するように形成されるとともに、溝部6aの下端部63aよりも下方に延びるように形成された不純物領域11とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の完全シリサイド化とソース/ドレイン拡散層の表面シリサイド化とを同時に行うことが可能で、これにより製造工程数を削減して製造コストの低減を図ることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上にpolySiゲート電極7をパターン形成する。次にpolySiゲート電極7脇の半導体基板1の表面層にソース/ドレイン拡散層19を形成する。また、polySiゲート電極7の側壁に絶縁性のサイドウォール21aを形成する。またソース/ドレイン拡散層19の表面に選択的に酸化膜31を形成する。以上の後、酸化膜31で覆われたソース/ドレイン拡散層19上、およびサイドウォール21aが形成されたpolySiゲート電極7を覆う状態で金属膜35を成膜し、熱処理を行うことによってpolySiゲート電極7をフルシリサイド化させると共に、酸化膜31下のソース/ドレイン拡散層19の表面層をシリサイド化してシリサイド層37を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の全領域がシリサイド化されたMISトランジスタを備える半導体装置の性能を向上させる技術を提供する。

【解決手段】MISトランジスタのゲート絶縁膜502、ゲート電極503及びソース・ドレイン領域506を半導体基板501に形成し、ソース・ドレイン領域506上に、シリサイド反応に必要な金属の拡散を抑制する拡散抑制膜511を形成する。そして、ゲート電極上503及び拡散抑制膜511上に、当該拡散抑制膜511が拡散を抑制する金属から成る金属膜531を形成する。その後、金属膜531とゲート電極503とを反応させて、ゲート電極503の全領域をシリサイド化するとともに、拡散抑制膜511を介して金属膜531とソース・ドレイン領域506とを反応させて、ソース・ドレイン領域を506シリサイド化する。

(もっと読む)

半導体装置の製造方法

【課題】シリコンから構成される導電パターンの下から上までの幅を均一化すること。

【解決手段】半導体基板1上に絶縁膜5を介して第1シリコン膜6を形成し、第1シリコン膜6に高濃度で一導電型不純物を導入し、第1シリコン膜6上に第2シリコン膜9を形成し、第2シリコン膜9上に所定パターンのマスク10mを形成した後、マスク10mから露出する領域で、第1シリコン膜6が露出しない深さまで第1条件により第2シリコン膜9をエッチングし、ついで第1条件に比べて半導体基板1の垂直方向へのエッチング成分の高い第2条件によって第2シリコン膜9の残りと第1シリコン膜6を絶縁膜5が露出しない深さまでエッチングし、さらに第2条件に比べて絶縁膜に対する第1シリコン膜6のエッチング選択比が大きな第3条件により第1シリコン膜6の残りをエッチングする工程とを有している。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】パワーデバイスなどへの適用に適したIII族窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この電界効果トランジスタにおける窒化物半導体積層構造部5には、n型GaN層6、p型GaN層7およびn型GaN層8に跨る壁面16を側面とするメサ状積層部15が形成されている。メサ状積層部15の壁面16には、ゲート絶縁膜9が形成され、このゲート絶縁膜9上にはゲート電極10が形成されている。また、n型GaN層6(引き出し部19)にはドレイン電極12が形成され、n型GaN層8の上面にはソース電極11が形成されている。そして、メサ状積層部15は、窒化物半導体積層構造部5に形成された高転位領域18および低転位領域17のうち、低転位領域17に形成されている。

(もっと読む)

21 - 40 / 102

[ Back to top ]