Fターム[5F140BK28]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400)

Fターム[5F140BK28]の下位に属するFターム

Fターム[5F140BK28]に分類される特許

81 - 83 / 83

ゲルマニウム基板タイプ材料およびその手法

ゲルマニウム回路タイプの構造が促進される。一実施形態例では、多段階の成長およびアニール・プロセスを実施して、ヘテロエピタキシャルル・ゲルマニウムなどのゲルマニウム(Ge)含有材料を、シリコン(Si)またはシリコン含有材料を含む基板上に成長させる。いくつかの応用例では、ゲルマニウム含有材料の上面に向かって貫通する欠陥が全体的に抑制されて、欠陥が全体的にシリコン/ゲルマニウム境界面付近に閉じ込められる。これらの手法は、ゲルマニウムMOSコンデンサ、pMOSFET、およびオプトエレクトロニック・デバイスを含む、さまざまなデバイスに適用できる。  (もっと読む)

(もっと読む)

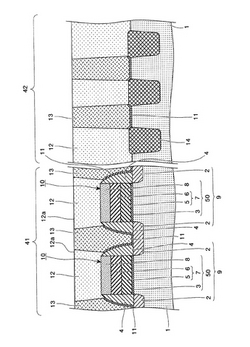

半導体装置および半導体装置の製造方法

【課題】半導体装置の更なる微細化に対応可能な、微細化されたコンタクトが確実に形成された素子特性に優れ、歩留まりの良い半導体装置、およびその製造方法を得る。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極を覆うエッチング保護膜を形成する工程と、前記エッチング保護膜を覆うように前記半導体基板上にバリアメタル層を形成する工程と、前記バリアメタル層上に導電性材料を堆積して導電性膜を形成する工程と、前記導電性膜上にレジストマスクを形成する工程と、前記レジストマスクをエッチングマスクとして前記導電性膜を選択的にエッチング除去してコンタクトを形成する工程と、前記レジストマスクを除去する工程と、前記半導体基板上における前記導電性膜がエッチング除去された領域に絶縁性材料を堆積して層間絶縁膜を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

81 - 83 / 83

[ Back to top ]