Fターム[5F140BK28]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400)

Fターム[5F140BK28]の下位に属するFターム

Fターム[5F140BK28]に分類される特許

41 - 60 / 83

炭化珪素半導体装置の製造方法および炭化珪素半導体装置

【課題】信頼性を向上できる炭化珪素半導体装置の製造方法および炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置の製造方法は、以下の工程を備えている。まず、主面110aを含む炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の主面110aにシリコンをドーピングして、炭化珪素半導体層に110おいてシリコンがドーピングされていない領域よりもシリコン濃度の高い高濃度領域115が形成される。そして、高濃度領域115と接する位置に、シリコンと化合物を生成する材料を含む金属層143、144が形成される。そして、金属層143、144を熱処理して、化合物を含む電極が形成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極、ソース電極またはドレイン電極にタングステン膜を用いた半導体装置において、nMOSとpMOS間での抵抗差を低減可能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極14a,14bとソース/ドレイン拡散層16a,16bとを有するnMOS及びpMOSを形成し、ゲート電極14a,14b及びソース/ドレイン拡散層16a,16b上に、タングステン膜17を選択的に形成し、タングステン膜17を覆うように、絶縁膜(エッチングストップシリコン酸化膜18、シリコン窒化膜19)を形成し、pMOS領域12bの絶縁膜を除去し、pMOS領域12bのタングステン膜17上に、タングステン膜20を選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、光吸収膜を利用して実行する新たな製造方法を提供する。

【解決手段】基板上に光吸収膜を堆積し、前記光吸収膜を加工して、第1の膜厚の前記光吸収膜で覆われた第1領域と、前記第1の膜厚よりも薄い第2の膜厚の前記光吸収膜で覆われた第2領域と、前記第2の膜厚よりも薄い第3の膜厚の前記光吸収膜で覆われた第3領域とを形成し、前記基板に光を照射することにより、前記基板をアニールすることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置及びその製造方法

【課題】III族窒化物半導体からなるトランジスタにおける相互コンダクタンスを向上しながら、ソース抵抗を小さくできるようにする。

【解決手段】半導体装置は、AlGaNからなる障壁層104と、該障壁層104の上に形成され、AlGaN/GaNの超格子層105を含み且つ障壁層104を露出するゲートリセス108を有するキャップ層107と、該キャップ層107の上にゲートリセス108を挟んで対向するように形成されたソース電極110及びドレイン電極111とを有している。少なくとも障壁層104におけるゲートリセス108からの露出部分の上には絶縁膜109が形成され、ゲートリセス108の底面上には、絶縁膜109を介在させてゲート電極112が形成されている。

(もっと読む)

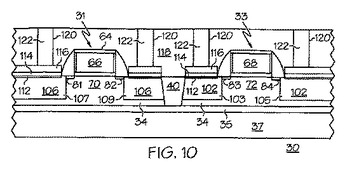

歪みが強化された半導体デバイスとその製造方法

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】コプラス時オン抵抗を低減化し、かつゲート漏れ電流を低減化した半導体装置を提供する。

【解決手段】窒化物系化合物半導体層(3,4)上に窒化物系化合物半導体層(3,4)とショットキー接触するゲート電極7と、ゲート電極7上に形成された第1の絶縁膜18と、ゲート電極7から離間した窒化物系化合物半導体層(3,4)上に窒化物系化合物半導体層(3,4)と低抵抗接触するソース電極5と、ゲート電極7と第1の絶縁膜18を介して形成され、ソース電極5と電気的に接続し、平面的に見て、ゲート電極7の上を跨ぐように延伸しているソースFP電極9と、ソースFP電極9上に形成された第2の絶縁膜10とを有する半導体装置であって、ソースFP電極9の厚みはソース電極5の厚みよりも厚く形成されている。

(もっと読む)

半導体素子

【課題】しきい値電圧を増大させることなくバッファ層を高抵抗化して素子を高耐圧化できること。

【解決手段】電界効果トランジスタ100は、基板1上にバッファ層2,3、半導体動作層4、ゲート絶縁膜5Gaおよびゲート電極5Gbを順次積層して備え、バッファ層3内にあってこのバッファ層3の積層面に平行な所定面内の転位密度は、この転位密度に対するバッファ層3の体積抵抗率が極大値近傍となる密度値とされ、具体敵意は2.0×108cm-2以上、7.0×1010cm-2以下とされている。

(もっと読む)

銀を含む配線を有する半導体構造及びその形成方法

半導体構造の形成方法は、絶縁材料からなる層(210)を備えた半導体基板を設ける。絶縁材料からなる層内には凹部が設けられている。凹部には銀を含む材料(216)が充填されており、場合によってはロジウム(214),(217)で被覆されている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 ソース/ドレインの横方向拡散を確実に抑止し、更なる微細化及び高性能化の要請を満たし、信頼性の高い半導体装置を実現する。

【解決手段】 ゲート電極2をマスクとしたイオン注入によりエクステンション領域3を形成した後、ゲート電極2及び第1のサイドウォール4をマスクとして、ソース/ドレイン5の不純物の拡散抑制機能を有する物質をイオン注入し、半導体基板1の表層のサイドウォール4に整合する部位を非晶質化してアモルファス状態の拡散抑制領域6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】GaN層3上に形成された第1の半導体層4上の一部の領域に無機膜5を形成すると共に、無機膜5を介して相互に対向する領域に電極6及び7を形成する。第1の半導体層4はAlGaN層とする。次に、第1の半導体層4上における無機膜5と電極6とに挟まれた領域、及び無機膜5と電極7とに挟まれた領域の各々に、第2の半導体層8を形成する。第2の半導体層8としては、MOCVD法によりAlGaN層を形成する。その後、無機膜5を除去し、凹み9を形成する。次に、絶縁膜10を形成し、凹み9内に電極11を形成する。これにより、半導体装置19が作製される。

(もっと読む)

半導体装置およびその製造方法

【課題】電極の接触抵抗、電極自身の抵抗の低減によって高性能化した電界効果トランジスタを含む半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板200に形成されたチャネル領域106と、ゲート絶縁膜101を介して形成されたゲート電極と、チャネル領域106の両側に形成されたソース電極およびドレイン電極を具備するn型電界効果トランジスタを含み、ソース電極およびドレイン電極が第1の金属のシリサイド110aで形成され、半導体基板200と第1の金属のシリサイド110aとの界面に、第2の金属120aを含有する界面層が形成され、第2の金属120aの仕事関数が第1の金属のシリサイド110aの仕事関数よりも小さく、かつ、第2の金属120aのシリサイドの仕事関数が第1の金属のシリサイド110aの仕事関数よりも小さいことを特徴とする半導体装置およびその製造方法。

(もっと読む)

トレンチ構造を利用した横型高駆動能力半導体装置

【課題】 平面的な素子面積を増加させずに、低オン抵抗の高駆動能力横型のMOSトランジスタを含む半導体装置の製造方法を提供する。

【解決手段】 半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域と、前記第1トレンチ領域の凹部底面と同一平面に前記第1トレンチ領域の長さ方向の両端に接して設けられた第2トレンチ領域および第3トレンチ領域と、前記第1トレンチ領域と前記第2トレンチ領域と前記第3トレンチ領域の少なくとも1領域に形成された第2導電型のウェル領域と、前記第1トレンチ領域に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に接して設けられたゲート電極と、前記第1トレンチと前記第2トレンチ領域と前記第3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド膜を有する半導体装置において、電流集中とリーク電流を共に抑制する。

【解決手段】半導体装置50は、半導体基板上のゲート電極4と、ゲート電極4の側面上のサイドウォールスペーサー7と、半導体基板におけるサイドウォールスペーサー7の外側方のソース領域8S及びドレイン領域8Dと、ソース領域8S上のソース上シリサイド膜5Sと、ドレイン領域8D上のドレイン上シリサイド膜5Dと、ソース領域8S上のソースコンタクト10Sと、ドレイン領域8D上に形成され且つゲート電極4のゲート幅方向に並ぶ少なくとも一対のドレインコンタクト10Dとを備える。一対のドレインコンタクト10D間に位置するドレイン領域8Dのうち、少なくともドレインコンタクト10Dのゲート電極4側の端部位置とサイドウォールスペーサー7との間の領域に、ドレイン上シリサイド膜5Dが形成されていない高抵抗領域30Dが設けられている。

(もっと読む)

AlN障壁層を有するGaN系電界効果トランジスタ、及びそのような電界効果トランジスタの製造方法

【課題】 本発明は、高出力、高耐圧、高速、高周波化などを達成し得る新規なGaN系ヘテロ接合トランジスタを提供することを目的とする。

【解決手段】上記課題は、GaN又はInGaNからなるチャネル層(4)と、AlNからなる障壁層(5)と含むヘテロ界面を構成する層と、トランジスタ素子表面に形成された絶縁膜(9)を有する電界効果トランジスタ(1)、特に絶縁膜としてSiN絶縁膜を用いた電界効果トランジスタや、そのような電界効果トランジスタの製造方法によって解決される。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

複合キャップによりシリサイド形成を改善するためのエア・ブレーク

【課題】 複合キャップによりシリサイド形成を改善するためのエア・ブレーク

【解決手段】 シリサイド応力を調節するための構造体及び方法、具体的にはn−FET性能を最適化するようにn−FETのゲート導体上に引張り応力含有シリサイド領域を造成する(402)ための構造体及び方法が開示される。より具体的には、n−FET構造体の上に第1金属層−保護キャップ層−第2金属層スタックが形成される(403−406)。しかしながら、第2金属層の堆積(406)の前に、保護層を空気に曝す(405)。このエア・ブレークのステップは、保護キャップ層と第2金属層の間の付着性を変化させ、それゆえに、シリサイド形成中に第1金属層に付与される応力に影響を与える。その結果として、n−FET性能に最適な引張り応力のより大きなシリサイドが生成される。さらに、この方法は、このような引張り応力含有シリサイド領域を、比較的薄い第1金属層−保護キャップ層−第2金属層スタック、より具体的には比較的薄い第2金属層を用いて形成することを可能にし、ゲート導体と側壁スペーサの間の接合部に蓄積される機械的エネルギーを最小にしてシリコン・ブリッジ形成を防止する。

(もっと読む)

同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体

【課題】 同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体を提供すること。

【解決方法】 半導体デバイス構造体を製造する方法は、基板(10)を準備するステップと、第1スペーサ(SP)を備える第1ゲート(G1)、第2スペーサ(SP)を備える第2ゲート(G2)、第1ゲート及び第2ゲートに隣接する、同じ導電型のそれぞれのソース(S)/ドレイン(D)領域、第1ゲートと第2ゲートとの中間に配置された分離領域(STI)、及び第1ゲート、第2ゲート、並びにそれぞれのソース及びドレイン領域の上にあるシリサイドを基板上に形成するステップと、中間構造体を製造するために第1スペーサ上に付加的なスペーサ(RSPS)を形成し、次いで、中間構造体全体の上に応力層を配置するステップと、を含む。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 短工期であり低消費電力および高駆動能力、高精度を有するパワーマネージメント半導体装置やアナログ半導体装置の実現を可能とする製造方法を提供する。

【解決手段】 CMOSを含むパワーマネージメント半導体装置やアナログ半導体装置の製造方法において、低濃度ドレインを構成する半導体領域の上方に熱伝導度の大きい物質を付加し、ドレイン領域を拡大することで、サージ入力時でのドレイン領域の熱伝達(熱放出)を向上させることにより局所的な温度上昇を抑えることで、熱破壊を抑止し、トランジスタの設計自由度を高めたパワーマネージメント半導体装置やアナログ半導体装置を実現する。

(もっと読む)

41 - 60 / 83

[ Back to top ]