Fターム[5F140BK32]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | イオン注入 (34)

Fターム[5F140BK32]に分類される特許

1 - 20 / 34

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

可動ゲート型電界効果トランジスタ

【課題】可動ゲート電極の変位を制御可能な可動ゲート型電界効果トランジスタを提供する。

【解決手段】ソース電極17とドレイン電極18との上に導電シールド電極20が配置される可動ゲート型電界効果トランジスタ1とした。そして導電シールド電極20の電位を固定することとした。導電シールド電極20が配置されることにより、可動ゲート15とドレイン電極18またはソース電極17との間に発生する静電力を抑制することができる。

(もっと読む)

半導体装置の製造方法

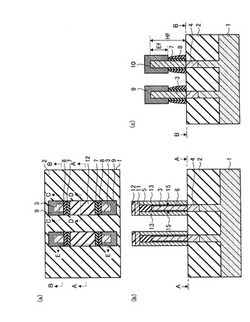

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層上に第1窒化物半導体層および第2窒化物半導体層が順次積層された窒化物半導体積層体と、窒化物半導体積層体の上面に接する、ソース電極およびドレイン電極と、ソース電極およびドレイン電極の間の窒化物半導体積層体における、第1窒化物半導体層の一部および第2窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域上に形成された窒化物半導体膜と、リセス領域の内壁面、および第2窒化物半導体層の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを有し、第2窒化物半導体層は、第1窒化物半導体層に比べて広い禁制帯幅を有し、窒化物半導体膜の上面は、第1窒化物半導体層の上面よりも低いことを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】拡散層とゲート電極との少なくとも1つの上に耐熱性が向上したNiSi膜が形成された半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Si基板200と、Si基板200内に形成された拡散層10と、Si基板200上にSiを用いて形成されたゲート電極20との少なくとも1つと、前記拡散層10と前記ゲート電極20との少なくとも1つ上に接触して形成されたP元素を含有したNiSi膜40,42と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられるNiPtSi電極の熱安定性を向上させる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板と、この半導体基板中のチャネル領域と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、チャネル領域の両側に形成され、NiおよびPtを主成分とする金属半導体化合物層からなるソース/ドレイン電極とを備え、金属半導体化合物層と半導体基板との界面において、金属半導体化合物層の単一の結晶粒と半導体基板との境界部の最大Pt濃度が、界面の平均Pt濃度よりも高いことを特徴とする半導体装置および半導体装置の製造方法。

(もっと読む)

相補型p、及びnMOSFETトランジスタの製造方法、このトランジスタを包含する電子デバイス、及び少なくとも1つのこのデバイスを包含するプロセッサ

ゲート電極(14、28)によって制御されるチャネル(20、34)によって接続される金属ショットキーのソース電極(10、24)、及びドレイン電極(12、26)を有する相補型p、及びnMOSFETトランジスタ(3、4)を製造する方法であって、p、及びnトランジスタの双方のための単一のシリサイドからソース電極、及びドレイン電極を製造することと、相補型nトランジスタ(4)をマスクして、シリサイドと、pトランジスタのチャネル(20)との間の界面(22)における周期表のII族、及びIII族からの第1の不純物(21)を偏析することと、相補型pトランジスタ(3)をマスクして、シリサイドと、nトランジスタのチャネル(34)との間の界面(36)における周期表のV族、及びVI族からの第2の不純物(35)を偏析することと、を有する。 (もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、ソース/ドレイン領域の寄生抵抗の小さい半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、Si層上にゲート部を形成する工程と、ゲート部を挟むSi層に、Asを導入する工程と、Asが導入されたSi層上にNi層を堆積する工程と、熱処理を用いて、Ni層とSi層とを反応させて第1シリサイド層を形成するとともに、第1シリサイド層とSi層との界面にAsを偏析させる工程と、第1シリサイド層中にPt元素を導入する工程と、熱処理を用いて、Pt元素をSi層まで拡散させて第1シリサイド層とSi層との間に第2シリサイド層を形成するとともに、第2シリサイド層とSi層との界面にAsを偏析させる工程と、を備えることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】p型MISFETまたはn型MISEFETを有する半導体装置において、p型MISFETまたはn型MISEFETのソース/ドレイン電極界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板100にp型MISFET200を備える半導体装置であって、p型MISFET200が、半導体基板100中のチャネル領域204と、チャネル領域204上に形成されたゲート絶縁膜206と、ゲート絶縁膜206上に形成されたゲート電極208と、チャネル領域204の両側の、Niを含有するシリサイド層210で形成されたソース/ドレイン電極と、ソース/ドレイン電極と半導体基板100との界面の半導体基板100側に形成された、Mg、CaまたはBaを含有する界面層230を有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 装置規模の拡大を最小限に抑制しながら、高い耐圧性を維持するとともに、現実的な製造プロセスの下で容易に製造が可能な半導体装置を提供する。

【解決手段】 第1絶縁膜3aを貫通するように基板面に直交する深さ方向に形成される導電膜14aと、第2絶縁膜3bの直上層から底面に達するまで一の外側壁に沿って深さ方向に形成される導電膜14bと、導電膜14bの底面の深さ位置から絶縁膜3a及び3bに挟まれた領域に係る基板2の上面位置に亘って、少なくとも導電膜14bの底面及び絶縁膜3bと接触していない側の外側壁と接触して形成される絶縁膜13bと、絶縁膜13bと3bに挟まれた領域内において底面から上面に向かって、第1導電型の第1不純物拡散領域6、第2導電型の第2不純物拡散領域5a、第1導電型の第3不純物拡散領域7、及び高濃度の前記第1導電型の第4不純物拡散領域17bを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の製造において、細線化したゲート電極上のシリサイドにおける凝集の防止および当該シリサイドの薄膜化を両立する。

【解決手段】NMOSトランジスタのゲート電極12並びにソース・ドレイン領域15の上部、およびPMOSトランジスタのゲート電極22並びにソース・ドレイン領域25には、それぞれNiシリサイド膜12s,15s,22s,25sが自己整合的に形成されている。Niシリサイド膜12s,15s,22s,25sは、NiおよびSiを主成分とし、化学量論組成がNiSiあるいはNiSi2である。但しそれらはPt,V,Pd,Zr,Hf,Nbのうち1以上の元素を合計で10at%未満の固溶量で含んでいる。

(もっと読む)

半導体素子およびその製造方法

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

1 - 20 / 34

[ Back to top ]