Fターム[5F140CE12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 露光 (102) | 位置合わせ (12)

Fターム[5F140CE12]に分類される特許

1 - 12 / 12

半導体装置の製造方法

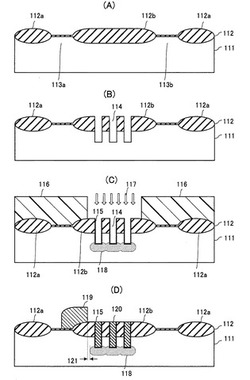

【課題】良好な特性の確保、素子サイズの増加の回避、及び製造プロセスの簡素化を実現できる半導体装置の製造方法を提供する。

【解決手段】Si基板111の主面に、LOCOS酸化膜112bを含む酸化膜112を形成する工程と、Si基板111の主面の側に、ソース・ゲート形成領域113aとドレイン形成領域113bとを形成する工程と、レジスト116をマスクとして、Si基板111の主面の側のLOCOS酸化膜112bで覆われていないトレンチ114を通してイオン117注入を行い、イオン注入層118を形成する工程と、LOCOS酸化膜112b上及びソース・ゲート形成領域113a上を部分的に覆うようにゲート電極119を形成する工程とを有し、イオン注入層118のゲート電極119側の端部とゲート電極119のイオン注入層118側の端部との間に間隔121が存在するように、各工程を行う。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1導電型の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2導電型の不純物層及び第1のエピタキシャル半導体層とは膜厚の異なる第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上に第1のゲート絶縁膜と同じ膜厚の第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

ワイドギャップ半導体基板およびワイドギャップ半導体装置の製造方法

【課題】ワイドギャップ半導体基板の位置検出を、可視光を用いて高精度に行う。

【解決手段】一実施形態によれば、ナローギャップ半導体基板(例えばSi基板2)の主面の所定の位置に彫り込み型のアライメントマーク4が形成されたナローギャップ半導体基板のその主面上にワイドギャップ半導体層(例えばGaN層19)をエピタキシャル成長したことにより、基板位置決め用のアライメントマークが予め埋め込まれているワイドギャップ半導体基板を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】強い圧縮応力を有するシリコン窒化膜を用いたpMISFETを有する半導体装置及びその製造方法において、歩留まりが高く且つスイッチングスピードが高い半導体装置及びその製造方法を提供する。

【解決手段】ボックスマーク102内においてシリコン基板1を覆うようにシリコン酸化膜14を形成する。次に、基板上の半導体領域にシリサイド化反応によりニッケルシリサイド8を形成する。その後、強い圧縮応力を有するシリコン窒化膜9をpMISFET101及びボックスマーク102を覆うように形成する。その上に層間絶縁膜11を形成した後レジストをパターニングしてコンタクトホール13を形成する。この際、重ね合わせ精度が所定の規格を満たすまで、レジストを一旦除去し再度レジスト12bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ノッチ及びオリエンテーションフラット等の結晶方位の指標の精度が十分とはいえない場合であっても、それを補償することができる半導体装置の製造方法を提供する。

【解決手段】ノッチ等の指標のずれに対する補正値を決定する。この補正値決定処理では、先ず、処理の対象となっているすべての半導体基板に対し、各半導体基板における角度の誤差を測定する(ステップS101)。各半導体基板について測定した角度の誤差の統計処理を行う(ステップS102)。具体的には、角度の誤差の「オフセット値」及び「ばらつきの大きさ」を求める。そして、ばらつきの大きさが所定範囲内にあれば、オフセット値の符号を反転したものを各半導体基板の補正値として決定し(ステップS103、S104)、外れていれば、半導体基板毎に、測定された角度の誤差の符号を反転したものを補正値として決定する(ステップS103、ステップS105)。

(もっと読む)

光及び電子ビーム・リソグラフィ混合製造レベルの共通位置合わせ用のトレンチ構造体及び方法

【課題】 光リソグラフィ及び電子ビーム・リソグラフィ混合製造レベルの共通位置合わせ用の位置合わせターゲット及び方法を提供すること。

【解決手段】 集積回路チップの製造レベルの構造部の第1の組を、基板内に形成された電子ビーム位置合わせターゲットに位置合わせして、電子ビーム・リソグラフィを用いて構造部の第1の組を形成し、そして、集積回路チップの同じ製造レベルの構造部の第2の組を、基板内に形成された光位置合わせターゲットに位置合わせして、フォトリソグラフィを用いて構造部の第2の組を形成する方法であって、光位置合わせターゲット自体は電子ビーム位置合わせターゲットに位置合わせされる、方法を提供する。また、電子ビーム位置合わせターゲットを形成する方法及び構造体を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 斜めイオン注入工程でイオン注入できない影領域を安定して低減させ、微細化に好適な構造を有する半導体装置およびその製造方法を提供する。

【解決手段】 p型ウェル領域12を第1および第2領域に区画するように絶縁分離層13を形成する工程と、絶縁分離層13と離間して第1領域12aに設けられた第1ゲート電極16と、絶縁分離層13と第2領域12bとに跨がり、且つ第1ゲート電極16と相対向する第2ゲート電極17とを同時に形成する工程と、第2ゲート電極17の一端をマスクとして垂直方向より所定角度傾けた方向からp型不純物イオンを第1領域12aに注入し、更に垂直方向よりn型不純物イオンを注入してソース/ドレイン領域19、20を形成する工程と、第2ゲート電極17の他端をマスクとして第2領域12bにウェルコンタクト層21を形成する工程を有している。

(もっと読む)

半導体ウエハ、半導体装置、及び半導体装置の製造方法

【課題】 半導体基板と電子ビーム露光装置との位置合わせを容易に行うことができる半導体ウエハ、半導体装置、及び半導体装置の製造方法を提供すること。

【解決手段】 ゲート電極17aと導電膜17のそれぞれの上と第1開口17b内に層間絶縁膜25を形成する工程と、第1開口17bを含む第2開口25aを層間絶縁膜25に形成する工程と、第1開口17bの下の素子分離絶縁膜14に穴14aを形成する工程と、レジスト28が塗布された状態で第1開口17bと穴14aとを位置合わせ用のマーク27として使用し、該マーク27からの反射電子EBrefの強度を測定して電子ビーム露光装置とシリコン基板10との位置合わせを行う工程と、第1領域Iのホール形成領域にあるレジスト28を電子ビームEBで露光する工程と、レジスト28を現像してレジストパターン28eにする工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】 従来の半導体装置の製造方法では、素子形成領域の平坦性を維持しつつ、遮光性の膜に対するアライメントマークを形成することが困難であるという問題があった。

【解決手段】 本発明の半導体装置の製造方法では、エピタキシャル層5表面から溝部9を形成する。溝部9をNSG膜で埋設し、CMP法により研磨することで、エピタキシャル層5表面を平坦面とすることができる。そして、スクライブライン領域2では、第1の段差部10の一部を露出するように、NSG膜11の一部を除去する。この工程により、多結晶シリコン膜22に対し、第2の段差部23を形成することができ、該第2の段差部23をアライメントマークとして利用することができる。

(もっと読む)

不透明なゲート層の位置合わせ用マーカ、このようなマーカの製作方法、及びリソグラフィ機器でのこのようなマーカの使用

【課題】順に繰り返して配置されたライン要素及びトレンチ要素を含むマーカ構造を製作する方法を提供すること。

【解決手段】この方法は、トレンチ要素に二酸化シリコンを充填し、マーカ構造を平坦化するステップを含む。半導体表面上で犠牲酸化物層を成長させ、ライン要素の第1サブセットを、ドーパント種を含むイオン注入ビームに露出させて、この第1サブセットをドープし、そのエッチング速度を変化させる。この基板をアニールしてドーパント種を活性化させ、半導体表面をエッチングして犠牲酸化物層を取り除き、第1サブセットを第1レベルの高さにし、第1サブセットが、第1サブセットと異なるマーカ構造表面部分の第2レベルと異なる第1レベルを有するようにトポロジーを生成する。

(もっと読む)

1 - 12 / 12

[ Back to top ]