Fターム[5F140DA10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 保護 (215) | センサー、温度、電流検知 (12)

Fターム[5F140DA10]に分類される特許

1 - 12 / 12

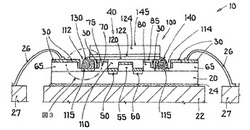

半導体ガスセンサ

【課題】従来技術を発展させた半導体ガスセンサを提供すること。

【解決手段】第1の端子部分が、半導体本体(20)の表面に設けられたパッシベーション層(30)を貫通する第1の成形部分(112)を有し、該第1の成形部分(112)は、参照電位に接続された導電性層(115)を備えた底面を有し、該第1の端子部分と制御電極(100)とは第1の接合材(130)を用いて電気的接続かつ摩擦接続的に結合されている。第2の端子部分と前記制御電極(100)とは第2の接合材(140)を用いて少なくとも摩擦接続的に結合されており、前記第1の接合材(130)は前記成形部分を少なくとも部分的に充填し、前記制御電極(100)と前記導電性層(115)とを接続する。

(もっと読む)

可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置

【課題】可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置を提供する。

【解決手段】熱によるFETのソース及びドレイン間の電流減少の問題を効果的に解決し、またFETの温度を低めることができる可変ゲートFET及びこのFETを備える電気電子装置を提供し、可変ゲートFETは、FETと、FETの表面または発熱部分に取り付けられ、回路的には、FETのゲート端子に連結されておりゲート端子の電圧を変化させるゲート制御素子と、を備え、FETの温度が所定温度以上に上昇しているときに、ゲート制御素子が、ゲート端子の電圧を変化させて、FETのソース及びドレイン間のチャンネル電流を制御する。

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

半導体装置

【課題】製造工程を変更することなくMOSトランジスタのドレイン電流−温度特性を制御する。

【解決手段】半導体層1に互いに間隔をもって形成されたソース11s及びドレイン11d,13dと、ソース11sとドレイン11d,13dの間の半導体層1上にゲート絶縁膜5を介して形成されたゲート電極7とをもつMOSトランジスタを備えている。MOSトランジスタで、ソース11sは上方から見てゲート電極7とは間隔をもつ位置に形成されている。ドレイン13dは上方から見てゲート電極7に一部重複する位置に形成されている。上方から見たソース11sとゲート電極7の間の距離AはMOSトランジスタが温度上昇に対してドレイン電流が増加するドレイン電流−温度特性をもつ寸法に設定されている。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】入力電圧ライン11と誘導性負荷Lとの間に接続される第1のスイッチング素子M1を有するハイサイドスイッチング素子と、誘導性負荷Lと基準電圧ラインとの間に並列接続される第2のスイッチング素子M2と第3のスイッチング素子M3とを有するローサイドスイッチング素子と、を備え、ローサイドスイッチング素子における誘導性負荷Lに接続される端子にサージが印加されたとき、サージ電流は第3のスイッチング素子M3を介して基準電圧ラインへと放電される。

(もっと読む)

高耐圧半導体スイッチング素子

【課題】センス比のコレクタ電流依存性をスイッチング素子自体の構造により制御する。

【解決手段】P型のベース領域2の表面部に、少なくとも1つのN型のエミッタ領域3及びエミッタ領域3と離隔した少なくとも1つのN型のセンス領域5が選択的に形成されている。エミッタ領域3及びセンス領域5は、コレクタ領域7からベース領域2に向かう第1の方向に対して垂直な第2の方向に並ぶように配置されている。センス比がコレクタ電流の変化に対応して所望の変化を生じるように、第2の方向におけるセンス領域5、エミッタ領域3、センス領域5に隣接する部分のベース領域2、及びエミッタ領域3に隣接する部分のベース領域2のそれぞれの幅が設定されている。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子の熱による素子欠陥及び破壊を未然に防止するのに適した半導体素子及びその製造方法を提供する。

【解決手段】ウェハー上にトランジスタ10を形成する段階と、トランジスタ10の上部に絶縁層を形成する段階と、トランジスタ10の両側のソース/ドレイン領域のうち一方の側のソース/ドレイン領域の電気的連結のための第1コンタクトホール20及び第2コンタクトホール30を絶縁層に形成する段階と、第2コンタクトホール30の内部に相変化物質を蒸着し、温度変化によって電気的連結を選択的に遮断する相変化物質層31を形成する段階と、第1コンタクトホール20及び第2コンタクトホール30を埋め立てる段階と、を含んで半導体素子の製造方法。

(もっと読む)

半導体装置

【課題】横型IGBTに対する過電流保護機能を有する半導体装置において、過電流保護機能が働く電流値のバラツキを低減する。

【解決手段】ゲート電圧により制御可能な主スイッチング素子である横型IGBT1と、電流検出用横型IGBT10とが並列に接続されている。電流検出用横型IGBT10ののベース領域109と、横型IGBT1のエミッタ領域106とが電気的に接続されている。電流検出用横型IGBT10のエミッタ領域108と、横型IGBT1のエミッタ領域106とが、電流検出回路7のセンス抵抗4を介して電気的に接続されている。

(もっと読む)

高耐圧IC

【課題】高耐圧第二領域を設け、縦型パワーデバイスの高耐圧接合終端構造、集積回路ユニット間を分離する高耐圧接合終端構造、nチャネルまたはpチャネルの高耐圧横型MOSFETの高耐圧接合終端構造などとし、配線が横切っても耐圧が低下せずに高耐圧が維持でき、かつ製造コストの低い高耐圧ICを提供すること。

【解決手段】第一の出力配線61と第二の出力配線62下の電界強度を弱めるために、GDU1を取り囲む第一の高耐圧接合終端構造HVJT1と、GDU1内およびLSU内に形成される横型MOSFETを取り囲む第二の高耐圧接合終端構造HVJT2とが同一構造の高耐圧接合終端構造HVJTで構成され、かつ一体となっている。

(もっと読む)

同一電界効果トランジスタを利用して生分子を検出する方法

【課題】同一電界効果トランジスタを利用して生分子を検出する方法を提供する。

【解決手段】電界効果トランジスタを利用した生分子検出方法において、電界効果トランジスタは、半導体基板、基板と異なる電導型にドーピングされたソース領域及びドレイン領域、ソース領域とドレイン領域との間に配置されたチャネル領域、チャネル領域上に配置され、生分子を検出する検出表面を有する絶縁層、絶縁層の検出表面から離隔されて配置された基準電極を備えることを特徴とし、生分子を含有する第1試料を、前記電界効果トランジスタの検出表面に提供し、前記電界効果トランジスタの第1電気信号の変化を測定するステップと、第2試料を同一の前記電界効果トランジスタの検出表面に提供し、前記電界効果トランジスタの第2電気信号の変化を測定するステップと、前記第1電気信号と前記第2電気信号とを比較するステップと、を含む生分子の検出方法である。

(もっと読む)

イオン物質検出用電界効果トランジスタ及びそれを用いたイオン物質検出方法

【課題】イオン物質検出用電界効果トランジスタを提供する。

【解決手段】半導体材料で構成される基板21と、前記基板内に互いに離隔されて形成され、基板と反対極性にドーピングされたソース領域22及びドレイン領域23と、ソース領域及びドレイン領域の間に配置されるチャネル領域24と、チャネル領域上に配置され、電気的絶縁材料で構成される絶縁層25と、絶縁層上部のエッジに配置される一次基準電極26と、絶縁層から離隔されて配置される二次基準電極27を備える。

(もっと読む)

電流検出電極を有するIII族窒化物半導体装置

【課題】電流の状態に関する情報を提供する能力を有するように配置されたIII族窒化物ベースの電力半導体装置を提供することである。

【解決手段】本発明の電力半導体装置は、III族窒化物ヘテロ接合領域と、該III族窒化物ヘテロ接合領域及び第1給電パッドに電気的に接続される第1電力電極と、前記III族窒化物ヘテロ接合領域及び第2給電パッドに電気的に接続される前記第1電力電極に対向して離隔される第2電力電極と、前記III族窒化物ヘテロ接合領域及び第3給電パッドに電気的に接続される前記第1電力電極に対向して離隔される第3電力電極と、を有する電力半導体装置。

(もっと読む)

1 - 12 / 12

[ Back to top ]