Fターム[5F152CD23]の内容

再結晶化技術 (53,633) | 被結晶化層の下方の層 (4,095) | 形状(結晶化直前の状態) (465) | 断面形状、厚さ (75)

Fターム[5F152CD23]に分類される特許

1 - 20 / 75

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域308と、前記島状の半導体領域308の側面及び上面を覆って設けられたゲート絶縁膜310と、前記ゲート絶縁膜310を介して前記島状の半導体領域308の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域308の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

EL表示装置の作製方法

【課題】画素構造を最適化することにより、開口率を向上させたEL表示装置を提供する。

【解決手段】スイッチング用TFTのゲート電極に近接して設けられた半導体層と、電流制御用TFTのゲート電極に近接して設けられた半導体層と、スイッチング用TFTのゲート電極および電流制御用TFTのゲート電極と同一面上に設けられたソース配線と、スイッチング用TFTのゲート電極、電流制御用TFTのゲート電極、およびソース配線を覆う絶縁膜と、ソース配線および前記スイッチング用TFTの半導体層に電気的に接続された第1の接続配線と、電流制御用TFTのゲート電極および前記スイッチング用TFTの半導体層に電気的に接続された第2の接続配線と、電流制御用TFTの半導体層と電気的に接続された画素電極と、発光層と、画素電極と対向する電極とを有するEL素子とを有するEL表示装置。

(もっと読む)

撮像装置、表示撮像装置および電子機器

【課題】製造工程を複雑化させることなく、光検出素子および駆動素子において高い特性を示すことが可能な撮像装置、表示撮像装置および電子機器を提供する。

【解決手段】光検出素子3におけるI層32I(チャネル領域,半導体層)と、TFT素子2におけるI層22I(チャネル領域,半導体層)とにおいて、それらの厚みおよび不純物濃度がそれぞれ互いに略等しくなっている。I層22I,32Iにおける平均トラップ順位密度がそれぞれ、2.0×1017(cm-3)以下となっている。2種類の半導体層(I層22I,32I)を、同一の工程で簡易に形成することができる。また、光検出素子3およびTFT素子2における特性をそれぞれ、高い値で両立させることができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いる薄膜トランジスタにおいて、安定した電気特性を有する信頼性のよい薄膜トランジスタを提供することを課題の一つとする。

【解決手段】酸化物半導体膜を用いる薄膜トランジスタのチャネル長が1.5μm以上100μm以下、好ましくは3μm以上10μm以下の範囲において、−25℃以上150℃以下の動作温度範囲で、チャネル幅が1μmあたりのオフ電流の値を1×10−12A以下とすることで、安定した電気特性を有する半導体装置を作製することができる。特に半導体装置の一態様である表示装置において、オフ電流の変動に起因する消費電力を低減することができる。

(もっと読む)

結晶化シリコン層の製造方法、半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置

【課題】金属原子が内部に拡散、侵入せず、かつ、結晶化方位や粒径を制御することのできる結晶化シリコン層の製造方法、かかる方法を利用した半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置を提供すること。

【解決手段】結晶化シリコン層を形成するにあたって、基板本体10d上に金属触媒層8および第1非結晶シリコン層4xを形成した後、熱処理を行ない、第1非結晶シリコン層4xと金属触媒層8との間での相互拡散により、第1非結晶シリコン層4xと金属触媒層8とを入れ替える。その際、第1非結晶シリコン層4xは、多結晶シリコン層4yに変化する。金属触媒層8を除去した後、開口部15aを備えた絶縁層15、および第2非結晶シリコン層1xを形成した状態で熱処理を行ない、第2非結晶シリコン層1xを、開口部15aの底部で多結晶シリコン層4yと接している部分を起点にして結晶化させる。

(もっと読む)

半導体装置の製造方法

【課題】短時間且つ低温で高品質な多結晶シリコンを形成する方法を提供する。

【解決手段】微結晶11aを含むアモルファス半導体膜11にマイクロ波を用いたアニールを行うことで、微結晶11aを核として微結晶11aを含むアモルファス半導体膜11を結晶化する。

(もっと読む)

非晶質半導体膜の結晶化方法、薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法

【課題】特性の優れた半導体膜を簡便に得ることができる微結晶半導体膜の結晶化方法と、これを応用した薄膜トランジスタ、半導体装置、及び薄膜トランジスタの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、基板1上に形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3を介してゲート電極2の対面に形成され、ソース領域となる第1非晶質領域41、ドレイン領域となる第2非晶質領域42、及び第1非晶質領域41と第2非晶質領域42との間に配置されたチャネル領域となる結晶性領域43を有する半導体膜4と、半導体膜4上に結晶性領域43と直接接触することなく形成され、ソース領域及びドレイン領域とそれぞれ電気的に接続されたソース電極81及びドレイン電極82と、を備えるものである。

(もっと読む)

多結晶シリコン層の製造方法、薄膜トランジスタ、それを含む有機電界発光表示装置及びその製造方法

【課題】多結晶シリコン層の製造方法、薄膜トランジスタ、それを含む有機電界発光表示装置及びその製造方法を提供する。

【解決手段】本発明は、基板100を提供する工程と、上記基板100上にバッファ層110を形成する工程と、上記バッファ層110上に金属触媒層115を形成する工程と、上記金属触媒層115の金属触媒をバッファ層110に拡散する工程と、上記金属触媒層115を除去する工程と、上記バッファ層110上に非晶質シリコン層120Aを形成する工程と、上記基板100を熱処理して上記非晶質シリコン層120Aを多結晶シリコン層に結晶化する工程とを含むことを特徴とする多結晶シリコン層の製造方法に関する。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】金属箔から成る支持層、支持層の上に形成された半導体構造部、および半導体構造部の上に形成された樹脂フィルムを有して成るフレキシブル半導体装置。かかるフレキシブル半導体装置では、樹脂フィルムには開口部が形成されており、その開口部に半導体構造部の表面と接触する導電部材が形成されており、半導体構造部が半導体層および半導体層の表面に形成された絶縁層を有して成る。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】トランジスタを有する半導体装置であって、絶縁表面上に所定の間隔を隔てて互いに平行に配列された複数の短冊状の半導体膜と、前記複数の短冊状の半導体膜の上面及び側面に接するゲート絶縁膜と、前記ゲート絶縁膜を介して前記複数の短冊状の半導体膜の上面及び側面を覆うゲート電極を有する半導体装置である。半導体膜の上部及び側部をチャネル形成領域とすることで、電流駆動能力を向上させることができる。

(もっと読む)

薄膜トランジスターの製造方法

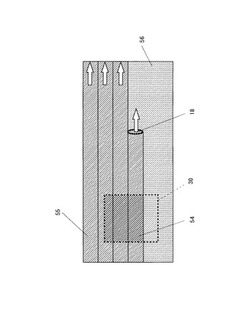

【課題】エキシマレーザーにより、α−Si層に加えられた熱は、絶縁層を介して金属遮光層へ伝わり、冷却されることで再結晶化される。この場合、金属層のパターン形状により、α−Si層の冷却速度は影響を受ける。そのため、多結晶シリコン層の特性は金属層のパターン形状の影響によりばらつくという課題がある。

【解決手段】形状および間隔を揃えた矩形の金属遮光層105の、長手方向に向けてエキシマレーザーを走査し、α−Si層を多結晶シリコン層115に改質する。長手方向に向けてエキシマレーザーを走査することから、金属遮光層105が連続した状態でレーザーアニールが進む。そのため、金属遮光層105上での多結晶シリコン層115は均質性が高くなる。そのため、金属遮光層105上に形成されるTFT101の電気的特性が均質化し、液晶装置100の表示均一性を高めることが可能となる。

(もっと読む)

半導体基板およびその製造方法、並びに半導体装置

【課題】段差部において膜厚の急激な変動が抑制された半導体膜を含む半導体基板、およびその製造方法、並びに、その半導体基板を備える半導体装置を提供する。

【解決手段】本発明に係る半導体基板1は、下地基板10と、下地基板10上の一部に形成されている金属膜20と、金属膜20を覆うようにして下地基板10上に形成されている絶縁膜30と、絶縁膜30上に形成され、かつ結晶化された半導体膜40とを備えている。絶縁膜30は、金属膜20の端部において段差部を有し、当該段差部の下地基板10に対して垂直な断面形状が、外に膨らむ「R」形状を呈している。上記段差面は、その上端部から下端部に向かって、テーパー角度ψが略0°から徐々に大きくなって、略40°〜90°であるテーパー角度θになるように形成されている。

(もっと読む)

半導体装置の作製方法

【課題】大面積な半導体装置を低コストに提供することを目的の一とする。または、nチャネル型トランジスタ及びpチャネル型トランジスタに最適な結晶面をチャネル形成領域とすることにより、性能向上を図ることを目的の一とする。

【解決手段】絶縁表面上に(211)面から±10°以内の面を上面とする島状の単結晶半導体層を形成し、単結晶半導体層の上面及び側面に接して形成し、且つ絶縁表面上に非単結晶半導体層を形成し、非単結晶半導体層にレーザー光を照射して非単結晶半導体層を溶融し、且つ、単結晶半導体層を種結晶として絶縁表面上に形成された非単結晶半導体層を結晶化して結晶性半導体層を形成し、結晶性半導体層を用いて、nチャネル型トランジスタ及びpチャネル型トランジスタを形成する。

(もっと読む)

半導体素子の製造方法及び電気光学装置の製造方法

【課題】例えば、高い膜質を有する多結晶シリコン層を活性層とする薄膜トランジスタを製造する。

【解決手段】第1膜(211)の上面(211t)と、上面(211t)に交差する第1膜(211)の側面(211s)とによって構成された角部(212)をなくすように、第1膜(211)にスライスエッチング処理を施し、第1膜(211)から第2膜(220)を形成する。即ち、第2膜(220)の角部(222)の断面形状は、第1膜(211)の角部(212)に比べて、角が取れているように、或いは曲線で構成されるように形成されている。尚、スライスエッチング処理とは、第1膜(211)上から第1膜(211)にエッチング液を接触させることによって、通常のウェットエッチング法及びドライエッチング法に比べて、緩やかに、言い換えれば、マイルドに第1膜(211)をエッチング処理することをいう。

(もっと読む)

半導体膜の形成方法および電気光学装置の製造方法

【課題】遮光層を有する構成でも、遮光層を有していない構成に対して液晶装置の製造工数や製造コストの上昇を抑えることができる半導体膜の形成方法および液晶装置の製造方法を提供すること。

【解決手段】半導体膜40の形成方法は、基板11上に、断面形状が台形状の遮光層21aを局所的に形成する遮光層形成工程と、遮光層21aを覆って、遮光層21aに重なる段差部22aを備えた絶縁層22を形成する絶縁層形成工程と、絶縁層22上に、段差部22aを覆う非晶質の半導体膜40を形成する半導体膜形成工程と、半導体膜40をアニールして結晶化させる結晶化工程と、を備え、遮光層形成工程では、遮光層21aにおける上底側の角部C1,C2が直角または鈍角をなして角張るように形成し、絶縁層形成工程では、絶縁層22の段差部22aにおける表面が角部C1,C2の形状に沿った形状となるように形成することを特徴とする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】結晶粒界が大きく電気的特性の向上したTFTを、コスト上昇を抑制しつつ形成する。

【解決手段】平坦な表面を有する基板10の該表面上に、高熱伝導性を有する材料からなる熱伝導層37を形成する第1の工程と、熱伝導層37を、熱伝導層37の少なくとも一部が表面に対して傾斜する傾斜部38となるようにパターニングする第2の工程と、少なくとも傾斜部38を覆うように、基板10上に非晶質シリコン層32を形成する第3の工程と、非晶質シリコン層32をレーザーアニールにより結晶化して多結晶シリコン層34を形成する第4の工程と、多結晶シリコン層34上に、平面視で傾斜部38と少なくとも一部が重なるようにゲート電極42を形成する第5の工程と、を有することを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

結晶シリコン膜の製造方法

【課題】 良質な単結晶シリコン膜を製造する。

【解決手段】 (a)単結晶シリコン基板表面の一部に、長さ方向に長く、幅方向に短い凹部を形成する。(b)凹部に、シリコン基板より熱伝導係数の小さい絶縁性の膜を埋め込む。(c)工程(b)で埋め込まれた絶縁性の膜の長さ方向と平行な方向に長く、長さ方向に平行な一方の縁が絶縁性の膜上にあり、長さ方向に平行な他方の縁がシリコン基板表面が露出した領域上にあるシリコン膜を形成する。(d)シリコン膜にレーザビームを照射して、シリコン基板に接触している部分から絶縁性の膜上の部分に向かって結晶成長させることにより、シリコン膜を結晶化する。

(もっと読む)

半導体装置およびその製造方法

【課題】微結晶半導体膜下部に微結晶を形成可能な半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、(a)ガラス基板10上にゲート電極20を形成する工程と、(b)ガラス基板10上およびゲート電極20上にゲート絶縁膜30を形成する工程と、(c)ゲート絶縁膜30上に非晶質シリコン膜40を成膜する工程とを備える。そして、(d)非晶質シリコン膜40にパルスレーザ光50を照射し、当該非晶質シリコン膜40を結晶化した微結晶シリコン膜41を形成する工程と、(e)ゲート電極20上側の微結晶半導体膜41以外の微結晶半導体膜41を除去する工程とを備える。そして、(f)工程(e)の後、ゲート電極20上側の微結晶半導体膜41と電気的に接続するソース電極71,ドレイン電極72を形成する工程を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 SOI構造の埋め込み絶縁膜の開口部における基板シリコンのダメージを防止すると共に、埋め込み絶縁膜の開口部における基板との接触面積の低下を防止する。

【解決手段】 SOI構造を有する半導体装置において、シリコン基板10と、シリコン基板10上に設けられ、一部に開口部12を有し、該開口部12の上部を上面側が広がった順テーパー構造に形成し、且つ下部を下面側が広がった逆テーパー構造に形成した絶縁膜11と、絶縁膜11上及び開口部12内に形成された単結晶シリコン層14と、単結晶シリコン層14に形成された半導体素子とを備えた。

(もっと読む)

1 - 20 / 75

[ Back to top ]