Fターム[5F152LN08]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706) | 歪を積極的に利用するもの (168) | 移動度の向上等 (128)

Fターム[5F152LN08]に分類される特許

1 - 20 / 128

半導体装置

【課題】高周波数動作が可能な半導体装置を提供すること。

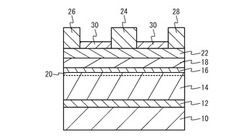

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

半導体装置

【課題】転位ループが発生するおそれがあるダミーパターン領域を有しながらも、転位ループによる基板上の他の素子等への悪影響が抑えられた半導体装置を提供する。

【解決手段】一実施の形態による半導体装置は、基板上に形成された素子分離絶縁膜と、前記素子分離絶縁膜により前記基板上に区画された素子領域およびダミーパターン領域と、前記素子領域内の前記基板上に形成された第1のエピタキシャル結晶層と、前記ダミーパターン領域内の前記基板上に形成された第2のエピタキシャル結晶層と、を有する。第1のエピタキシャル結晶層は前記基板を構成する結晶と異なる格子定数を有する結晶からなる。第2のエピタキシャル結晶層は前記第1のエピタキシャル結晶層と同じ結晶からなる。前記第2のエピタキシャル結晶層と前記基板との界面上の任意の点を含む前記基板の(111)面は、前記第2のエピタキシャル結晶層よりも深い領域で前記素子分離絶縁膜に囲まれる。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】単一のシリコン基板上に種類の異なる半導体結晶層をエピタキシャル成長させる場合に、表面の平坦性を向上し、半導体デバイスの信頼性を高める。

【解決手段】第1窪みおよび第2窪みが形成されたシリコン結晶を表面に有するベース基板と、第1窪みの内部に形成され、露出されている第1のIVB族半導体結晶と、第2窪みの内部に形成された第2のIVB族半導体結晶と、第2窪みの内部の第2のIVB族半導体結晶上に形成され、露出されているIII−V族化合物半導体結晶とを備える半導体基板を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

半導体装置

【課題】チャネル領域に歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】第一半導体からなる半導体基板1と、半導体基板1上に形成されたゲート絶縁膜2と、ゲート絶縁膜2上に形成されたゲート電極3と、ゲート絶縁膜2を介したゲート電極3下のチャネル領域4と、チャネル領域4に隣接する不純物原子が注入されたソース/ドレイン拡散層領域5,6と、を有し、ソース/ドレイン拡散層領域5,6に第一半導体と格子定数の異なる第二半導体の結晶からなる一軸歪み誘発層7を含み、一軸歪み誘発層7の底部と半導体基板1との界面で格子不整合が起こっており、一軸歪み誘発層7を形成した際に生じる半導体基板1との格子整合に起因する歪みが緩和している。

(もっと読む)

半導体装置およびその製造方法

【課題】大きな歪み量を発生可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、CとCの濃度の10倍以上のGeとを含んだSiGeC層を形成する工程(S3)と、SiGeC層内のCのうちで格子置換位置に位置しているものを格子間位置へと移動させることによって、前記SiGeC層内の全てのCに対する格子置換位置に位置するCの割合を形成された時点での割合から低下させて50%以下に低下させる工程(S4)と、を含む。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

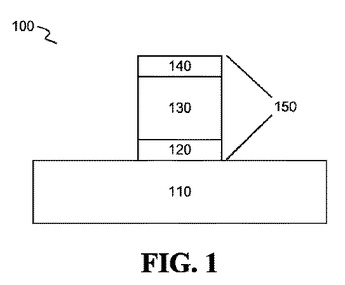

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高集積、高速且つ高性能な歪みSOI構造の縦型MISFETを得ること。

【解決手段】Si基板1上に酸化膜2を介して、横方向エピタキシャルSiGe層3が設けられ、SiGe層3は素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。SiGe層3上には選択的に縦方向エピタキシャルSiGe層7が設けられ、SiGe層7の側面には格子定数がやや小さい横方向エピタキシャル歪みSi層8が周設され、歪みSOI基板を形成しており、SiGe層7及び歪みSi層8の上部にはドレイン領域(10、11)が設けられ、SiGe層3全体、SiGe層7及び歪みSi層8の下部にはソース領域9が設けられ、歪みSi層8の側面にはゲート酸化膜12を介してゲート電極13が周設され、ドレイン領域11、ソース領域9及びゲート電極13には、それぞれ導電プラグ20を介してCu配線23が接続されている歪みSOI構造の縦型のMISFETを構成すること。

(もっと読む)

半導体装置およびその製造方法

【課題】Nチャネル絶縁ゲート型電界効果トランジスタのシリコンのチャネル領域に引張応力を効果的に印加することを可能とし、また寄生トランジスタの移動度を高めることを可能にする。

【解決手段】シリコン基板11と、前記シリコン基板11に区画された素子形成部12と、前記素子形成部12に形成されたNチャネル絶縁ゲート型電界効果トランジスタ20と、前記シリコン基板11に形成されていて前記素子形成部12の側部を囲む溝部13と、前記溝部13内に絶縁材料が埋め込まれて形成された素子分離部14と、少なくとも前記Nチャネル絶縁ゲート型電界効果トランジスタ20のチャネル長L方向と平行な前記溝部13の側面に形成されたシリコンゲルマニウムエピタキシャル成長層15を有する。

(もっと読む)

成膜方法

【課題】基板の主表面上に、基板の主表面を構成する材料の格子定数とは格子定数の異なる材料からなる薄膜を成膜することによりヘテロエピタキシャル膜を成膜させる際に、膜の界面付近において組成が急峻に変化していない遷移層が出現する。この遷移層が、ヘテロエピタキシャル膜の界面付近における結晶の特性を劣化させる。

【解決手段】成膜させたい薄膜を構成する材料の格子定数と、薄膜が成膜される基板の一方の主表面を構成する材料の格子定数とに応じて、主表面に沿った方向に対して基板を湾曲させる。そして、基板を湾曲させた状態で、その基板の一方の主表面上に薄膜を成膜させる。

(もっと読む)

半導体装置およびその製造方法

【課題】

歪み技術を用いたMOSトランジスタにおいて、リーク電流を抑える。

【解決手段】

半導体装置は、第1の格子定数を有する第1の半導体で形成された半導体基板に形成され、活性領域を画定する素子分離領域と、活性領域の中間位置を横断して、半導体基板上方にゲート絶縁膜を介して形成されたゲート電極と、ゲート電極側壁上に形成されたサイドウォールスペーサとを含むゲート電極構造と、ゲート電極構造両側の活性領域と素子分離領域との界面が半導体基板の表面に表出した境界の一部を覆って半導体基板の表面上方に配置された他のゲート電極構造であって、他のゲート電極と該他のゲート電極の側壁上に形成された他のサイドウォールスペーサとを含む他のゲート電極構造と、ゲート電極構造と他のゲート電極構造の間の活性領域をエッチして形成されたリセスと、リセスを埋めてエピタキシャル成長され、第1の格子定数と異なる第2の格子定数を有する第2の半導体で形成された半導体層と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETのゲート絶縁膜が薄膜化しゲート構造が複雑化した場合においても、動作速度に優れ、高信頼性を安定して確保できるMOSFETを実現する。

【解決手段】半導体装置の製造方法は、半導体基板3に、nチャネル型電界効果トランジスタ及びpチャネル型電界効果トランジスタを形成する工程(a)と、nチャネル型電界効果トランジスタ上及びpチャネル型電界効果トランジスタ上を覆うように応力膜11を形成する工程(b)と、応力膜11上に、pチャネル型電界効果トランジスタの上方を覆い且つnチャネル型電界効果トランジスタの上方に開口を有する遮光膜12を形成する工程(c)と、工程(c)の後に、半導体基板3上の全面に紫外線を照射する工程(d)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、効果的な高速動作が可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明の一実施形態による半導体装置は、n型Si基板2に埋め込まれ、チャネルを挟んで離間して形成されたソースおよびドレインと、チャネル上に形成されたゲートとを備え、ソースおよびドレインは、SiC3と、SiC3の全面上に形成され、チャネルに応力を与えることが可能な半導体材料よりなるp型SiGeとの積層からなることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

多層膜構造体およびその形成方法

【課題】半導体素子用の多層膜構造体を基板上に形成する多層膜構造体であって、大きな伸張歪を半導体層に印加できる多層膜構造体の形成方法を提供する。

【解決手段】半導体素子用の多層膜構造体10を基板上に形成する際に、基板11上に、当該基板11を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、圧縮歪を有する圧縮歪半導体層12を形成する。その圧縮歪半導体層12の上方に、圧縮歪半導体層12を構成する結晶の格子定数よりも大きな格子定数の結晶からなるとともに、無歪の無歪半導体層13を積層する。圧縮歪半導体層12の圧縮歪を緩和させることにより、無歪半導体層13に伸張歪を印加する。それにより、大きな伸張歪を無歪半導体層13に印加することができる。

(もっと読む)

1 - 20 / 128

[ Back to top ]