Fターム[5F152MM04]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 電子素子 (1,201) | トランジスタ (962) | MOSFET (619)

Fターム[5F152MM04]に分類される特許

601 - 619 / 619

シリコンゲルマニウムを用いる半導体構造の製造方法

シリコン層(24,26,28)を有する半導体基板を提供する。一実施形態では、基板はシリコン層(24,26,28)の下に位置する酸化物層(14)を有するシリコン・オン・インシュレータ(SOI)基板(12,14,24,26,28)である。シリコン層(24,26,28)の上に非晶質または多結晶のシリコンゲルマニウム層(32)を形成する。これに代えて、シリコン層(24,26,28)の上部へゲルマニウムを注入して、非晶質シリコンゲルマニウム層(32)を形成する。次に、シリコンゲルマニウム層(32)を酸化して、シリコンゲルマニウム層をシリコンジオキサイド層(34)に変換し、かつシリコン層(24,26,28)の少なくとも一部をゲルマニウムリッチシリコン(36,38)に変換する。次に、ゲルマニウムリッチシリコン(36,38)を用いるトランジスタ(48,50,52)の形成に先立って、シリコンジオキサイド層(34)を除去する。一実施形態では、シリコン層(28)の上、かつ、シリコンゲルマニウム層(32)の下のパターン形成されたマスキング層(30)を用いて、ゲルマニウムリッチシリコン(36,38)を選択的に形成する。これに代えて、分離領域を用いて、ゲルマニウムリッチシリコンが形成される基板の局所的領域を画定する。  (もっと読む)

(もっと読む)

SOI(semiconductoroninsulator)基板、およびこの基板から形成されるデバイス

レアアース・スカンデートのようなペロブスカイト格子構造を有する絶縁材料の層を含むSOI(semiconductor on insulator)デバイスである。この絶縁材料(52)は、この絶縁材料(52)のすぐ上にダイヤモンド格子を有する半導体材料(54)を成長させることができる、有効な格子定数を有するように選択される。レアアース・スカンデート絶縁体の例としては、ガドリニウム・スカンデート(GdScO3)、ジスプロシウム・スカンデート(DyScO3)、およびガドリニウムとジスプロシウム・スカンデートの合金(Gd1-xDyXScO3)が含まれる。  (もっと読む)

(もっと読む)

歪みシリコンオンインシュレータ構造を製造する方法およびそれによって形成された歪みシリコンオンインシュレータ構造

【課題】シリコンの活性層を基板から分離する埋め込み絶縁層の活性層の下にある領域の厚さを増加させることによって形成されるシリコン活性層の局所的に歪んだ領域を有するシリコンオンインシュレータ(SOI)デバイスおよび構造を提供する。

【解決手段】絶縁層の活性層の下にある肥厚領域からその上にある歪んだ領域へと伝達される応力が、活性層の閉じ込められた領域において担体移動度を増加させる。シリコン活性層およびその上に形成されたデバイスは、隔置された歪んだ領域内の担体移動度の増加から恩恵を受けることができる。

(もっと読む)

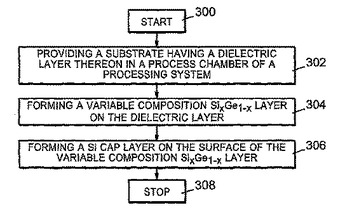

可変シリコン−ゲルマニウム組成を有するシリコンゲルマニウム薄層半導体構造および加工方法

誘電体層(410,510,610)、誘電体層(410,510,610)上の可変組成SixGe1-x層(440,520,620)、および可変組成SixGe1-x層(440,520,620)上のSiキャップ層(450,530,630)を持った基板(400,500,600)を含むSiGe薄層半導体構造である。可変組成SixGe1-x層(440,520,620)は、勾配を付けたGeを有するSixGe1-x層(520,620)、または、それぞれ異なったGe含有量(421,431)を有する複数のSixGe1-xサブ層(420,430)を含むことができる。本発明の一実施形態では、SiGe薄層半導体構造は、誘電体層(610)、誘電体層(610)上のSi含有シード層(615)、シード層(615)上の可変組成SixGe1-x層(620)、及び可変組成SixGe1-x層(620)上のSiキャップ層(630)を持つ半導体基板(600)を含む。SiGe薄層半導体構造を加工するための方法と処理ツール(1,100)も提供される。  (もっと読む)

(もっと読む)

高速CMOS共存Ge−オン−インシュレータ光検出器の構造および製作方法

【課題】SiCMOS技術と共存可能な高速高効率光検出器を作る問題に対処すること。

【解決手段】本構造は、薄いSOI基板の上のGe吸収層から成り、分離領域、交互になるn型およびp型コンタクト、および低抵抗表面電極を利用する。本デバイスは、下の基板で生成されたキャリアを分離するために埋込み絶縁物を利用して高帯域幅を、Ge吸収層を利用して広いスペクトルにわたった高量子効率を、薄い吸収層および狭い電極間隔を利用して低電圧動作を、さらに平面構造およびIV族吸収材料の使用によってCMOSデバイスとの共存性を、達成する。本光検出器を製作する方法は、薄いSOIまたはエピタキシャル酸化物へのGeの直接成長および高品質吸収層を達成するための後の熱アニールを使用する。この方法は、相互拡散に利用可能なSiの量を制限し、それによって、下のSiによるGe層の実質的な希釈を起こすことなく、Ge層をアニールすることができるようになる。

(もっと読む)

シャロウトレンチ分離プロセスおよび構造

集積回路(IC)を製造する方法は、シャロウトレンチ分離(STI)技術を利用する。シャロウトレンチ分離技術は歪みシリコン(SMOS)プロセス中において使用される。トレンチ(34)を形成した後、歪み材料(36)を形成する。このプロセスは、埋込酸化膜(BOX)層(14)上の化合物半導体層16上で利用される。  (もっと読む)

(もっと読む)

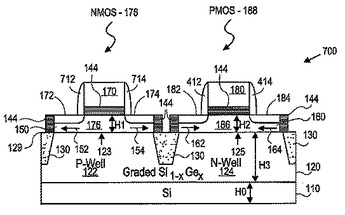

CMOS用歪トランジスタの集積化

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

MIS型電界効果トランジスタ

下地SiGe層1上に歪みSi層2をエピタキシャル成長させ、ゲート絶縁膜3aとゲート電極4aを形成した後、ゲート電極4aをマスクにして、下地SiGe層1及び歪みSi層2に不純物をイオン注入し(図2(a))、活性化のための熱処理を行ってソース・ドレイン領域6を形成する(図2(b)、(c))。このとき、歪みSi層2の膜厚は、最終的なMISFETのソース・ドレイン領域6の不純物濃度が最大となる深さをTp(=Rp)としたとき、2Tp以下にする。 (もっと読む)

MOSFET構造体内に歪みSiチャネルを形成する方法

基板(1)上に歪みSi層を形成する方法が、Si表面上のエピタキシャルSiGe層(4)の形成と、エピタキシャルSiGe層(4)の上部にSi層のエピタキシャル成長による歪みSi層の形成とを含み、Si層はエピタキシャル成長によって歪み状態にされ、基板(1)が、支持層(1)と、埋込み二酸化シリコン層(BOX)と、単結晶Si表面層(3)とを有するシリコン・オン・インシュレータ基板であり、その方法は、更に、Si表面層(3)をアモルファスSi層(3B)に、且つ、エピタキシャルSiGe層(4)の一部分をアモルファスSiGe層(5)に変換するためのSi表面層(3)とエピタキシャルSiGe層(4)のイオン注入であって、エピタキシャルSiGe層(4)の更なる部分が残存単結晶SiGe層(6)であるイオン注入を含み、アモルファスSi層(3B)と、アモルファスSiGe層と、残存単結晶SiGe層(6)とが、埋込み二酸化ケイ素層(BOX)に隣接しているアモルファスSi層(3B)と共に埋込み二酸化ケイ素層(BOX)上の積層(3B、5、6)を形成する。  (もっと読む)

(もっと読む)

Si:C−OIおよびSGOI上のシリコン・デバイスならびに製造方法

【課題】より費用効果が高くより簡略な、大きな引張り応力および圧縮応力をそれぞれnFETおよびpFETのチャネル中で生成する方法を提供すること。半導体構造および製造方法を提供すること。

【解決手段】この製造方法は、基板中に浅いトレンチ分離(STI)(25)を形成するステップと、基板上に第1の材料(30)および第2の材料(40)を設けるステップとを含む。第1の材料(30)および第2の材料(40)は、熱アニール・プロセスによって基板中に混合され、それぞれnFET領域の第1のアイランド(50)、およびpFET領域の第2のアイランド(55)を形成する。第1のアイランド(50)および第2のアイランド(55)の上に、材料層を形成する。STIは、緩和して、第1のアイランド(50)および第2のアイランド(55)の緩和を促進する。第1の材料(30)は、堆積または成長させたGe材料とすることができ、第2の材料(40)は、堆積または成長させたSi:CまたはCとすることができる。第1のアイランド(50)および第2のアイランド(55)の少なくとも一方の上に、歪みSi層を形成する。

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

格子チューニング半導体基板の形成

Si表面(15)上において分離層(11)を貫通するウィンドウ(13)により、Si表面(15)の選択された領域(12)を画定するステップ、分離層(11)の一部によってSi表面(15)から分離されたくぼみ(14)を分離層(11)内に画定するステップ、Si表面(15)の選択された領域(12)の上にSiGe層(16)を成長させることにより、ウィンドウ(13)内に転位(17)を形成してSiGe層(16)内のひずみを開放するステップ、及び、分離層(11)を越えてくぼみ(14)内に延びるまでSiGe層(16)を更に成長させることにより、くぼみ(14)内にSiGeのほぼ転位のない領域(18)を形成するステップを含む格子チューニング半導体基板形成方法を提供する。必要に応じて、SiGe層(16)の、分離層(11)を越えて成長した部分を研磨によって除去し、くぼみ(14)内のSiGeのほぼ転位のない領域(18)をウィンドウ(13)内のSiGe領域から分離することができる。更に、SiGe層(16)及び分離層(11)をくぼみ(14)の近傍を除くSi表面(15)から除去し、分離層(11)部分によってSi表面(15)から分離されたSiGeのほぼ転位のない領域(18)をSi表面(15)上に残すことができる。  (もっと読む)

(もっと読む)

極薄SOI/SGOI基板上の超高速SI/SIGE変調ドープ電界効果トランジスタ

【課題】 MODFETデバイス構造体の製作における横及び垂直方向の縮小に伴う困難を克服するMODFETデバイス構造体の縮小技術を提供する。

【解決手段】 シリコン及びシリコンゲルマニウム・ベースの半導体MODFETトランジスタ・デバイスの設計と製造方法が示される。MODFETの設計は、RF、マイクロ波、サブミリ波及びミリ波を含むさまざまな通信用途のための、超高速、低ノイズの性能を持った、成長型エピタキシャル電界効果トランジスタ構造を有する。エピタキシャル電界効果トランジスタ構造は、大幅に改善されたRF性能の達成を可能にする、極薄SOI又はSGOI基板上に最適な変調ドープ・ヘテロ構造を形成するシリコン及びシリコンゲルマニウム層を組込んだ高移動度ひずみn−チャネル及びp−チャネル・トランジスタのための、極限的な(垂直及び横方向の)デバイス小型化及び層構造設計を含む。

(もっと読む)

テンプレート層構成

ひずみ半導体層を形成するためのプロセス。かかるプロセスは、ウェハを加熱しながら、当該ウェハの上にわたって塩素ベアリングガス(例えば、塩化水素、塩素、四塩化炭層、及び、トリクロロエタン)を流すことを含む。ある実施例では、ひずみ半導体層(例えば、ひずみシリコン)を形成するためのテンプレート層として使用される半導体層に圧縮プロセスをする間、塩素ベアリングガスが流される。他の実施例では、圧縮操作の後、前記ウェハのポストベーク中、塩素ベアリングガスが流される。

(もっと読む)

(もっと読む)

絶縁構造部上の半導体チャンネル

半導体装置基板上に貫通誘電体層を形成するステップと、貫通誘電体層の上部にトレンチ誘電体層を形成するステップと、貫通誘電体層を露出させるため、トレンチ誘電体層を貫通する溝を形成するステップと、基板を露出させるため、前記溝内の貫通誘電体層に貫通孔を形成するステップと、溝内および前記貫通孔内に半導体材料を形成するステップと、を有する方法を示した。装置基板と、該装置基板の表面に形成された誘電体層と、誘電体層上に形成された、装置基板と相間する結晶構造を有する装置基部と、を有する装置を示した。  (もっと読む)

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

実質的に緩和されたSiGeオン・インシュレータ基板材料およびそれを製作する方法(合金融点付近でのアニーリングによる高品質SGOI)

【課題】 低欠陥で実質的に緩和されたSiGeオン・インシュレータ基板材料を形成する方法を提供することにある。

【解決手段】 この方法は、Ge拡散に対する抵抗力のあるバリア層の上に存在する第1の単結晶Si層の表面上にGe含有層をまず形成するステップを含む。次に、加熱ステップは、最終的なSiGe合金の融点に近く、Geを保持しながら積層欠陥の形成を遅らせる温度で実行される。加熱ステップは、第1の単結晶Si層およびGe含有層全体にわたってGeの相互拡散を可能にし、それによりバリア層の上に実質的に緩和された単結晶SiGe層を形成する。その上、加熱ステップは最終的なSiGe合金の融点に近い温度で実行されるので、緩和の結果として単結晶SiGe層内に存続する欠陥はそこから効率よく消滅される。一実施形態では、加熱ステップは、2時間未満の期間の間、約1230〜約1320℃の温度で実行される酸化プロセスを含む。この実施形態は、最小表面ピッチングおよび低減されたクロスハッチングを有するSGOI基板を提供する。

(もっと読む)

選択されたパラメータを有するSiGeオン・インシュレータ(SGOI)基板を製作する方法(酸化、薄型化、およびエピタキシャル再成長の組み合わせを使用するSiGe格子工学)

【課題】 SiGe厚さとGe比とひずみ緩和との相互依存を切り離すために格子工学が使用される、SiGeオン・インシュレータ(SGOI)基板を製作する方法を提供することにある。

【解決手段】 この方法は、選択された平面内格子定数と、選択された厚さパラメータと、選択されたGe含有量パラメータとを有するSiGe合金層を有するSiGeオン・インシュレータ(SGOI)基板材料を提供するステップであって、選択された平面内格子定数が一定値を有し、他のパラメータ、すなわち、厚さまたはGe含有量の一方または両方が調整可能な値を有するステップと、選択された平面内格子定数を維持しながら、他のパラメータの一方または両方を最終選択値に調整するステップとを含む。この調整は、どのパラメータが固定され、どのパラメータが調整可能であるかに応じて、薄型化プロセスまたは熱希釈プロセスのいずれかを使用して達成される。

(もっと読む)

歪みシリコン・オン・インシュレータ(SSOI)およびこれを形成する方法

【課題】 コストが低く歩留まりの高い、引っ張り歪みSOI層を形成するための方法および引っ張り歪みSOI層の構造を提供する。

【解決手段】 歪みSiベースの層を製造するための方法、この層に製造されるデバイス、ならびに、かかる層およびデバイスを含む電子システムを開示する。この方法は、基板上にSiGe層をエピタキシャル成長させるステップと、このSiGe層において様々なGe濃度を生成するステップを含む。SiGe層内のGe濃度は、Ge濃度が突然かつ著しく増大する固有のGeオーバーシュート・ゾーンを含む。SiGe層上に、Siベースの層をエピタキシャル堆積させ、これによって引っ張り歪みが与えられる。また、典型的にSiまたはSiGeである歪みSiベースの層を、異なるバルク基板または絶縁体に転写可能であることも開示される。

(もっと読む)

601 - 619 / 619

[ Back to top ]