Fターム[5H420NB33]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 複数出力 (42) | 多出力カレントミラー回路を用いるもの (26)

Fターム[5H420NB33]に分類される特許

1 - 20 / 26

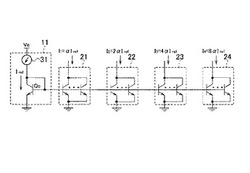

定電流回路の出力設定装置

【課題】電流値の設定が容易であり、且つ、装置構成を簡素化することが可能な定電流回路の出力設定装置を提供する。

【解決手段】基準電流Irefを流す基準電流発生回路11と、基準電流Irefに比例した電流を流すカレントミラー回路を少なくとも一つ備えた、4個のカレントミラー回路群、即ち、第1〜第4のカレントミラー回路群21〜24を備える。そして、各カレントミラー回路群21〜24は、それぞれ、基準電流Irefに対してα倍、2α倍、4α倍、8α倍となる電流を出力する。そして、各カレントミラー回路群を適宜選択して負荷に接続することにより、該負荷に供給する電流値が所望の電流値となるように設定することが可能となる。このため、操作性を容易とし、且つ、装置構成を簡素化することが可能となる。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

基準電流発生回路

【課題】正の2次温度係数を有する基準電流を生成する基準電流発生回路を提供する。

【解決手段】第1基準電流発生回路11は、第1電流電圧変換回路14と、第2電流電圧変換回路15と、第1および第2電流電圧変換回路14、15に等しい電流を供給する第1電流供給回路16とを備え、負の2次温度係数a12を有する第1基準電流I1を発生する。第2基準電流発生回路12は、第3電流電圧変換回路24と、第4電流電圧変換回路25と、第5電流電圧変換回路26と、第4電流電圧変換回路25に供給する電流に等しい電流を第3および第5電流電圧変換回路24、26に一定の比率で分流して供給する第2電流供給回路27とを備え、絶対値が負の2次温度係数a12と略等しい正の2次温度係数a22を有する第2基準電流I2を発生する。電流出力回路13は、第1基準電流I1と第2基準電流I2を加算した第3基準電流I3を出力する。

(もっと読む)

基準電流生成回路

【課題】PN接合ダイオードを必要とせず、回路電流の温度依存性が概略零となる基準電流生成回路を提供する。

【解決手段】基準電流生成回路は、第1カレントミラー回路と、第2カレントミラー回路とを具備する。第1カレントミラー回路は、入力側トランジスタである第1チャネルの第1トランジスタと、第1トランジスタのゲートに制御電圧を印加する第1抵抗とを備える。第2カレントミラー回路は、入力側トランジスタである前記第1チャネルと相補の第2チャネルの第2トランジスタを備える。第1カレントミラー回路の出力ノードは、第2カレントミラー回路の入力ノードに接続され、第1カレントミラー回路の入力ノードは、第2カレントミラー回路の出力ノードに接続される。基準電流生成回路は、第1トランジスタのゲートに印加される制御電圧を第1出力とし、第2トランジスタのゲートに印加される制御電圧を第2出力とする。

(もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

ディレイ発生回路、定電流源回路

【課題】トランジスタのしきい値と電流量のみに依存するディレイ発生回路、ディレイ発生回路を使った定電流源を提供する。

【解決手段】制御電圧をゲート端子から入力し、基準電流を発生するPMOSトランジスタ(PMOSTr)104a、PMOSTr104のドレインにかかる電圧を保持するPMOSTr105h及びオペアンプ106、PMOSTr104aに基準電流と同じ電流Isを供給するPMOSTr105a、PMOSTr105aに流れる電流の比例電流を各々が発生する複数のPMOSTr105b〜105g、PMOSTr105b〜105gとオープンドレイン接続されるNMOSTr104b〜104gを設け、NMOSTr104b〜104gを多段に接続し、NMOSTr104bのゲート端子にはクロック信号を入力させ、2以上の偶数番目のNトランジスタのドレインから遅延信号を出力させる。

(もっと読む)

定電圧発生回路およびA/D変換回路

【課題】定電圧発生回路に対して供給される電源電圧に変動があった場合でも、所定の差分を有する電圧を精度よく発生させる定電圧発生回路、および、その定電圧発生回路を備えたA/D変換回路を提供する。

【解決手段】第1入力端子11、第2入力端子12、第1出力端子21、第2出力端子22および入力コモン端子13を備えた全差動型OPアンプ50と、電源VDDとグランドとの間に直列接続された抵抗R2、抵抗R3および定電流源10と、電源VDDとグランドとの間に直列接続された抵抗R1,R1とを備える。抵抗R2の両端子は、第1入力端子11および第2入力端子12にそれぞれ接続され、抵抗R1,R1の接続点は、入力コモン端子13に接続されている。

(もっと読む)

定電流回路検査装置、集積回路および定電流回路検査方法

【課題】カレントミラー回路の検査を容易かつ確実に素早く行う。

【解決手段】出力された基準電流I1を複製して定電流I7、I8を出力するカレントミラー回路3を備えた定電流回路3を検査する定電流回路検査装置であって、定電流I3を複製して検査用定電流I7、I8を出力する電流複製部Q17、Q18と、基準電流I2の電流値と異なる電流値を有する電流である比較電流I50、I51を流す検査用カレントミラー回路4と、比較電流I7、I8に基づく各電圧を検出し、その各電圧を利用して定電流回路3の良不良を判定する判定回路5とを有する。

(もっと読む)

電流感知回路ループのある定電流調整器

【課題】特に定電流を負荷装置に供給するための電流感知回路ループのある定電流調整器を提供する。

【解決手段】

定電流調整器3には、スイッチ装置SWを通って流れる電流を検出し、スイッチ装置SWを通って流れる電流に比例する検出電流Isを発生させるために、定電流調整器のスイッチ装置SWに接続される電流感知回路ループ30が含まれる。検出電流Isは、検出電圧Vsを誘導するために検出抵抗器Rsを通って流れる。差動増幅器36は、パルス幅変調制御器32に誤差電圧Veを発生させるために、既定電圧Vsetおよび受信検出電圧に基づき、同様に、ゲート駆動回路31にそのスイッチ装置SWの調整器の出力電圧に接続される負荷装置に定電流を供給するスイッチング操作を制御させる。

(もっと読む)

基準電圧発生回路のための起動回路

【課題】初期に充分な起動電流が流れることで、迅速にBGR回路を起動できるとともに、BGR回路自身による起動が可能な時点からは、それ自体の動作電流を減少できる基準電圧発生回路のための起動回路を提供する。

【解決手段】一定のレベルを有する基準電圧を発生する基準電圧発生回路を起動する起動回路において、起動開始信号に応答して、起動初期に前記基準電圧発生回路に電流を流して起動を開始する起動スタート部と、前記基準電圧発生回路の起動可否による変動電圧を減少させ、前記変動電圧に相応する起動基準電流を発生する基準電流発生部と、前記基準電圧発生回路に流れる電流を検出し、検出された結果を前記起動基準電流と比較し、比較された結果を前記起動開始信号として出力する起動制御部とを備えて基準電圧発生回路のための起動回路を構成する。

(もっと読む)

電流源装置、オシレータ装置およびパルス発生装置

【課題】停止時においては出力電流を遮断し、起動時においては所望の出力電流を直ちに得ることができる電流源装置を提供する。

【解決手段】第1FETとこれに直列接続された抵抗とからなり電源電圧が回路両端に印加されている第1直列回路と、第2FETとこれに直列接続された第3FETとからなり、第2FETと第3FETとの接続点と第3FETのゲートとが短絡され電源電圧が回路両端に印加されている第2直列回路と、第1および第2FETの双方のゲートに共通の駆動電圧を供給する駆動回路と、第2および第3FETのゲート電圧を第1および第2駆動電圧としてこれらに応じて動作する第1および第2電流源回路と、を含む電流源装置であり、第1および第2電流源FETが導通に至る際に第1および第2駆動電圧を強制的に変化せしめる起動回路を含み、第1および第2電流源FETのソース若しくはドレインから出力電流を供給する。

(もっと読む)

基準電圧発生回路

【課題】発生させる基準電圧の電圧レベルが高くなった場合でも、基準電圧を所定の許容範囲内に調整することができる基準電圧発生回路を提供する。

【解決手段】モード切替回路12より、発生させる基準電圧に応じて当該基準電圧の電圧レベルが高くなるほど電流値の大きな供給電流を供給し、調整回路14により、供給電流の通電経路における所定位置の電圧を基準電圧Vrefとして出力すると共に、当該通電経路の抵抗値を変更することにより出力される基準電圧の電圧レベルを調整しており、基準電流制御回路16により、発生させる基準電圧の電圧レベルが高い場合に通電経路に通電される供給電流の一部を分岐させる。

(もっと読む)

カレントミラー回路

【課題】電源電圧が1V程度から安定に動作する回路とする。

【解決手段】基準電流源Isをコレクタに接続したPNP型のマスタートランジスタQ1とダイオード接続したPNP型のミラートランジスタQ2とで構成される第1のカレントミラー回路と、第1のカレントミラー回路によって生じたミラー電流を基準電流として動作するNPN型のマスタートランジスタQ4と、複数のNPN型のミラートランジスタQ5〜Qn+3とで構成される第2のカレントミラー回路と、電源にエミッタを接続し、マスタートランジスタQ1のコレクタにベースを接続し、マスタートランジスタQ4および複数のミラートランジスタQ5〜Qn+3のそれぞれのベースにコレクタを接続するPNP型のベース電流補償用トランジスタQ3と、を備える。

(もっと読む)

チェーン−チョッピング電流ミラー及び出力電流安定化方法

【課題】電流ミラー回路の出力電流の同等性を向上する。

【解決手段】チェーン-チョッピング電流ミラー及び出力電流を安定化する方法を開示する。電流ミラーは多数の出力ノード、バイアス源ユニット、多数の電流ミラーリングユニット及び多数のスイッチ部品を具えている。バイアス源ユニットは受電した電流に応じて基準バイアスを供与する。電流ミラーリングユニットの各々は基準バイアスに応じて出力電流を出力する。各スイッチ部品の制御端子はクロック信号を受信して、そのクロック信号に従ってスイッチ部品の第1端子をその第2端子に結合させるのか、第3端子に結合させるのかどうかを決定し、i番目のスイッチ部品の第1端子はi番目の電流ミラーリングユニットの出力端子に結合され、その第2端子はi番目の出力ノードに結合され、その第3端子は(i+1)番目の出力ノードに結合されるようにし、ここに、iは自然数とする。

(もっと読む)

カレントミラー回路

本発明は、入力側のトランジスタ(Q1)又は電界効果トランジスタと、出力側のトランジスタ(Q2)又は電界効果トランジスタとを備えるカレントミラー回路(40,50,60)であって、前記入力側及び出力側の各トランジスタのエミッタ又はソースを結合するとともに電圧供給端(UB,55)に接続し、前記入力側及び出力側の各トランジスタのベース(45,46,57,58)又はゲートを互いに電気的に結合するとともに追加の電界効果トランジスタ(Q3)に接続し、前記追加の電界効果トランジスタ(Q3)のソース(44)を前記入力側及び出力側の2つのトランジスタ(Q1,Q2)又は電界効果トランジスタのベース(45,46,57,58)又はゲートに結合し、且つ前記追加の電界効果トランジスタ(Q3)のドレインを前記入力側のトランジスタ(Q1)又は電界効果トランジスタのコレクタ又はドレインに結合するようにした、カレントミラー回路に関する。  (もっと読む)

(もっと読む)

LED駆動回路

【課題】基準列の開放故障があってもすべてのLEDが消灯することなく、また無駄な電力消費をもたらす基準列をなくした。

【解決手段】LED列回路2とカレントミラー回路3とが、出力電圧可変電源1の出力端子に接続されるLED駆動回路において、基準列トランジスタ31T及びこれと接続されたLED列21における開放故障を検出する個別開放故障検出回路41と、この個別開放故障検出回路41による故障検出出力に応答してカレントミラー回路3の電流通路を切換える電流切換回路5と、を備えた。

(もっと読む)

カレントミラー回路および定電流回路

【課題】 トランジスタの共通のベースラインと電源線との間に抵抗が接続されている場合でも高精度のミラー比を得る。

【解決手段】 カレントミラー回路18において、抵抗R5はノイズ耐量を上げるとともにトランジスタQ10、Q11の漏れ電流を防止するために必要であり、トランジスタQ12のコレクタ電流は、抵抗R5に流れる電流が支配的となる。トランジスタQ12のベース電流IB(Q12)を、トランジスタQ14のベース電流IB(Q14)により補償する。抵抗R5に流れる電流とトランジスタQ11、Q13〜Q15に流れる電流とが等しい場合にほぼ完全に補償でき、ミラー比はより正確に1に近付く。

(もっと読む)

基準電圧発生装置

【課題】温度変化/電圧変動に依存性しない複数出力の基準電圧発生回路。

【解決手段】電源電圧変動/温度変化の影響を受け無いバイアス電圧発生回路と、チャンネル幅とチャンネル長の比が実質的に等しい2つのNMOS型トランジスタを直列に接続して構成した第1〜第H(Hは2以上の正の整数)の直列回路と、これらの直列回路に電流を供給する電流供給源とを備え、前記夫々の直流回路を構成するNMOS型トランジスタのゲートとドレインとを接続し、前記第1の直列回路の一方のNMOS型トランジスタのゲートに前記バイアス電圧発生回路の直流出力電圧を印加し、他方のNMOS型トランジスタの出力端子に前記直流出力電圧の2倍の直流出力電圧を発生させ、第H−1の直列回路の出力電圧を第Hの直列回路の相互接続点に印加し、他方のNMOS型トランジスタの出力端子に前記バイアス電圧発生回路の直流出力電圧に(H+1)倍の直流出力電圧を発生させる。

(もっと読む)

定電流駆動回路、それを用いた発光装置、電子機器

【課題】 並列に接続された複数の負荷回路に、均一な駆動電流を供給可能な定電流駆動回路を供給する。

【解決手段】 並列に接続された複数の負荷回路を定電流駆動する定電流駆動回路100において、基準電流源20は、基準電流Irefを生成する。定電流回路10は、負荷回路に直列に接続される。電流分配部(M10〜M15)は、基準電流Irefを複数の定電流回路10に分配する。定電流回路10は、基準電流Irefにもとづいて駆動電流Idrvを生成し電流出力端子102に接続される負荷回路を駆動する。オフセット電圧調節回路14は、演算増幅器12のオフセット電圧を調節することにより、各定電流回路10により生成される駆動電流Idrvを均一化する。

(もっと読む)

1 - 20 / 26

[ Back to top ]