Fターム[5H730FD26]の内容

DC−DCコンバータ (106,849) | 信号検出 (10,889) | その他の電圧の (663) | スイッチング素子の (202)

Fターム[5H730FD26]に分類される特許

1 - 20 / 202

半導体集積回路、および、DC−DCコンバータ

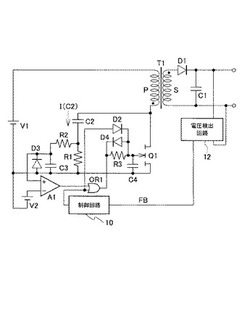

過電圧保護回路

【課題】製造し易い高耐圧素子を使用し、且つ、インピーダンスのバラツキを考慮しなくても良い過電圧保護回路。

【解決手段】制御信号によりスイッチング素子Q1を駆動する駆動部10と、スイッチング素子のドレインとソースとの間に接続され、コンデンサC2と抵抗R1とが直列に接続された微分回路と、抵抗R1の両端に接続され、抵抗R2とコンデンサC3とが直列に接続された積分回路と、コンデンサC3の電圧が基準電圧以上となった場合にドレイン及びソース間の電圧が所定電圧以上になったと判定し、スイッチング素子をオンさせてドレイン及びソース間の電圧をクランプさせる過電圧保護部A1,R3,C4とを備える。

(もっと読む)

チャージポンプ回路及びこれを用いた電源装置

【課題】容易にかつ適切にFETのオン/オフ制御を行う。

【解決手段】チャージポンプ回路1は、キャパシタC1の充放電用スイッチとして用いられるFET103(104)と、FET103(104)に流れる電流またはFET103(104)の両端電圧に応じて検出信号S11(S12)を生成する検出部109(110)と、検出信号S11(S12)に応じてFET103(104)の駆動信号G11(G12)を生成する駆動部107(108)と、を有する。

(もっと読む)

DC/DCコンバータ

【課題】軽負荷時において、同期整流スイッチに逆電流を流すことなく、簡素な構成で同期整流スイッチの切り替え動作を行うことが可能なDC‐DCコンバータを提供する。

【解決手段】軽負荷時に同期整流オフとする同期整流オフ選択回路11とスイッチQ1のオフ期間Toffを生成するToff期間生成部12を備え、軽負荷時のスイッチQ1とQ2との接続点電位をパルス成型回路13でパルス変換後カウンタ14でカウントし、時間差比較/不連続検出信号生成部15でToff期間中にカウンタ信号の発生を検出し、カウンタ信号があった場合は1パルス・ラッチ回路17を介して次のスイッチング周期は同期整流オフを継続させてスイッチQ2の同期整流をオフにするスイッチ制御部10aを備える。

(もっと読む)

過電流保護回路及びこれを用いたスイッチング電源装置

【課題】過電流保護値に適切な負の温度特性を持たせる。

【解決手段】過電流保護回路18は、抵抗値の異なる抵抗A1、A2を含む抵抗部Aと、抵抗A1、A2に現れる電圧V1、V2を比較して過電流保護信号S1を生成する比較部Bと、抵抗A1、A2にスイッチ素子12の降下電圧(SW−PGND)を印加する入力部Cと、電流値の等しい電流I1、I2を生成して抵抗A1、A2に供給する電流生成部Dとを有し、電流生成部Dは、抵抗A1、A2と同一の温度特性を有しており、温度特性のフラットな基準電圧BGから基準電流Ixを生成する抵抗D10と;スイッチ素子12と同一の温度特性を有しており、基準電流Ixから基準電圧Vxを生成する抵抗D7と;負の温度特性を有しており、基準電圧Vxから基準電流Iyを生成する抵抗D8と;基準電流Iyから電流I1、I2を生成するカレントミラー(D1〜D4)と;を含む。

(もっと読む)

DC−DCコンバータ

【課題】複数のDC−DC変換部を均等に動作させて直流出力電圧を生成可能なDC−DCコンバータを提供する。

【解決手段】DC−DCコンバータは、直流入力電圧を矩形波電圧に変換する複数のDC−DC変換部と、複数のDC−DC変換部の出力端子に一端が接続され、他端が共通の外部出力端子に接続される複数のインダクタ素子と、複数のDC−DC変換部の出力端子にそれぞれ接続され、対応するDC−DC変換部から出力される矩形波電圧のデューティ比を検出する複数のデューティ検出回路と、複数のデューティ検出回路の出力信号を、2つずつ組にした各組ごとに比較した結果に基づいて、各組の矩形波電圧のデューティ比が等しくなるように、各組内の一方のデューティ検出回路に接続されたDC−DC変換部のデューティ比を調整するデューティ調整回路と、を備える。

(もっと読む)

スイッチングコンバータ

【課題】電流臨界モード動作の昇圧コンバータにおいては、リアクトルの充電エネルギが放電を完了した時点でスイッチをターンオフさせる必要がある。そのためにリアクトル電流をシャント抵抗や電流センサで検出したり、リアクトル端子電圧をリアクトルに巻かれた2次巻き線から検出することが行われている。

【解決手段】本発明によれば、スイッチ端子電圧の電圧傾斜の変化を検出することによりリアクトルの充電エネルギの放電完了の検出が可能で、リアクトル電流やリアクトル電圧を検出することなく、電流臨界モードの昇圧コンバータ制御を行うことができる。

本発明をPFCインバータに適用すれば、シャント抵抗などによる電流検出不要の電源システムが実現できる。

(もっと読む)

定電流出力制御型スイッチングレギュレータ

【課題】電流検出用の抵抗器が不要になり、部品点数の削減を図ることができ、該抵抗器に流れる電流による損失をなくすことができる、入力電圧を所望の出力電流に変換して出力する定電流出力制御型スイッチングレギュレータを得る。

【解決手段】クロック信号CLKがハイレベルのときに、スイッチングトランジスタM1に初期電流値i0の電流が流れたときの電流センス電圧VSNSをサンプリングし、クロック信号CLKがローレベルのときに、第1基準電圧VREF1とサンプリングした電流センス電圧VSNSとの電圧差ΔVSを第1基準電圧VREF1に加算して生成した第2基準電圧VREF2と、電流センス回路2の電流センス電圧VSNSとの電圧比較結果を示す信号CPOUTによって、PWM制御時におけるスイッチングトランジスタM1及び同期整流用トランジスタM2の各動作を制御するようにした。

(もっと読む)

短絡保護回路およびDC−DCコンバータ

【課題】スイッチ端子の短絡状態をより速く検出することが可能な短絡保護回路を提供する。

【解決手段】DC−DCコンバータ100は、第1導電型の第1MOSトランジスタM1と、第2導電型の第2MOSトランジスタM2と、第1ドライバ回路3と、第2ドライバ回路6と、コントローラ7と、短絡保護回路101と、スイッチ端子SWとを備える。短絡保護回路101は、電源電位VDDとの短絡を検出する第1論理回路1と、第1検出回路2と、第1抵抗R1と、第1導電型の第3MOSトランジスタM3と、第1導電型の第4MOSトランジスタM4と、を有すると共に、接地電位VSSとの短絡を検出する第2抵抗R2と、第2導電型の第5MOSトランジスタM5と、第2導電型の第6MOSトランジスタM6と、第2論理回路4と、第2検出回路5とを有し、検出結果に基づいた第1、第2検出信号Sd1、Sd2をコントローラ7に出力する。

(もっと読む)

発光素子の調光制御回路

【課題】発光素子の調光を行うための制御回路を提供する。

【解決手段】交流電源を全波整流する整流部30と、発光素子に流れる電流をスイッチングするスイッチング素子38と、整流部30において整流された電圧に応じた導通角でスイッチング素子38のスイッチングを制御するスイッチング制御部42と、導通角が所定角以下である場合にスイッチング制御部42によるスイッチング素子38のスイッチング制御を停止させる発振制御部44と、を備える構成とする。

(もっと読む)

スイッチング電源の制御回路ならびにそれを用いたスイッチング電源および電子機器

【課題】スイッチング電源の高効率化にある。

【解決手段】コンパレータ12は、検出電圧VDSがしきい値電圧VTH_DSより小さくなるとアサートされる比較信号S2を生成する。パルス変調器10は、スイッチング電源2の出力が安定化するようにデューティ比が調節されるパルス変調信号S1を生成する。ドライバ20は、パルス変調信号S1が、スイッチングトランジスタM1のオンに対応する第2レベルに遷移すると、駆動パルス信号S3を、スイッチングトランジスタM1のオンに対応する第3レベルに遷移させる。またドライバ20は、パルス変調信号S1が第1レベルに遷移するタイミングと、比較信号S2がアサートされるタイミングのうち、遅いタイミングで、駆動パルス信号S3を、スイッチングトランジスタM1のオフに対応する第4レベルに遷移させる。

(もっと読む)

スイッチング回路及びDC−DCコンバータ

【課題】スイッチ素子の破壊を防止したスイッチング回路及びDC−DCコンバータを提供する。

【解決手段】ハイサイドスイッチと、整流要素と、駆動回路と、を備えたスイッチング回路が提供される。前記ハイサイドスイッチは、高電位端子と出力端子との間に接続されている。前記整流要素は、前記出力端子と低電位端子との間に、前記低電位端子から前記出力端子に向かう方向を順方向として接続される。前記駆動回路は、入力されるハイサイド制御信号に応じて前記ハイサイドスイッチの制御端子に第1の電圧を供給してオンさせ、前記出力端子の電圧が規定値以上に上昇したとき前記ハイサイドスイッチの制御端子に前記第1の電圧よりも高い第2の電圧を供給する。

(もっと読む)

パルス発生回路

【課題】不定周期でパルス信号を発生させる構成を採用しながら、制御対象による所望の制御を実現できるようにしたパルス発生回路を提供する。

【解決手段】予め定められた所定時間が経過すると、計数回路7のカウンタCO1のカウント値が既定値に達する。すると、計数回路7のカウンタCO1がパルスを出力することで、閾値電圧切換回路8が制御スイッチSW2を用いて比較回路5の比較対象となる閾値を強制的に変更する。その後、インダクタL1の磁気エネルギーが負荷側に伝達されるとノードN4の電圧が低下し、パルス検出回路6がこの電圧低下タイミングを検出するとパルスを出力する。すると、信号発生回路3の出力電圧は初期化される。

(もっと読む)

パルス幅変調制御回路及びその制御方法

【課題】 コンバータ出力側のインダクタンス、静電容量特性の影響を軽減できるパルス幅変調制御信号を提供し、正確な制御及びコスト削減の効果を有するパルス幅変調制御回路を提供する。

【解決手段】コンバータは、アップ、ダウンブリッジエレメントQ1、Q2が入力電源VINに電気的に接続され、位相ノードAを通じてアップ、ダウンブリッジエレメントQ1、Q2を接続し、位相ノードAがドライバー91により駆動されてアップ、ダウンブリッジエレメントQ1、Q2にスイッチング動作を行わせる。位相ノードAが出力インダクタンス92、出力コンデンサ93に接続し、出力インダクタンス92の電流を出力コンデンサ93に充電するよう制御して出力電圧VOUTを生成する。仮想電流リップルのパルス幅変調回路1が位相ノードAの電圧信号を入力すると共に出力電圧VOUT信号に反応し、スイッチング動作を行わせるよう制御する。

(もっと読む)

スイッチング電源装置

【課題】ノイズを減少させて安定的に動作するスイッチング電源装置。

【解決手段】トランスTの一次巻線P1とスイッチング素子Q1との直列回路、Q1をオンオフさせる制御回路、トランスの二次巻線S1に発生した電圧を整流平滑する整流平滑回路D、C1、整流平滑回路の出力電圧と基準電圧との誤差電圧を制御回路に出力する誤差増幅回路OPを備え、制御回路は、Q1をオンオフさせる信号を出力する信号出力部FF、Q1のオフ期間で主電極間の電圧がゼロボルトに近い所定値になったことを検出した場合に、Q1をオンさせる信号が出力されるようにFFを制御するボトム電圧検出部CMP1、FFの出力信号によりQ1のオン数をカウントするカウンタ22、カウント値が所定値に達する毎にQ1をオフさせる信号が遅延されるように遅延時間を切り替えてFFを制御する遅延時間切替回路21を備える。

(もっと読む)

電源制御方法および電源制御装置

【課題】 複雑な構成をとることなく安定してゼロクロスを検出してスイッチング素子の制御を行うことのできる電源制御方法を提供する。

【解決手段】 部分共振波形の立ち上がり部分および立ち下がり部分の位置に基づいて部分共振波形のゼロクロスポイントを推定し、推定されたゼロクロスポイントに基づいてスイッチング素子のON/OFF制御を行う電源制御方法が提供される。

(もっと読む)

スイッチング電源装置

【課題】補助巻線を設けずに、損失を大幅に減らすことができるスイッチング電源装置。

【解決手段】トランス4の1次巻線Pに接続されたスイッチング素子5を有し、トランスの1次側に電圧が入力された場合に制御回路50がスイッチング素子をオン/オフ制御することによりトランスの2次巻線Sに誘起される電圧を整流平滑して負荷に出力するスイッチング電源装置であって、制御回路に電力を供給するコンデンサ12と、制御回路を起動させる場合及びスイッチング素子がオフの場合に、コンデンサに電流を供給する起動回路57と、スイッチング素子の主電極電圧がボトムになったことを検出するボトム検出回路20,25,26,27,28,29,55と、起動回路は、ボトム検出回路がボトムを検出したとき、コンデンサに電流を供給する。

(もっと読む)

電源検出回路及び電源検出回路を備える電源回路

【課題】本発明は、多相電源の異常を検出することができる電源検出回路及び該電源検出回路を備えた電源回路を提供する。

【解決手段】本発明に係る電源回路は、パルス幅変調コントローラと、複数の相回路及び電源検出回路と、を備え、各々の前記相回路は電源信号出力端がそれぞれ形成され、前記電源検出回路は、前記電源信号出力端が正常に動作するかどうかを検出するために用いられ、且つ検出された状況に基づいて電源回路を停止するかどうかを判断する。

(もっと読む)

コンデンサ充電方法および装置

【課題】ゼロ電圧スイッチングスキームを実施するために、スイッチ電圧VSWの勾配の極性変化の検出に応答してスイッチオフ時間が制御される。

【解決手段】フライバックコンバータは、一次巻線18aと出力コンデンサ26に結合された二次巻線18bとを有する変圧器18、一次巻線に結合された端子を有するスイッチ410、およびスイッチのオン時間を制御するための第1の回路部分とスイッチのオフ時間を制御するための第2の回路部分とを有するスイッチ制御回路406を備えており、第2の回路部分は、スイッチ端子の電圧の極性変化を検出するための勾配検出回路を備えている。勾配検出回路は、スイッチ端子に結合された第1の端子および第2の端子を有するコンデンサ412と、コンデンサの前記第2の端子に結合された抵抗器418と、コンデンサの前記第2の端子に結合され、スイッチ端子の電圧の勾配が負の勾配から変化すると、第1の論理レベルから第2の論理レベルに変化する比較器出力信号を提供する比較器420と、を備える

(もっと読む)

昇圧型スイッチングレギュレータの制御回路およびそれを用いたスイッチングレギュレータならびに電子機器

【課題】整流用のダイオードが外れると、スイッチング(SW)端子の電位が上昇する。

【解決手段】スイッチングトランジスタM1は、スイッチング(SW)端子と接地端子の間に設けられる。誤差増幅器10は、出力電圧VOUTに応じたフィードバック電圧VFBと所定の基準電圧VREFとの誤差を増幅し、誤差電圧VERRを生成する。パルス変調器12は、誤差電圧VERRに応じてデューティ比が調節されるパルス信号SPを生成する。ドライバ14は、パルス信号SPにもとづきスイッチングトランジスタM1を駆動する。過電圧検出回路20は、スイッチング(SW)端子の電圧VSWを、所定のしきい値電圧VTHより高くなるとアサートされる過電圧保護(OVP)信号を生成する。制御回路100は、OVP信号がアサートされると、所定の保護処理を行う。

(もっと読む)

1 - 20 / 202

[ Back to top ]