Fターム[5J001CC05]の内容

Fターム[5J001CC05]に分類される特許

1 - 8 / 8

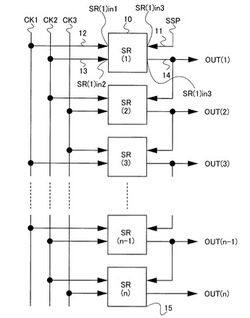

半導体装置、シフトレジスタ、表示装置

【課題】非選択期間においてノイズが少なく、且つトランジスタを常時オンすることのない半導体装置、シフトレジスタ回路を提供することを目的とする。

【解決手段】第1〜第4のトランジスタを設け、第1のトランジスタの、ソースとドレインのうち一方を第1の配線に接続し、他方を第2のトランジスタのゲート電極と接続し、ゲート電極を第5の配線に接続し、第2のトランジスタの、ソースとドレインのうち一方を第3の配線に接続し、他方を第6の配線に接続し、第3のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第2のトランジスタのゲート電極に接続し、ゲート電極を第4の配線に接続し、第4のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第6の配線に接続し、ゲート電極を第4の配線に接続する。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

半導体装置

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

クロック生成回路、電源供給システム及び遅延時間調整部

【課題】一方のクロック信号に対して他方のクロック信号の立ち上がりを遅延させる遅延時間を制御するため、例えば電波状況に応じて、輻射ノイズの低下を図るクロック生成回路、電源供給システム及び遅延時間調整部を提供すること。

【解決手段】コントロール部16は、ワンセグ受信機2から受信したBERデータDBに基づいて、ワンセグ受信機2のビットエラーレートを最も小さくするような、第1及び第2基準クロック信号Ck1,Ck2の周波数の設定周波数データDf、及び、第1基準クロック信号Ck1に対する第2基準クロック信号Ck2の立ち上がりの遅延時間の設定遅延時間データDtに設定し、その設定周波数データDf及び設定遅延時間データDtを基準クロック生成回路21に出力する。基準クロック生成回路21は、入力された設定周波数データDf及び設定遅延時間データDtに基づいて、第1及び第2基準クロック信号Ck1,Ck2を生成する。

(もっと読む)

歪曲されたデューティ比を補正するDLLクロック生成回路

【課題】本発明は、デューティの歪曲を補正したDLLクロックを生成するDLLクロック生成回路を提供する。

【解決手段】本発明のDLLクロック生成回路は、 第1のクロック及び第2のクロックの入力により、第1の内部クロック及び第2の内部クロックを生成し、第1の内部クロックのデューティ比により生成された基準信号に基づき、第1の内部クロック及び第2の内部クロックのデューティを補正するデューティ補正バッファと、デューティ補正バッファに連結しており、第1の内部クロックのイネーブル動作により第1のレベルに遷移され、第2の内部クロックのイネーブル動作により第2のレベルに遷移される、DLLクロックを生成するエッジトリガー部を含む。

(もっと読む)

半導体集積回路、通信装置、情報再生装置、画像表示装置、電子装置、電子制御装置、及び移動体装置

【課題】従来と同一構造の伝送線路で、従来に比べ高転送レートにて伝送を実現できるようにする。

【解決手段】与えられた外部データ信号DINを送信する送信回路110を備えた半導体集積回路において、送信回路110を次のように構成する。すなわち、送信回路110には、リファレンスクロックCKを入力とし、リファレンスクロックCKに同期して外部データ信号DINを保持する送信用フリップフロップ回路111と、リファレンスクロックCKをn/m倍(m、nは2以上の整数かつm>n)に分周して出力する分周回路112と、送信用フリップフロップ回路111が保持しているデータ信号を伝送するデータ信号用バッファ回路113と、分周回路の出力を伝送するクロック用バッファ回路114とを設ける。

(もっと読む)

クロック遅延補正回路

【課題】クロック分配回路のクロック遅延を補正するクロック遅延補正回路で固定遅延手段を除き、設計時における設計検証を容易にする。

【解決手段】クロック遅延補正回路10は、分配クロックCLKの周期を示す周期データを生成する周期データ生成手段11と、可変遅延時間を持ち分配クロックCLKを遅延して出力クロックCOUT1を生成する可変遅延回路121と、出力クロックCOUT1の位相と基準クロックCREF1の位相とを比較する位相比較回路122と、位相比較回路122の比較結果に従ってカウントUPするカウンタ123とを有し、カウンタ123のカウント値で可変遅延回路121の遅延時間を制御する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 周波数が周期的に変動するスペクトラム拡散クロックに発生するジッタを小さく抑えるとともに、そのスペクトラム拡散クロックのデューティ比の悪化や周波数変調の特性の悪化を小さく抑えることができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 遅延回路10を構成する遅延セル11が2入力NANDゲートからなり、遅延回路10にクロックCLKを入力するクロック入力回路21,22,23,24,25,26が2入力ANDゲートとNORゲートからなり、複数の変調度を実現するためのバイパス回路4が2入力NANDゲートからなるものであって、第1のモードでは遅延回路10の第1ポイントP1まで伝搬してきたクロックCLKをその直近の遅延セル11に伝え、第2のモードでは第1ポイントP1まで伝搬してきたクロックCLKを、遅延回路10の途中をバイパスして、第2ポイントP2の遅延セル11に入力する。

(もっと読む)

1 - 8 / 8

[ Back to top ]