Fターム[5J001DD00]の内容

パルス回路 (4,711) | 機能 (1,034)

Fターム[5J001DD00]の下位に属するFターム

Fターム[5J001DD00]に分類される特許

41 - 48 / 48

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】基準信号と内部クロック信号とが同期しているか否かを瞬時に判断することによって検査効率を向上させることができる遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路を提供する。

【解決手段】遅延同期ループ回路に、各タップ信号をクロック信号とする複数のフリップフロップを直列に接続することによってシフトレジスタを形成し、複数のフリップフロップにクロック信号として基準信号からの遅延時間の長いタップ信号から順に入力した場合に、このシフトレジスタから出力される第1の検査信号と、複数のフリップフロップの全てにクロック信号として基準信号を入力した場合に、このシフトレジスタから出力される第2の検査信号とを検出し、これらの第1の検査信号と第2の検査信号との差に基づいて良否を判定することとした。

(もっと読む)

レベルシフト回路

【課題】 小規模な回路構成で入力信号と出力信号の電圧差が大きい場合であっても十分に動作し、かつ入力信号と出力信号との間で、デューティサイクル及び位相が同一であるレベルシフト回路を提供する。

【解決手段】 レベルシフト回路(3)は、所定の第1正側電源電圧VDD1と所定の負側電源電圧との間の振幅を有する2値の相反するレベルの一対の入力信号を、第1正側電源電圧VDD1よりも大きい所定の第2正側電源電圧VDD2と負側電源電圧との間の振幅を有する2値の相反するレベルの一対の信号にレベルシフトさせて出力する。レベルシフト回路(3)は、一対の入力信号を第2正側電源電圧VDD2と負側電源電圧との間の振幅を有する2値の信号にそれぞれレベルシフトさせて出力するレベルシフト回路部(4)と、レベルシフト回路部(4)からそれぞれ出力された2つの信号のレベル変化のタイミングを調整するタイミング調整回路部(5)とを備える。

(もっと読む)

ディジタルインターフェースを有する半導体装置、メモリ素子及びメモリモジュール

【課題】

本発明の課題は、インターフェースのレシーバにて、データパターンに依存するジッタを低減することにある。そして、低減するための遅延量の設定を装置毎に調整できるように自動的に調整可能なLSIを提供することにある。

【解決手段】

データパターン依存ジッタは、前の状態がどの様であったかで予測可能であるので、レシーバにて受け取ったデータの状態を保持しこの保持された状態と、入力されたデータとから入力データの取り込みタイミングを調整する。

また、実装形態に依存する遅延量を決定するためのレシーバ内の調整機構として、ドライバから1サイクル間隔のパルスデータ、2サイクル間隔のパルスデータをテストパターンとして送受信する。パルス幅の異なるパルスの立上りと立下がり時間差から系に最適な遅延量を求める自動調整機構を持つ。

(もっと読む)

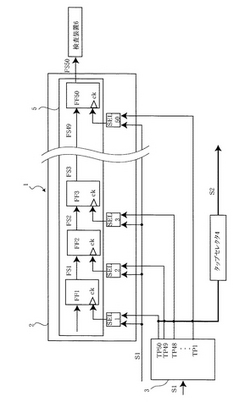

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】

ディジタルデータをもとに良否判定可能な比較的安価な検査装置を用いて遅延同期ループ回路の良否検査を行うことができる遅延同期ループ回路の良否検査方法及び、遅延同期ループ回路の良否検査回路を提供する。

【解決手段】

基準信号を所定時間ずつ遅延させたN個のタップ信号を出力する遅延同期ループ回路の良否検査回路及びこの良否検査回路により行う良否検査方法において、各タップ信号をクロック信号とするN個のフリップフロップといずれかのタップ信号をクロック信号とするフリップフロップとを直列接続することによってシフトレジスタを形成し、このシフトレジスタを基準信号の1周期分動作させて、N個目のフリップフロップの出力信号とN+1個目のフリップフロップの出力信号とに基づいて遅延同期ループ回路の良否を判定することとした。

(もっと読む)

パルス信号生成回路及びこのパルス信号生成回路を有するSRAM

【課題】

回路規模を縮小できるとともに、任意のパルス幅の出力パルス信号を生成することができるパルス信号生成回路及びこのパルス信号生成回路を有するSRAMを提供する。

【解決手段】

データを記憶する記憶回路と、この記憶回路を動作させる駆動回路と、この駆動回路を駆動させるための出力パルス信号を生成するパルス信号生成回路とを有するSRAMにおいて、パルス信号生成回路は、クロック信号が非アクティブ状態からアクティブ状態に切替わると、出力パルス信号を強制的にアクティブ状態に切替えるアクティブ切替え回路と、クロック信号がアクティブ状態から非アクティブ状態に切替わっても出力パルス信号の状態をそのまま保持する保持回路と、クロック信号の状態に関わらず、切替え信号が非アクティブ状態からアクティブ状態に切替わると、出力パルス信号を強制的に非アクティブ状態に切替える非アクティブ切替え回路とを有することとした。

(もっと読む)

パルス幅変調回路

【課題】

高速、高精度の動作を実現できるパルス幅変調回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路では多相クロック生成回路2によって基準クロックに基づき多相クロック信号を生成する。そして、入力データと、多相クロック生成回路2によって生成された多相クロック信号とに基づいてパルス幅変調信号を生成する。ここで、多相クロック生成回路2は、位相ロックループ回路を有し、位相ロックループ回路によって生成された中間クロック信号をさらに位相補間することにより多相クロック信号を生成する。

(もっと読む)

クロック信号の補正に適したクロック信号入出力装置

本発明は、クロック信号入出力装置(1、101)に加えて、クロック信号補正方法に関するものである。本発明の方法では、クロック信号(clk)または該クロック信号から得られた信号を、上記装置に入力し、分周器(4、104)に伝送し、分周器(4、104)から出力された信号、または、該信号から得られた信号(clk2)を、信号積分器(6、106)に伝送し、該信号積分器(6、106)から出力されるか、または、該信号から得られた信号(I2)を、第1信号比較回路(8、108b)に伝送する。さらに、分周器(4、104)から出力された信号、または、該信号から得られた信号(clk2)を、第2信号比較回路(9、109a)に伝送し、クロック信号用の入出力装置(1)は、第1信号比較回路(8、108)から出力された、または、該信号から得られた信号(rIclk)に応じて、および、第2信号比較回路(9、109a)から出力された、または、該信号から得られた信号(rclk)に応じて、クロック出力信号(clk50)を出力するための、信号出力回路(11、111)を備えている。  (もっと読む)

(もっと読む)

クロックパルス幅調整回路

【課題】半導体集積回路の動作速度を保証すると共に、ダイナミック回路の動作時のピーク電流が単一時間に集約されることを防ぎ、EMIを抑制することを目的とする。

【解決手段】トランジスタ駆動能力測定回路333によりプロセスのばらつきによるトランジスタの駆動能力を測定し、クロックパルス変更回路444にて測定結果に基づいてクロックパルスの立ち上がりおよび立ち下りのタイミングを変更することにより、最適なタイミングでダイナミック回路251を動作させることができ、半導体集積回路の動作速度の保証を行うことができる。

(もっと読む)

41 - 48 / 48

[ Back to top ]