Fターム[5J001DD00]の内容

パルス回路 (4,711) | 機能 (1,034)

Fターム[5J001DD00]の下位に属するFターム

Fターム[5J001DD00]に分類される特許

21 - 40 / 48

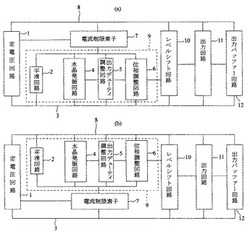

パルス発生回路

【課題】発振周波数が数MHz〜GHzの高周波用に適用可能であり、かつ消費電力が少ない、定電流回路を用いたパルス発生回路を提供すること。

【解決手段】パルス発生回路は、電源間に定電圧回路1を有し、電流制御素子7と波形発生部9とを直列に接続して、それらを定電圧回路1と並列に接続して構成されている。そして、波形発生部9は、平滑回路2と、水晶発振回路4と、水晶発振回路4からの出力を受けて最終出力波形のデューティ比を調整する出力デューティ調整回路5と、水晶発振回路4の発振波形と最終出力波形との位相差を調整する位相調整回路6と、を並列に接続して構成されている。使用する水晶振動子の周波数によっては、位相調整回路6の替わりに分周回路を並列に接続して構成されている。

(もっと読む)

多段インバータのデューティサイクル歪みの低減する装置および方法

【課題】インバータ回路のデューティサイクル歪みを改善する。

【解決手段】多段インバータ100回路は、少なくとも第1、第2、第3ステージ110、120、130を含む。インバータ100回路の段数をL、最後の段と第1ステージのサイズ比をNとするとき、第mステージのサイズと、m段目の一つ前段の第m−1ステージのサイズの比Rm,m−1を、N(1/(L−1))より小さくする。

(もっと読む)

クロック生成回路

【課題】

要求されるデューティ比の同期クロック信号を生成できるか否かの判別が正確に行われるクロック生成回路を提供する。

【解決手段】

クロック生成回路100において、外部から入力されてきた外部クロック信号Sextclkを遅延することにより外部クロック信号Sextclkに同期した同期クロック信号Sclkを生成するDLL回路110と、DLL回路110のデューティ比劣化テスト用にパルス幅を変化させたテスト信号Stestを生成するテスト信号生成回路120と、外部クロック信号Sextclkおよびテスト信号Stestのうちの一方の信号を選択してDLL回路110に入力する選択回路130とを備えたことを特徴とする。

(もっと読む)

メモリ制御装置

【課題】DDR/DDR1/LPDDR SDRAMの動作クロックの切り替わりに応じてデータ・ストローブ信号DQSの位相を好適に調整する。

【解決手段】メモリ・コントローラは、動作周波数レンジの異なる複数のDLLを備え、動作周波数毎にDLLを選択的に使用して動作周波数レンジを切り替えることによって、SDRAMの広い動作クロック範囲に対応する。また、DLLの他に1以上のDLも備え、DLを使用して位相調整を行なうモードと、DLLを使用して位相調整を行なうモードを有し、SDRAMを低速動作で使用するときには、DLLを使用せずにDLモードで動作させて、消費電力を削減する。

(もっと読む)

クロック信号のデューティサイクルを補正するための補正装置

【課題】クロック信号のデューティサイクル補正を行うために、確実かつ簡便に実現される技術を提供する。

【解決手段】クロック信号(CLK)から第1グループおよび第2グループのn個の遅延された各バージョンをそれぞれ生成するために各遅延デバイス(DA、DB)を設ける。第1グループの各バージョンでは前側エッジが後側エッジに対して時間増分τだけずつ段階的に遅延し、第2グループの各バージョンでは後側エッジが前側エッジに対して時間増分τだけずつ段階的に遅延する。第1グループの信号が消失する点での遅延増分値の順序数xを確定する。第2グループの各信号が発振が消失する点での遅延増分値の順序数yを確定する。遅延補正デバイス(DC)を、x>yまたはx<yである場合にクロック信号のパルスの前側エッジまたは後側エッジを(V=τ×|x−y|/2)だけ遅延して補正クロック信号CLK’を得るために制御可能に設ける。

(もっと読む)

デジタルDLL回路

【課題】外部のゲート遅延誤差を電源電圧や温度、プロセス変動があっても容易に打ち消すことができ、遅延誤差判明後のLSI作り直しやDLLとは別の遅延調整機構追加が不要とすることが可能なデジタルDLL回路を提供する。

【解決手段】遅延指定のための遅延指定値を保持する第1レジスタ11、LSI内部のゲート遅延補正値を指定するための第2レジスタ12、デジタル制御の可変遅延回路13、可変遅延回路13の遅延を第1レジスタ11の遅延指定値に維持するよう制御を行うように遅延制御値DCVを生成する制御回路15、制御回路から出力される遅延制御値DCVに第2レジスタ12が保持するゲート遅延補正値GDCVを加算し、可変遅延回路13の制御入力へ出力する加算回路15を有する。

(もっと読む)

差動クロック信号のデューティサイクル歪みを補正する回路および方法

【課題】差動増幅器を介して伝搬する差動クロック信号のデューティサイクル歪みの補正に対する完全に差動的な手法を提供する。

【解決手段】デューティサイクル歪み補正(DCDC)差動増幅器回路/デバイスは、出力線が補正回路に結合される差動増幅器を備える。補正回路は、差動低域フィルタおよび差動補正増幅器を含む。差動補正増幅器の出力は、増幅器の出力にドットバック(dotted back)される。増幅器の差動出力は、低域フィルタに通され、この低域フィルタは、各差動出力パルスに足し戻される反転された補正電流を生成するために、各補正増幅器のトランジスタを作動させる差動DC出力信号を供給する。DCDC差動増幅器は、差動出力の中のデューティサイクル歪みの補正に対する完全に差動的な手法を提供する。

(もっと読む)

低ノイズ遅延回路を有する電子回路

電子回路が、ループの形に結合された鋸歯状波遅延段(10a〜d)のチェインを有する遅延回路を備えて、例えば発振器を形成する。各段は、積分回路(104)、及び積分回路(104)に結合された電流変調器(106)を備えている。各段は、積分結果が基準電圧によって規定されるレベルに達すると、次の段における遷移をトリガする。相関回路(102、30、32、34)は、電流変調器(106)への電流、及び鋸歯状波遅延段(10a〜d)用の基準電圧を発生するための電流出力を備えている。基準電圧は、少なくとも一部は共通基準電流源(102c)から発生し、これにより、電流変調器(106)からの電流中のノイズと基準電圧中のノイズとが、遅延時間に対するこれらノイズの影響が少なくとも部分的に相殺される方法で相関される。  (もっと読む)

(もっと読む)

遅延セル及びこれを備える遅延ライン回路

【課題】遅延セル及びこれを備える遅延ライン回路を提供する。

【解決手段】遅延ライン回路は、直列に連結される複数の遅延セルを備える。前記遅延セルの各々は、第1ないし第3ロジックゲートを備える。第1ロジックゲートは、選択信号に応答して、入力信号に基づいた信号を発生させる。第2ロジックゲートは、選択信号に応答して入力信号に基づいた信号を発生させる。第3ロジックゲートは、リターン信号または第2ロジックゲートの出力信号に基づいた信号を発生させる。第1ないし第3ロジックゲートは、各々NANDゲートあるいはNORゲートであり得る。本発明によれば、遅延セルあるいは遅延ライン回路の出力信号の特性、特に、デューティー特性が改善される。

(もっと読む)

位相調整回路

【課題】入力される複数の信号の位相を補償し、これら信号の位相の単調増加性を向上する位相調整回路の実現する。

【解決手段】位相調整回路は、第1から第nの二位相調整回路(10)を備えている。各二位相調整回路(10)は、入力された二つの信号の論理和を演算する第1の論理回路(105)、論理積を演算する第2の論理回路(107)、第2の論理回路(107)と同等の信号遅延量を有し、第1の論理回路(105)の出力信号を遅延させる第1の遅延回路(108)、及び第1の論理回路(105)と同等の信号遅延量を有し、第2の論理回路(107)の出力信号を遅延させる第2の遅延回路(106)を備えている。ここで、二つの二位相調整回路(10)の出力信号は、次段の二位相調整回路(10)の入力信号となる。

(もっと読む)

遅延固定ループ

【課題】遅延固定ループでコース遅延時間とファイン遅延時間とを別に制御して、高周波数動作を行うと共に、ジッタを低減できる遅延固定ループを提供すること。

【解決手段】プリ遅延ラインとポスト遅延ラインとを直列に接続して、各々のコース遅延を有し、立ち上がりクロックと立下りクロックとの位相比較により、遅延ラインの動作を制御する遅延ライン制御部を備え、デューティーサイクル補正動作の開始時、2つのファイン遅延の動作タイミングを異なるように制御し、プリ遅延ラインの補正に関する情報をポスト遅延ラインに出力して、ポスト遅延ラインで2回の遅延補正が可能なようにすることによって、デューティー補正速度を向上させることができるようにする。

(もっと読む)

遅延回路

【課題】プロセス変動及び電源電圧の変動による遅延時間の変動を補償することが出来る遅延回路を提供する。

【解決手段】通常のCMOSタイプのインバータ10,30と、電源電圧VDD端子側に遅延用のPMOSを追加した変形インバータ20P,40Pとを交互に縦続接続した遅延回路に対して、遅延用のPMOS23,43のゲートに制御信号VPを与える補正回路60を設けている。補正回路60は、順方向にダイオード接続されたPMOS61と、このPMOS61のドレインを接地電圧VSSの端子側に接続する抵抗62,63とにより構成され、この抵抗62,63間の内部ノードN60から制御信号VPを出力している。これにより、電源電圧VDDが上昇すると制御信号VPの電圧も上昇し、遅延用のPMOS23,43のゲート・ソース間電圧が一定に保たれ、ドレイン電流は変化せず遅延時間も一定に保たれる。

(もっと読む)

半導体メモリ装置

【課題】ODT動作タイミングを容易に調節できる半導体メモリ装置を提供すること。

【解決手段】本発明の半導体メモリ装置は、データ入力パッドと、外部から入力されるODT信号を入力されたデコード値に対応するインピーダンス値の選択信号として出力するODT動作制御部と、前記インピーダンス値の選択信号に応答しインピーダンス値を調節するためのインピーダンス調整回路部と、内部生成されるODT制御信号を、第1タイミングと同じタイミングだけ遅延させて出力するための第1遅延調整部と、前記出力された信号を第2タイミングと同じタイミングだけ遅延させて出力するための第2遅延調整部と、現在の状態が、モジュールの第1ランクと第2ランクのどちらで用いられるのかによって、前記第1遅延調整部の出力または第2遅延調整部の出力を前記ODT信号の制御で行うODTタイミング制御部とを備える。

(もっと読む)

デューティ比可変回路およびこれを用いたAD変換回路

【課題】

入力信号のスルーレートを可変して、出力パルスのデューティ比を変える。

【解決手段】

制御信号に応じて入力信号のスルーレートを可変する第1のインバータ21と、第1のインバータから出力されたパルス信号を反転する第2のインバータ22と、第2のインバータ出力からのパルス信号のレベルを平均化する積分器と、記積分器からの出力信号と基準値を比較し、比較結果に応じて制御信号を前記第1のインバータに出力する増幅器26とを有し、制御信号に応じてスルーレートを可変し、第2のインバータから出力されるパルス波形のデューティ比を可変する。

(もっと読む)

半導体集積回路

【課題】 クロックスキューを低減し、動作マージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】 遅延回路8による遅延時間DL1とクロックツリー11による遅延時間DL11との和が、遅延回路9による遅延時間DL2とクロックツリー12による遅延時間DL12との和と等しくなるように、遅延回路8,9の遅延時間DL1,DL2が調整される。このように、予め任意に遅延時間をプログラムすることができるプログラマブル遅延回路8,9を設けたことによって、機能ブロック3,4に供給される内部電源電圧V1,V2の差が大きい場合でも、機能ブロック3,4間のクロックスキューを低減することができる。したがって、低消費電力の半導体集積回路において、クロックスキューを低減することができ、動作マージンを十分に確保することが可能になる。

(もっと読む)

遅延回路

【課題】ディレイラインのディレイセルの段数に関わらず、ディレイラインを通過させた後の出力信号のデューティの崩れを軽減することができる遅延回路を提供する。

【解決手段】遅延回路は、入力信号の立上りおよび立下りを検出して、そのエッジから所定のパルス幅を持つ検出信号を出力するエッジ検出回路と、検出信号を所定の時間遅延して遅延信号を出力するディレイラインと、遅延信号の立上りだけまたは立下りだけに基づいて、入力信号に略等しい周波数およびデューティを持ち、入力信号がディレイラインによる遅延時間だけ遅延された出力信号を出力する信号再生回路とを備える。

(もっと読む)

半導体集積回路およびその検査方法

【課題】 半導体集積回路の検査において遅延故障検出の容易化を図る。

【解決手段】ゲート101〜112の中から非インバータ系のゲート101〜103,106,108,110〜112を抽出する。抽出したゲートを出力段の論理を反転したゲート101−1〜103−1,106−1,108−1,110−1〜112−1に置換する。置換したゲートの後段にインバータ101−2〜103−2,106−2,108−2,110−2〜112−2を付加する。データフリップフロップ201〜204は反転出力QNを後段のSI端子に接続する。このようにして回路内部の伝搬信号のトグル率を向上させる。状態遷移の頻度が高まるので遅延故障検出が容易になる。

(もっと読む)

信号処理装置

【課題】簡単な回路構成で、入力信号レートに応じて、デューティサイクルが約50%に近いクロック信号を生成し得る信号処理装置を提供する。

【解決手段】バーストモードのシリアル信号をパラレル信号に変換したときに得られる入力クロック信号と有効データ識別パルスとを利用して、カウンタ142により有効データ識別パルスの入力タイミングから次の有効データ識別パルスの入力タイミングまでの入力クロック信号のクロック数をカウントし、乗算器145にてこのカウント値の1/2の値を求め、比較器146にてこの1/2の値とカウンタ142のカウント値とを比較し、この比較結果に基づきFF回路143にて有効データ識別パルス周期の略1/2期間で立ち上がりまた略1/2期間で立ち下がりへ変化する出力クロック信号を生成する。

(もっと読む)

デューティ比補正回路

【課題】パルス発生器等から供給されるパルスのデューティ比を補正する回路において、容量を小量化して応答性を向上する。半導体集積回路のチップ面積を小さくする。

【解決手段】PLLoutがデューティ比50%未満だとクロックパルスのデューティ比は50%を上回る。AVR>Vdd/2となってコンパレータ7の出力CoutがHとなり第2のスイッチング増幅回路8がオンする。コンデンサC2によりバイアス信号BIASが高くなる。FET21の電流制御により出力点Q1の信号のパルス幅が長くなる。クロックパルスのデューティ比が低く補正されて50%に近付く。コンデンサ2により積分した信号はFET21,24へのバイアス信号BIASとなるから小電流で済む。コンデンサC2の容量を小さくできる。チップ面積を小さくできる。応答性が向上する。

(もっと読む)

2つのPLLを用いた微小時間差回路及び時間測定回路

【課題】1桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得る。

(もっと読む)

21 - 40 / 48

[ Back to top ]