Fターム[5J001DD01]の内容

Fターム[5J001DD01]の下位に属するFターム

Fターム[5J001DD01]に分類される特許

1 - 20 / 30

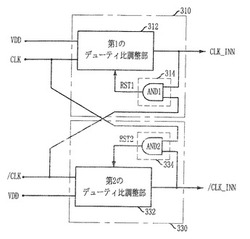

デューティ比補正回路

【課題】入力される外部クロック信号の活性化エッジを用いてデューティ比を補正することができるデューティ比補正回路を提供する。

【解決手段】本発明のデューティ比補正回路は、第1の基準クロック信号及びリセット信号に応じて定義されるデューティ比の内部クロック信号を生成するデューティ調整手段と、第2の基準クロック信号及びフィードバックされる前記内部クロック信号に応答して前記リセット信号を生成するリセット信号生成手段とを備えることを特徴とする。

(もっと読む)

相変化物質に基づくプログラマブル抵抗を用いた遅延発生器

【課題】 相変化物質に基づくプログラマブル抵抗を用いた遅延発生器を提供する。

【解決手段】 本発明は、カルコゲナイドに基づく相変化物質で作られる少なくとも1つのプログラマブル抵抗RPCM(11)を含み、前記抵抗RPCMが、遅延を発生させるために、抵抗RPCMの抵抗値が所定の初期値R0に等しく、そしてカルコゲナイドが非晶相であるようなやり方で初期化され、比較器(13、16、19)が、時間の経過に対して安定な基準電気量を、プログラマブル抵抗RPCM(11)の抵抗値を表わす可変電気量と比較し、比較器が特異信号sを発生させ、前記特異性が、その2つの電気量の間の差が符号を変えるときに生成される、遅延発生器に関する。

(もっと読む)

遅延回路およびシステム

【課題】 遅延段の数を切り換えるときの遅延時間の増加量および減少量を一定にすることで、高い精度を有する遅延回路を形成する。

【解決手段】 遅延回路は、直列に接続された複数の遅延段、検出回路および調整回路を有する。各遅延段は、前段からの信号を反転して後段に伝達する第1遅延素子と、後段からの信号を反転して前段に伝達し、または前段からの信号を反転した遅延信号を反転して前段に伝達する第2遅延素子とを含む。検出回路は、奇数段目および偶数段目の遅延段において、前段からの信号を受けてから遅延信号を経て第2遅延素子から信号が出力されるまでの伝搬遅延時間をそれぞれ検出する。調整回路は、検出回路の検出結果に基づいて、奇数段目および偶数段目の遅延段の伝搬遅延時間を互いに等しくする。

(もっと読む)

パルス発生回路

【課題】入力信号にジッタが含まれていても安定した時間幅のパルスを出力する。

【解決手段】パルス発生回路は、ゲートが入力端子2に接続され、ソースが電源電圧VDDに接続されたPMOSトランジスタQ1と、ゲートが入力端子2に接続され、ドレインがPMOSトランジスタQ1のドレインに接続され、ソースが出力端子3に接続されたNMOSトランジスタQ2と、一端が出力端子3に接続され、他端が接地電圧VSSに接続された負荷インピーダンスZout1とを有する。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号が入力され、入力されたクロック信号の波形の立ち上がりに合わせて波形が立ち上がりパルス幅が一定の幅であるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力が一方の入力側に入力される否定論理和回路120と、否定論理和回路120の出力信号を遅延させる第1遅延回路130を有し、第1遅延回路130により遅延された否定論理和回路120の出力を否定論理和回路120の他方の入力側にフィードバックする帰還回路140と、否定論理和回路120の出力信号が入力される第2ローパスフィルタ150と、を備える。

(もっと読む)

TDC装置とTDCのキャリブレーション方法

【課題】遅延素子の遅延時間のばらつきに対してTDCの変換特性を一定とし線形性を実現可能なTDCの提供。

【解決手段】第1の信号DATAを順次遅延させる複数段の遅延素子111〜11Nを有するディレイライン10と、第2の信号CLKに応答して複数段の遅延素子の出力をサンプルする複数のフリップフロップ121〜12Nと、相隣るフリップフロップの出力結果が切り替わるエッジ位置を、第1の信号の第2の信号に対する位相差として検出するエッジ検出器13と、を備え、エッジ位置の検出結果に基づき、バイアス制御用の制御コードICNTを生成するキャリブレーション制御回路15と、制御コードに対応する複数段の遅延素子に対して供給するバイアス発生回路14を備え、第1の信号の周波数範囲に対応した段数の遅延素子に、第1の信号のエッジが位置するように遅延素子111〜11Nの遅延時間の校正を行う。

(もっと読む)

パルス幅制御回路及び半導体メモリ

【課題】トランジスタのプロセス依存と配線幅のばらつきとに応じて適切なパルス幅に制御することが可能なパルス幅制御回路及び半導体メモリを提供すること。

【解決手段】配線による遅延とインバータによる遅延とを比較する比較回路と、インバータ段数によりパルス幅を調整するパルス幅調整回路と、を備える。パルス幅調整回路は、比較回路の比較結果に基づいて、インバータによる遅延が配線による遅延よりも小さくなった場合に、インバータ段数を多くし、パルス幅を増加させる。

(もっと読む)

パルス幅調整回路及びこれを用いたデューティ比補正回路

【課題】入力クロック信号のパルス幅を安定して調整すること。

【解決手段】第1及び第2の電源間に設けられたパルス幅調整回路であって、ゲートに入力パルス信号INが入力される第1導電型の第1のトランジスタP1と、第1のトランジスタP1と第2の電源との間に設けられ、ゲートに入力パルス信号INが入力される第2導電型の第2のトランジスタN1と、第1のトランジスタP1と第1の電源との間に設けられ、ゲートに入力される第1の制御信号に応じて流れる電流が制御される第1導電型の第3のトランジスタP2と、第1のトランジスタP1と第1の電源との間に、第3のトランジスタP2と並列に設けられた第1の電流源回路102と、を備えるパルス幅調整回路。

(もっと読む)

フリップフロップ、半導体集積回路、半導体デバイスおよびブレードサーバ

【課題】

回路オーバヘッドが小さく、かつ、ソフトエラーへの耐性が高い、高ソフトエラー耐性のフリップフロップおよび、それを用いた半導体集積回路を提供する

【解決手段】

ソフトエラーに対する耐性の異なる複数のラッチ回路と、前記複数のラッチ回路にクロックを供給するクロック分配部と、を備えたフリップフロップであって、前記複数のラッチ回路は、第一のラッチ回路と、前記第一のラッチ回路よりもソフトエラーに対する耐性の低い第二のラッチ回路の少なくとも2つのラッチ回路であることを特徴とするフリップフロップ。

(もっと読む)

DLL回路

【課題】LPF出力の変化に対するロック周波数の変化量のゲイン設定のばらつきの抑制でジッタ精度をより向上できるDLL回路の提供。

【解決手段】遅延クロックを生成する遅延回路101と、遅延クロックと入力クロックの位相差信号を出力する位相比較回路10と、位相差信号対応の位相差電圧を出力するチャージポンプ回路20と、チャージポンプ回路出力の高周波成分を除去するローパスフィルタ回路30と、ローパスフィルタ回路の出力電圧を電流に変換する第1電圧−電流変換回路40及び基準電圧Vrefを電流に変換する第2電圧−電流変換回路50を含み、第1電圧−電流変換回路の出力電流から第2電圧−電流変換回路の出力電流を減算した結果を変換した電圧とオフセット電流Idを変換した電圧とを含み、位相差電圧が基準電圧より小の場合、オフセット電流を変換した電圧を制御電圧Vcontとして遅延回路に出力する遅延制御回路102と、を備える。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法

【課題】デューティ制御バッファの出力信号のパルスが消滅してしまうという問題を回避する回路を提供する。

【解決手段】入力信号IN1、INB1を受けるデューティ制御バッファ10と、デューティ制御バッファの出力OUT1、OUTB1を受け、デューティの誤差を検出して制御信号VCNT1、VCNTB1を生成するデューティ制御電圧発生部20を備える。デューティ制御バッファ10は、入力信号を差動で受ける第1の差動対と第2の差動対を備えた差動段と、第1の差動対の出力対と第2の差動対の出力対がそれぞれ接続され、前記第1、第2の差動対の出力対と電源との間に接続された負荷素子対と、第1、第2の差動対にそれぞれ駆動電流を供給する電流源段とを備え、第1の差動対のトランジスタ対の電流駆動能力が異なり、第2の差動対のトランジスタ対の電流駆動能力が異なる不平衡差動対よりなる。

(もっと読む)

クロックデューティサイクル適合による半導体デバイスの性能の低下の補償

【解決手段】

集積回路のデバイス劣化が、クロック信号のデューティサイクルを適切に適合させることによって補償され得る。この目的で、デューティサイクルと集積回路の全体的な性能特性の間での相関が確立されてよく、またデューティサイクルを修正するためにデバイスの通常の分野の動作の間に用いられてよい。従って、デューティサイクルが効果的に制御され得る一方で、同時にクロック信号周波数の変化及び/又は供給電圧の増大は必要とされないであろうから、効果的な制御戦略の実装が可能になる。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

CML−CMOS変換器

【課題】CMLレベルでスイングする信号をCMOSレベルでスイングする信号に変換する過程において、デューティ比の不一致を防止するCML−CMOS変換器を提供すること。

【解決手段】第1基準レベルを中心にスイングする正CML信号を第2基準レベルにシフトする第1基準レベルシフト部、第1基準レベルを中心にスイングする負CML信号を第2基準レベルにシフトする第2基準レベルシフト部、第1基準レベルシフト部の出力信号のスイング幅をCMOSレベルに増幅する第1CMOS反転部、第2基準レベルシフト部の出力信号のスイング幅をCMOSレベルに増幅する第2CMOS反転部、第1CMOS反転部の出力信号に応じて第1及び第2CMOS反転部にソース電流を提供する第1バイアス部、第1CMOS反転部の出力信号に応じて第1及び第2CMOS反転部にシンク電流を提供する第2バイアス部を備えるCML−CMOS変換器を提供する。

(もっと読む)

位相調整装置

【課題】設計時以降に生じる位相差の変動を内部で自動的に調整することで、予め設定された位相差を有する2つの信号を出力する。

【解決手段】2つのクロック信号の位相差を予め定められた位相差に調整する位相調整装置であって、第1クロック信号に対する第2クロック信号の遅延量を選択的に変更可能な遅延部11と、前記遅延量を制御する制御部12とを備え、前記制御部12は、準備モードにおいて、前記遅延量を第1の時間間隔で段階的に増加又は減少させ、遅れ期間、又は、進み期間を検出し、調整モードにおいて、前記遅れ期間又は前記進み期間と同じ長さの期間において第2の時間間隔で前記遅延量を段階的に変化させることで、前記第2クロック信号の位相差を予め定められた位相差に調整し、前記第2の時間間隔と前記第1の時間間隔との比は、180度と予め定められた位相差との比に等しい。

(もっと読む)

電子回路装置

【課題】パルス幅を意図的に変化させるNRZ等の信号の伝送において、パルス幅のバラツキの低減を図り、さらにジッタの低減も図る。

【解決手段】2個のエッジ検出回路11,12と、2個の可変遅延回路13,14と、SRラッチ回路15とを備え、可変遅延回路13,14のそれぞれの入力にエッジ検出回路11,12の出力を接続し、SRラッチ回路のS入力およびR入力それぞれに可変遅延回路13,14の出力を接続する。前記SRラッチ回路15が、可変遅延回路13,14の出力のパルス終端側エッジを検出してセット/リセット動作を行う。

(もっと読む)

半導体集積装置

【課題】0リードおよび1リードをともに遅延しにくい状態で動作させることのできる半導体集積装置を提供。

【解決手段】調整回路100は、アドレス推移検出信号(ATD)を入力し、電圧Vp生成回路142と電圧Vn生成回路132とからそれぞれ供給される電圧Vpおよび電圧Vnのレベル変動に応じて、信号ATDEQ 32のパルス幅を調整して出力する。

(もっと読む)

フィードバック制御により遅延量を連続的かつ精密に可変設定可能なパルス遅延回路システム

【課題】100pSないしnSオーダーの極短時間の遅延時間であっても長期間、安定に保持でき、設定操作も簡単な実用性に優れたパルス遅延回路システムを提供する。

【解決手段】遅延量を定めるアナログ制御信号の入力端子を備えた遅延回路1で基準パルス列信号DIを遅延して、遅延パルス列信号を端子SOから得る。基準パルス列信号DIと遅延したパルス列信号との立ち上がりの時間差を検出し、遅延時間差を示すパルス列を得、このパルス列を平滑し脈動信号eを得る。この脈動信号eが示す現在の遅延時間と、目標の遅延時間を示す外部制御信号VCIが示す目標の遅延時間との誤差をオープンゲイン1万倍以上の演算増幅器7で増幅し、かつ当該演算増幅器7が構成する積分回路で積分する。演算増幅器7の出力を、遅延回路1に遅延時間を決めるアナログ制御信号として出力する。

(もっと読む)

デジタル型ヘリウム−ネオン安定化レーザ

【目的】 安定化のために、デジタル量を用いる安定化ヘリウム−ネオンレーザの高度の安定度をうるため、デジタルのパルスの形状を正確に揃える手段の提供を行なうと共に、前記安定化のためのデジタル量のパルスの周波数を正確に一定にする手段の提供を行なうことを目的とする。

【構成】

レーザから安定化のために使用出来るデジタル量のパルス周波数を、基準周波数を完全に、しかも安定に一致させるため、ダイオードの順方向の電圧を利用して、正負のパルスの基線を零ボルトにし、さらに、このデジタル量をアナログ量に変換する際、F/V変換回路と正負のパルスの電荷をゆっくり積分する回路を並列にして誤差信号の値を完全に零にしている。

(もっと読む)

1 - 20 / 30

[ Back to top ]