Fターム[5J022AB02]の内容

アナログ←→デジタル変換 (13,545) | D/A、局部D/A変換器の型式 (1,044) | 振幅型D/A (528)

Fターム[5J022AB02]の下位に属するFターム

R−2R型(抵抗、コンデンサ) (38)

重み付け型(抵抗、コンデンサ) (96)

スイッチングツリー型 (136)

電流源型 (126)

CCD、BBD型(電荷転送) (38)

Fターム[5J022AB02]に分類される特許

1 - 20 / 94

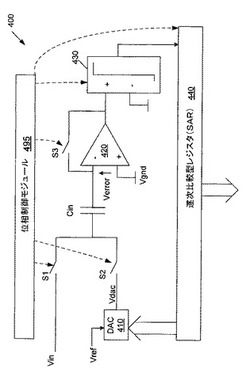

マルチビット遂次比較型ADC

【課題】いくつかの逐次比較サイクルでサイクル当たり1つよりも多いビットに変換するアナログ/デジタル変換器(ADC)を提供する。

【解決手段】システムは、容量性サブDAC回路410及び比較器430を含み、スイッチS2は、1つ又はそれよりも多くの最初のサイクル中に容量性サブDAC回路を隔離し、かつ1つ又はそれよりも多くの最終サイクル中にサブDAC回路を融合し、逐次比較型レジスタ(SAR)440は、デジタル出力信号又はDACデジタル信号を発生させる。また、システムは、DAC回路を含み、アナログ入力信号及びDACアナログ信号のうちの少なくとも一方で入力キャパシタCinを予充電し、プログラマブル利得増幅器420は、誤差信号を増幅し、マルチビットADCは、増幅された誤差信号をマルチビットデジタル信号に変換し、SARは、マルチビットデジタル信号を使用してDACデジタル信号又はデジタル出力信号を発生させる。

(もっと読む)

デジタルアナログ変換器

【課題】従来のデジタルアナログ変換器では変換精度を向上させることができない問題があった。

【解決手段】本発明のデジタルアナログ変換器は、デジタル入力値の上位側mビットの値に対応した第1のアナログ電圧VO1と第2のアナログ電圧VO2とを出力する上位デジタルアナログ変換器DA1と、下位電圧側ノードND1の電圧VR1と、上位電圧側ノードND2の電圧VR2との電圧差を前記デジタル入力値の下位側nビットの値に応じて分割してアナログ出力電圧VOUTを出力する下位デジタルアナログ変換器DA2と、下位電圧側ノードND1に接続される第1のコンデンサC1と、上位電圧側ノードND2に接続される第2のコンデンサC2と、を有し、上位デジタルアナログ変換器DA1は、下位デジタルアナログ変換器DA2に第1、第2のアナログ電圧VO1、VO2を排他的に出力する。

(もっと読む)

パイプラインA/D変換器

【課題】より低ノイズのパイプラインA/D変換器を提供する。

【解決手段】パイプラインA/D変換器のステージ301a〜301iを、アナログ入力信号をサンプルホールドするサンプルホールド回路102、サンプルホールドされたアナログ入力信号をディジタル信号に変換するADSC304、ディジタル変換されたディジタル信号をD/A変換するDAC105、サンプルホールド回路102によってサンプルホールドされたアナログ入力信号からDAC105によってD/A変換された信号を減算し、減算の結果得られた信号を次段のステージに出力する減算器103によって構成する。そして、k個のステージのうちのADSC301a〜301dが、ヒステリシスを有する閾値を使ってアナログ入力信号をディジタル信号に変換するように構成する。

(もっと読む)

スイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システム

【課題】精度および高速性能を損なうことなくアンプシェア動作を実現可能なスイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システムを提供する。

【解決手段】複数のスイッチドキャパシタ回路210,220で共有される演算増幅器AMP11を有し、複数のスイッチドキャパシタ回路は演算増幅器の入力および出力と切り離すように複数のスイッチが制御されて複数の容量で第1のアナログ信号をサンプリングするサンプルモードと、サンプリングした容量を演算増幅器の入力および出力と選択的に接続するように複数のスイッチが制御されて、演算増幅器のサンプルモードでサンプリングした信号と第2のアナログ信号との差分を2N倍に増幅するホールドモードとが相補的に設定され、サンプルモード時に演算増幅器の入力および演算増幅器の内部における電圧が固定されていないノードを共通電位にリセットするスイッチswrを有する。

(もっと読む)

A/D変換器

【課題】追加的な製造工程の必要な容量素子を用いることなく、高精度で高速のA/D変換を行うことができるA/D変換器の提供を図る。

【解決手段】相補的に動作する正側容量主DAC DACPおよび負側容量主DAC DACNを有し、差動信号を受け取って上位ビットの変換を担う容量主DACと、下位ビットの変換を担う抵抗副DACと、前記容量主DACを補正する抵抗補正DACと、複数の差動回路を有し、前記正側容量主DACおよび前記負側容量主DACの出力電位を比較する比較器 CMPと、を有するA/D変換器であって、前記正側容量主DACおよび前記負側容量主DACは、それぞれ最上位の配線層を除く配線層により形成される第1容量素子 CN0', CNO〜CN3を有し、前記比較器は、隣接する前記差動回路CMP1, CMP2の間に設けられ、前記最上位の配線層を含めた配線層により形成される第2容量素子 CC1, CC2を有するように構成する。

(もっと読む)

ディジタルアナログ変換器

【課題】低消費電力で信号の歪みやSNR劣化が少ないディジタルアナログ変換器を提供する。

【解決手段】シフトレジスタSREG、1ビットディジタルΔΣ信号を入力し、一対の信号を出力するスイッチ回路SW1〜SW(N)、出力された一対の信号を入力して一対の信号として出力するインピーダンス素子IMP1〜IMP(N)、出力された一対の信号の一方を入力する反転入力端子OPAa、他方を入力する非反転入力端子OPAb、1ビットディジタルΔΣ信号をディジタルアナログ変換した信号を出力する出力端子102を備える演算増幅器OPA、反転入力端子OPAaと出力端子102とに接続されるインピーダンス素子IMP0−N、非反転入力端子OPAbに一端が接続され、他端に基準電圧が与えられるインピーダンス素子IMP0−Pによりディジタルアナログ変換器を構成する。

(もっと読む)

高分解能のオーバーラッピングビットセグメント化デジタル‐アナログ変換器

【課題】幾つかある識別可能な特徴及び利点の中で、分解能が高く且つ部品数が少なく、更に単調性レンジを動的に移動させ、あるビット値の遷移をまたぐように単調性レンジを移動させるMビットのDACを提供する。

【解決手段】コントローラがMビットの入力を受け、これに応答して、Sビットの高レンジDACに供給するためのSビットの上側レンジ二進データと、Rビットの低レンジDACに供給するためのRビットの下側レンジ二進データとを発生する。このコントローラは、Mビットの入力における遷移点を検出し、これに応答して、Sビットデータの少なくとも1つの最下位ビットに等しい遷移データをSビットデータに加算するとともに、Rビットのデータから遷移データに等しい値を減算する。遷移点及び遷移データを検出して、Rビットデータのフルスケール値でこのような遷移を回避する点において加算する。

(もっと読む)

DA変換装置および試験装置

【課題】簡単な回路構成で、出力電圧の直線性、オフセット、ゲイン誤差を調整するDA変換器。

【解決手段】入力されるデジタル値に応じた出力電圧を出力ラインに出力する容量アレイ型のDA変換器と、出力ラインに接続する負荷容量の大きさを変更する負荷変更部と、を備えるDA変換装置を提供する。負荷変更部は、出力ラインに接続する負荷容量の大きさをデジタル値によらず一定の容量として、当該DA変換装置のゲインを設定する。

(もっと読む)

スイッチ損失を改善するための回路アーキテクチャを有するデジタル/アナログ変換器

【課題】従来の電圧モードDACよりも、線形性が改善され、スイッチエリアの全体が小さく、そして寄生電気抵抗に鈍感なデジタル/アナログ変換器(DAC)を提供する。

【解決手段】デジタル/アナログ変換器(DAC)は、それぞれハイ基準電圧またはロー基準電圧のそれぞれに結合された第1入力をそれぞれ有するオペアンプ対を具備する。前記DACは、複数のスイッチ制御されるセルを具備し、それぞれ、抵抗器および2つのフォース/センススイッチ対を具備する。それぞれのセル内において、4つの全てのスイッチは、抵抗器と結合されている。第1フォーススイッチは、第1オペアンプの出力と結合されるとともに、結合されているセンススイッチは、第1オペアンプの反転入力に結合されている。第2フォーススイッチは、第2オペアンプの出力に結合されるとともに、結合されているセンススイッチは、第2オペアンプの反転入力に結合されている。

(もっと読む)

基準電圧発生回路およびA/D変換器ならびにD/A変換器

【課題】省電力モードへの移行時間、復帰時間が短く、短時間の間欠動作が可能な基準電圧発生回路を有する、A/D変換器、D/A変換器を提供する。

【解決手段】第1基準電圧端子VRTと第2基準電圧端子VRBとの間に接続され、複数の基準電圧を発生する基準電圧発生部12と、第1及び第2基準電圧端子にそれぞれ接続された容量13a、13bと、第1及び第2基準電圧端子の電圧値を検出する基準電圧検出回路16と、基準電圧検出回路により検出された電圧値に応じて、基準電圧発生部へ流す電源電流の大きさを制御する電流制御回路11a、11bと、省電力モード時に基準電圧発生部を高抵抗素子15に切替える切替え手段14a〜14dとを備える。省電力モード時に高抵抗素子に切り替えることで、第1及び第2基準電圧端子間の電流を低減し、しかも、微小電流で容量の電位は保持され、省電力モードからの復帰時間が短くなる。

(もっと読む)

DEM(ダイナミック・エレメント・マッチング)

【課題】精度の高いΔΣ型AD型変換器を実現できるDEMを提供する。

【解決手段】ΔΣ変調器に使用される本願発明のDEMのアルゴリズムは、ΔΣ変調器を構成する量子化器、DA変換器の出力値に関係なく、DA変換器において使用開始するエレメントを所定の個数A個シフトさせることを特徴とする。Aとは1、又は、DA変換器のビット数N(Nは3以上の正の整数)に対して{A<2N/4}となる正の整数である。

(もっと読む)

参照電圧発生回路、およびそれを用いた表示パネル駆動装置

【課題】ラッチアップ耐量試験でのラダー抵抗値の変化およびラダー抵抗の断線を防ぐことで、ラッチアップ耐量試験の耐量値が高い参照電圧発生回路を提供する。

【解決手段】本発明に係る参照電圧発生回路1は、参照電圧を生成するためのラダー抵抗R0〜R7を備えている。上記ラダー抵抗には、外部電源に接続されて上記ラダー抵抗に電圧を印加するV0端子、V5端子、およびV7端子(第1基準電圧端子)と、外部電源に接続されないV6端子(第2基準電圧端子)が接続されている。試験時にV6端子に向かって電流が流れるラダー抵抗R6,R7に並列に、当該ラダー抵抗R6,R7に上記試験時に流れる電流を当該ラダー抵抗R6,R7に代わって自身に流すことができるバイパス素子としてのダイオードD1,D2が接続されている。

(もっと読む)

デジタルアナログコンバータ

デジタル値をアナログ信号に変換する回路(60)が説明される。回路は、値を表し、且つ、それぞれが相対的な重み付けを有する、1つまたは複数のデジタル信号を受信するように構成された論理ブロック(64)を備える。論理ブロックは、1つまたは複数の信号を出力するようにさらに構成されており、各出力信号は、それぞれのデジタル信号で変調された発振器信号を含む。回路(60)は、デジタル値を表すアナログ信号を生成する生成手段(69)をさらに備える。アナログ信号は、論理ブロック(64)から出力された信号の重み付けされた合成を含み、相対的な重み付けは、それぞれのデジタル信号の相対的な重み付けに基づく。論理ブロック(64)は、論理ゲートまたは一連のスイッチなどの、一連の乗算素子(61a−c)を備えてもよく、各乗算素子は、第1の入力としての発振器信号と、第2の入力としてのそれぞれのデジタル信号と、を受信し、且つ、発振器信号をデジタル信号で乗算するように構成される。生成手段(69)は、論理ブロック(64)から出力される信号の相対振幅を変更するように構成される、キャパシタ、抵抗器、およびインダクタなどの、一連の振幅変更器(62a−c)を備えてもよい。生成手段(69)は、振幅変更された信号を合計する手段(66)を備えてもよい。  (もっと読む)

(もっと読む)

逐次比較型A/D変換器、逐次比較型A/D変換器の制御方法、固体撮像装置および撮像装置

【課題】逐次比較型A/D変換器において、オーバーサンプリングを行う場合の処理にかかる時間、ひいてはA/D変換の変換時間を短縮する。

【解決手段】オーバーサンプリングを行う際に、1回目のA/D変換処理では、N回のステップでアナログ信号についてNビットのデジタル値を求める。そして、2回目以降のA/D変換処理では、1回目のA/D変換処理で得たNビットのデジタル値の上位nビットについてはA/D変換処理を行わずにそのまま固定とし、(N−n)ビット以下の下位ビットから、即ちビットの途中からA/D変換を開始する。

(もっと読む)

D/A変換器

【課題】出力応答時間の短縮を図ることができるD/A変換器を提供すること。

【解決手段】第1スイッチ回路12aのスイッチ素子SW0a〜SW15aは、第1端子が共通接続されるとともにその第1端子が高電位電源VRHに接続され、第2スイッチ回路12bのスイッチ素子SW0b〜SW15bは、第1端子が共通接続されるとともにその第1端子が低電位電源VRLに接続される。第1分圧回路13aの抵抗素子Raは、スイッチ素子SW0a〜SW15aの第2端子間に接続され、第2分圧回路13bの抵抗素子Rbは、スイッチ素子SW0b〜SW15bの第2端子間に接続される。制御回路11は、デジタル信号D5〜D0に基づいて、第1スイッチ回路12aのスイッチ素子SW0a〜SW15aのうちの1つをオンするとともに第2スイッチ回路12bのスイッチ素子SW0b〜SW15bのうちの1つをオンする。

(もっと読む)

D/A変換装置

【課題】低分解能のD/A変換装置を用いて、精度の高い高分解能のD/A変換を行うことができるD/A変換装置を提供する。

【解決手段】D/A変換装置Aは、電圧生成装置として第1D/A変換回路1、第2D/A変換回路2、第3D/A変換回路3、及びセレクタ4から構成される。セレクタ4に入力されたデジタル信号Dは、各D/A変換回路に振り分けられる。第1D/A変換回路1、及び第2D/A変換回路2から出力される電圧は、第3D/A変換回路3の上下側基準電圧設定端子に入力される。セレクタ4から第3D/A変換回路3に送られたデジタル信号D3はD/A変換され、出力電圧Voutとして出力される。第3D/A変換回路3は、通常のD/A変換装置より絞られた範囲について、同程度の分解能を有することになるので、通常より精度の高い電圧を出力することができる。

(もっと読む)

D/A変換器及びこれを備える基準電圧回路

【課題】回路規模が小さく、多ビットのディジタル信号を変換可能であり、高精度のD/A変換器を提供する。

【解決手段】上位nビット、下位mビットのディジタル信号をアナログ電圧に変換するD/A変換器であって、同一の抵抗値であり、かつ直列に接続された(2^n)−1個の抵抗を有し、両端に第1基準電圧及び第2基準電圧が印加される分圧手段と、上記分圧手段により分圧された電圧を、上記上位nビットのディジタル信号により選択して上記アナログ電圧として出力する選択手段とを備えるD/A変換器において、上記直列に接続された(2^n)−1個の抵抗の両端に、上記下位mビットのディジタル信号により抵抗値を決定される2つの可変抵抗を接続する。

(もっと読む)

デジタル・アナログ変換回路、固体撮像装置、カメラシステム及びデジタルコードのアナログ変換方法

【課題】D/A変換器の消費電流増加を避けながら、イメージでの横筋状のノイズ低減に有効なD/A変換技術を提案する。

【解決手段】基準電圧をドライバから出力するレギュレータと、そのレギュレータから出力される基準電圧が供給されて、入力したコードに応じたアナログ電圧を出力するアナログ電圧出力部とを備えた構成とする。そして、レギュレータ内のドライバのサイズを、入力したコードに応じて可変させる制御を行う。このようにしたことで、ドライバのゲート電圧が再調整などによって変化することが抑制され、レギュレータに求められる過渡応答特性を下げることが可能となる。

(もっと読む)

DA変換回路および表示用駆動装置

【課題】回路規模を縮小化し、かつコストダウンを行う。

【解決手段】参照電圧V0〜V8を用いて、参照電圧V0〜V8の間の異なる電圧値をそれぞれ有する基準電圧G(63:0)を発生する基準電圧発生回路101と、基準電圧G(63:0)に対して所定の範囲の基準電圧を選択するように区分されて構成されている複数のMOSトランジスタを、該各区分にそれぞれ供給されるデジタルデータに基づいて制御することにより、基準電圧G(63:0)の中から1つの基準電圧を選択する選択回路102と、選択回路102の各区分が選択する基準電圧の範囲に応じて電圧レベルを変換したデジタルデータを、該各区分にそれぞれ供給するレベル変換回路104とを備え、選択回路102の複数のMOSトランジスタは、少なくとも各基準電圧が1番目に入力されるMOSトランジスタが、参照電圧V0〜V8の間の電圧範囲よりも低い耐圧のMOSトランジスタである。

(もっと読む)

逐次比較型A/D変換器

【課題】高速で小面積な自己補正逐次比較型A/D変換器を提供する。

【解決手段】Jビットの第1のデジタル信号に応じた電圧を生成する容量D/A変換器と、第2のデジタル信号に応じた電圧を生成する抵抗D/A変換器と、抵抗D/A変換器の生成する電圧を出力ノードに容量結合する容量素子と、出力ノードに現れる電圧に応じた比較結果信号を生成する比較器と、比較器からの比較結果信号に応じて、第1のデジタル信号を容量D/A変換器に供給すると共に、容量D/A変換器の容量誤差の補正値を示す第3のデジタル信号と、Kビットの第4のデジタル信号を出力する制御回路と、第3のデジタル信号と第4のデジタル信号とに基づいてKビット以上のビット数の第2のデジタル信号を生成して抵抗D/A変換器に供給するデジタル演算回路を含み、(J+K)ビットのデジタルデータを生成する。

(もっと読む)

1 - 20 / 94

[ Back to top ]