Fターム[5J022BA03]の内容

アナログ←→デジタル変換 (13,545) | 目的、効果 (2,366) | 高精度化 (1,223) | オフセット・ドリフトの除去 (306)

Fターム[5J022BA03]に分類される特許

1 - 20 / 306

DACの直線歪補正回路

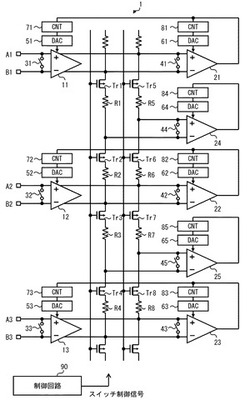

AD変換回路及びその補正方法

【課題】精度の高いAD変換を行うことがが可能なAD変換回路を提供すること。

【解決手段】本発明にかかるAD変換回路は、プリアンプ11,12と、コンパレータ21,22,24と、スイッチ31,41と、トランジスタTr1,Tr5と、スイッチ41をオンした場合におけるコンパレータ21の比較結果に基づいてコンパレータ21のオフセット電圧を補正する第1補正部と、スイッチ31をオンし、スイッチ41及びトランジスタTr1,Tr5をそれぞれオフした場合におけるコンパレータ21の比較結果に基づいてプリアンプ11のオフセット電圧を補正する第2補正部と、を備える。

(もっと読む)

半導体装置

【課題】受信特性に悪影響を及ぼすことなく、受信動作中にバックグランドキャリブレーションを実施可能とする半導体装置を提供する。

【解決手段】受信動作中に、利得や受信チャンネルの切り替えに伴って無効な受信信号が発生するタイミングを検出して、このタイミングに合わせてバックグランドキャリブレーションを行う。このとき、受信信号はもともと無効なのでキャリブレーションに伴うさらなる受信精度の悪化は表面化しない。また、バックグランドキャリブレーションを一定の周期で行う際に発生する不要信号成分も、バックグランドキャリブレーションをランダムなタイミングで行えば発生しない。

(もっと読む)

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

固体撮像装置

【課題】ランプ信号の生成に容量帰還型アンプを用いても、良好なAD変換精度でAD変換を行うことができる固体撮像装置を提供することを課題とする。

【解決手段】2次元状に配列された複数の画素と、列毎に配置され画素からの信号を増幅する増幅回路と、ランプ信号を生成する参照信号発生回路と、ランプ信号及び増幅回路からの出力を用いて、画素からの信号をAD変換するAD変換回路とを備え、増幅回路が有する容量帰還型アンプ及び参照信号発生回路が有する容量帰還型アンプにて同じ構造の帰還容量を用い、かつ帰還容量と増幅器との接続関係を同じにするようにして、増幅回路及び参照信号発生回路のそれぞれの帰還容量のキャパシタンスの電圧依存性を等しくし、AD変換精度を向上させる。

(もっと読む)

A/D変換器

【課題】 キャパシタの誤差の影響を少なくし、A/D変換器の精度を高める。

【解決手段】 アナログ信号更新部100は、キャパシタC1PおよびC1Nが差動増幅器150の入力側に入力キャパシタとして接続され、キャパシタC2PおよびC2Nが差動増幅器150の入出力間に帰還キャパシタとして接続された第1の状態またはキャパシタC2PおよびC2Nが差動増幅器150に入力キャパシタとして接続され、キャパシタC1PおよびC1Nが差動増幅器150に帰還キャパシタとして接続された第2の状態に切り換え可能である。制御部400は、A/D変換サイクル単位で、A/D変換のための係数乗算処理時のアナログ信号更新部100を交互に第1の状態とし、または第2の状態とする切り換えを行う。平均化部502は、所定回数に亙るA/D変換結果が得られる毎に、A/D変換結果を平均化して出力する。

(もっと読む)

デジタル受信機及びそれを用いた光通信システム

【課題】受信信号の品質に応じて、AD変換器の識別レベルを適切に調整することにより、その実効的な分解能を向上させ、もって、高分解能と高速化の要求に応え得るデジタル受信機を提供する。

【解決手段】デジタル受信機は、識別レベル制御信号に応じて識別レベルを設定し、設定された識別レベルに基づいて入力アナログ信号をデジタル信号に変換するAD変換器102と、設定値に基づき識別レベル制御信号を生成し、AD変換器へ出力する識別レベル調整回路104と、設定値に基づきAD変換器の伝達関数に関する情報である伝達関数補正制御信号を生成する信号品質モニタ部108と、伝達関数補正制御信号に基づいて、AD変換器の伝達関数と初期伝達関数とのずれを相殺するようにデジタル信号を信号処理する伝達関数補正回路106とを備える。

(もっと読む)

アナログデジタル変換装置及び信号処理システム

【課題】アナログデジタル変換装置のサイズを縮小し、且つ、インタリーブ間のミスマッチに起因する誤差の補正に必要な処理量を低減する。

【解決手段】本発明の実施形態のアナログデジタル変換装置は、アナログ入力信号をデジタル出力信号に変換する。アナログデジタル変換装置は、アナログデジタル変換ユニット12と、疑似エイリアス信号生成部114と、利得制御部116と、エイリアス信号補正部118と、を備える。アナログデジタル変換ユニット12は、アナログ入力信号を、複数のデジタル信号に変換する。疑似エイリアス信号生成部114は、複数のデジタル信号を合成した合成信号に含まれるエイリアス信号成分を模擬する疑似エイリアス信号を生成する。利得制御部116は、疑似エイリアス信号を用いて、デジタル出力信号の利得を制御する利得制御信号を生成する。エイリアス信号補正部118は、利得制御信号を用いて、エイリアス信号成分を補正する。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

コンパレータシステム、アナログデジタルコンバータおよびコンパレータの閾値補正方法。

【課題】 閾値のずれを補正できるコンパレータシステムを提供する

【解決手段】 コンパレータは、一対のキャパシタを介して入力端子から入力信号を受ける一対の入力ノードと、入力信号の電圧差を示す出力信号を出力する出力ノードとを有する。第1制御回路は、コンパレータの閾値を補正する補正期間に、所定量の負荷が出力ノードに接続された状態で、出力信号の論理が反転するまで一対の入力ノードに設定するコモン電圧を変更し、出力信号の論理が反転するときのコモン電圧の値を求め、求めたコモン電圧を補正期間後の通常動作期間に使用する。第2制御回路は、出力ノードに接続される負荷の量を設定する。第3制御回路は、補正期間に、所定量の負荷が出力ノードに接続されているときのコンパレータの標準の閾値の変動量に対応する電圧差を有する第1電圧および第2電圧を入力端子にそれぞれ供給する。

(もっと読む)

デジタル−アナログ変換器及び半導体集積回路

【課題】デジタル−アナログ変換器の低電圧動作を実現するとともにミラー電流精度を高める。

【解決手段】デジタル−アナログ変換器10は、基準電流を所定のミラー比で複製する第1トランジスタと前記第1トランジスタにカスコード接続される第2トランジスタとを含むミラー回路と、前記第2トランジスタのゲートに接続され、外部からの入力されるデジタル入力信号によってオン・オフ制御されるアナログスイッチとを含む。

(もっと読む)

アナログ‐デジタル変換器及びアナログ信号をデジタル信号に変換する方法

【課題】製造ばらつきによる誤動作が少ないAD変換器を提供することを目的とする。

【解決手段】本発明に係るAD変換器1は、アナログ入力信号を所定の分解能を有するデジタル信号に変換するサイクリック型のアナログデジタル変換器であって、入力される第1アナログ信号の大きさとしきい値とを比較して該比較結果を示すデジタル値を出力する比較部13と、第1アナログ信号を1よりも大きく2よりも小さいβ倍に増幅するとともに比較部の比較結果に応じて所定の演算を実行して第2アナログ信号を出力するMDAC部14とを備えるデジタル近似部10と、MSBを演算するときはアナログ入力信号を、又MSBを演算するとき以外は第2アナログ信号を第1アナログ信号として出力するマルチプレクサ20と、βの値を推定するβ推定部30と、比較部が出力するデジタル値を順次取り込んでデジタル信号として出力するデジタル信号出力部40とを有する。

(もっと読む)

液晶表示装置の駆動装置

【課題】オフセットの影響、回路規模の増大、フリッカ等を抑制し、画質の向上に好適なドライバの提供。

【解決手段】切換制御信号が第1の論理値のとき、第1、第3の電圧が第1、第3の差動段に、第2、第4の電圧が第2、第4の差動段に入力され、第1、第3の差動段の出力が第1、第3の出力段の入力に、第2、第4の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加され、切換制御信号が第2の論理値のとき、第1、第3の電圧が第3、第1の差動段に、第2、第4の電圧が第4、第2の差動段に入力され、第3、第1の差動段の出力が第1、第3の出力段の入力に、第4、第2の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加される。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】ディジタルPGAを含むパイプライン型A/Dコンバータであっても、ディジタルPGAの利得に関係なく、線形性エラーが発生することを抑えて、パイプライン型A/Dコンバータで生成された信号だけを増幅することができるパイプライン型A/Dコンバータを提供する。

【解決手段】ディジタル出力信号DoutのMSB側を処理するA/Dコンバータ102−1´は、制御部105´から出力されたコンパレータ出力制御信号CP1,CP1´によって導通状態が制御される出力値固定用スイッチング素子151,152を有している。ディジタルPGA202によって所定の利得に応じてそれらのスイッチング素子の導通状態を制御することによって、A/Dコンバータ102−1´,102−2´のコンパレータ出力値を固定させておき、通常動作状態のように処理途中の信号に加減算される基準電圧が切り替わらないようにしている。

(もっと読む)

A/D変換器および固体撮像装置

【課題】A/D変換器の比較器のオフセット電圧を簡単な構成で補正するための技術を提供する。

【解決手段】アナログ信号を入力するための入力端子INと、時間的に変化する参照信号を生成する信号源に接続される参照信号供給線と、非反転入力端子、反転入力端子及び出力端子を有し、非反転入力端子に供給された電圧と反転入力端子に供給された電圧との比較結果に応じた出力信号Voutを出力端子から出力する比較器CMPと、比較器の反転入力端子に接続された補正用キャパシタCoffと、入力端子に入力されたアナログ信号に対応するデジタルデータを出力する出力回路330とを備え、入力端子に入力された第2アナログ信号を比較器の非反転入力端子に供給しつつ、参照信号を用いて、比較器の非反転入力端子に供給されている第2アナログ信号又は補正用キャパシタに保持されている合計電圧を変化させる。

(もっと読む)

電圧比較回路,A/D変換器および半導体装置

【課題】比較器に対して最適な同相電圧を与えることによって、動作速度の向上を図る。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

(もっと読む)

デジタル信号生成回路及びデジタルマイク

【課題】入力信号の温度変化をキャンセルするときの増幅利得の歪み及びバラツキを低減する。

【解決手段】デジタル信号生成回路10は、増幅ユニット12と、基準電圧生成回路142と、変調器140と、を備える。増幅ユニット12は、温度Tに線形依存する信号レベルを有するアナログ入力信号Ainを増幅する。基準電圧生成回路142は、温度Tに線形依存させて基準電圧Vrefを生成する。変調器140は、基準電圧Vrefに基づいて、増幅ユニット12が増幅したアナログ入力信号(増幅信号Ain´)をデジタル出力信号Doutに変換する。

(もっと読む)

逐次比較型AD変換器及びその制御方法

【課題】SubDACの出力端子につながる4端子コンパレータのトランジスタのゲート容量が所望の容量比となるように制御して補正し、高精度化を可能とする逐次比較型AD変換器を提供する。

【解決手段】探索範囲を設定するデジタル値DSRを受け、対応する電圧を出力するMainDAC102,103と、探索範囲を設定するための制御信号を受け、対応する電圧を出力するSubDAC101と、MainDAC102,103とSubDAC101からの電圧の比較を行う4端子コンパレータ105,107、MainDAC+(102)と、MainDAC−(103)の出力電圧を比較するコンパレータ106と、切替制御信号に基づきSubDAC101の出力A1,B1,D1,E1又はコモン電圧VCMに切り替えるセレクタ104と、セレクタ104に切替制御信号を与える逐次比較レジスタロジック108を備える。

(もっと読む)

パイプライン型A/D変換回路

【課題】セットリング誤差を線形化でき、高速で消費電力の小さいパイプライン型A/D変換回路を提供する。

【解決手段】パイプライン型A/D変換回路において、各段のA/D変換回路部に、複数の比較器を含み、入力信号をA/D変換するサブA/D変換回路と、サブA/D変換回路からのデジタル信号を、正負の参照電圧を基準値として用いて生成したアナログ制御信号にD/A変換し、アナログ制御信号に基づき、入力信号を、複数のサンプリングキャパシタを用いてサンプリングし、ホールドし、増幅してD/A変換する乗算型D/A変換回路と、後段側の乗算型D/A変換回路でサンプリングをする前に、後段側のサンプリングキャパシタを、サブA/D変換回路に含まれる複数の比較器の出力する比較結果信号に応じて、正負の参照電圧の中間電圧値に予め充電するプリチャージ回路と、を設け、セットリング誤差を線形化する。

(もっと読む)

信号処理装置

【課題】複数のAD変換器を用いて同一のアナログ信号をAD変換する信号処理装置において、個々のAD変換器の特性のばらつきによって生じる同一のアナログ信号のAD変換精度の低下を抑制する。

【解決手段】クロック生成部58はπ[rad]位相の異なる二つのクロックを生成し、対象信号供給部52は受信信号RSまたは0VのいずれかをAD変換部68の二つのAD変換器72、74に供給する。被補正データ生成部86は、AD変換部68が受信信号RSをAD変換した結果に基づき、読出データRDを生成する。オフセットデータ生成部76は、AD変換部68が基準電圧をAD変換した結果に基づき、AD変換器72、74毎の測定誤差を表すオフセットデータAZ1、AZ2を生成する。補正部100は、読出データRDからオフセットデータAZ1、AZ2分を除去する補正処理を実行し、サンプリングデータSDを生成する。

(もっと読む)

1 - 20 / 306

[ Back to top ]