Fターム[5J022CB02]の内容

アナログ←→デジタル変換 (13,545) | 基準電圧・バイアス系 (1,329) | 基準電圧発生回路 (518) | 分圧・レベル調整回路 (222)

Fターム[5J022CB02]に分類される特許

1 - 20 / 222

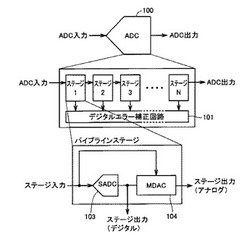

パイプライン型A/Dコンバータ

【課題】コンパレータのオフセットによるディザ量の制限を解消することができるパイプライン型A/Dコンバータを提供する。

【解決手段】アナログ信号をデジタル信号に変換するパイプライン型A/Dコンバータ100は、縦列接続された複数のステージと、複数のステージのそれぞれから出力される副デジタル信号に基づいてデジタル信号を生成するエラー補正回路101とを備える。複数のステージのうち少なくとも1つのステージは、Nビットの副デジタル信号を出力する場合に、伝達関数のステージゲインが2N-2で、且つ折返し数が2N−4、もしくは、2N−2、もしくは、2Nであり、隣接するステージとエラー補正する際にオーバーラップするビット数が2ビットである。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】実施形態のアナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の可変抵抗器で分圧して複数の比較用電圧を生成する。複数の可変抵抗器の各々は、直列に接続されるとともに、外部信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧とを比較し、その比較結果に応じたデジタル信号を出力する。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

アナログ/デジタル変換回路及び半導体装置

【課題】アナログ/デジタル変換器のより詳細な故障診断のための技術を提供する。

【解決手段】アナログ/デジタル変換回路(100〜108)は、入力されたアナログ信号(x、15)を所要の演算式(f(x))にしたがって診断用に演算する演算部(12)と、前記入力されたアナログ信号(x)又は前記演算部によって演算されたアナログ信号(y)のいずれかを選択する第1選択部(11)と、前記第1選択部によって選択されたアナログ信号をデジタル信号に変換する変換部(10、21、22、23)とを有する。

(もっと読む)

半導体装置とその駆動方法

【課題】高精度且つ高分解能のA/D変換を行いつつ、サイズ縮小を可能にしたA/D変換回路を搭載した半導体装置を提供する。

【解決手段】1つのループ状抵抗配線を複数の電源供給スイッチ及び複数の出力回路で共有化し、該抵抗配線及び複数の電源供給スイッチを用いて発生させた三角波(階段状)波形を有する参照電圧を利用する事で、煩雑な回路を用いることなくサイズ縮小を可能にしたA/D変換回路を出力回路に用いて、高精度なデジタル信号を得ることができる。また、A/D変換回路の構成要素が少ないため、並列型のA/D変換回路では、個々のA/D変換回路間でのばらつきを少なくすることができる。

(もっと読む)

比較回路および並列型アナログデジタル変換器

【課題】比較回路の回路面積を小さくする。

【解決手段】第1および第2抵抗列は、所定の電圧範囲を分割してそれぞれ複数の第1参照電圧および複数の第2参照電圧を生成する。第1および第2スイッチ制御回路は、複数の第1参照電圧のうちの事前に決定した1つおよび複数の第2参照電圧のうち事前に決定した1つを選択する。比較回路は、選択された第1および第2参照電圧に応じたトランジスタ電流の合成電流を、入力信号に応じたトランジスタ電流と比較し、論理値を表す論理信号を生成する。第1スイッチ制御回路は、選択する第1参照電圧を順次切り替えることで、論理値が反転する2つの隣接する第1参照電圧を特定し、そのうちの1つを選択することを決定する。その後、第2スイッチ制御回路は、選択する第2参照電圧を順次切り替えることで、論理値が反転する2つの隣接する第2参照電圧を特定し、特定した第2参照電圧のうちの1つを選択することを決定する。

(もっと読む)

抵抗ストリング型D/Aコンバータ

【課題】シングル出力の抵抗ストリング型D/Aコンバータと同等の素子数とセル面積を保ちつつ差動出力電圧を得られる抵抗ストリング型D/Aコンバータを提供する。

【解決手段】第1及び第2の抵抗ストリング部と、データ反転回路と、出力選択スイッチと、第1及び第2の出力端子とを備え、夫々抵抗ストリング部は(n−1)ビットの入力データに応じたアナログ電圧を出力し且つ下位(n−1)ビットの入力データが変動するとき第1の抵抗ストリング部と第2の抵抗ストリング部との電圧変動方向が逆であり、データ反転回路は、被変換データ2(n−1)−1と被変換データ2(n−1)との間を境界として、下位(n−1)ビットの被変換データを反転させて抵抗ストリング部に出力し、出力選択スイッチは、最上位の被変換データの“0”と“1”の切り替わりにより、第1及び第2の出力端子に対して、第1と第2の抵抗ストリング部のアナログ電圧出力を切替る。

(もっと読む)

A/D変換器、A/D変換方法

【課題】簡易な構成で且つ低消費電力(低発熱)なA/D変換器の実現。

【解決手段】入力アナログ信号を抵抗を用いて複数レベル(n種のレベル)に分割し、分割したそれぞれのアナログ信号に基づき各磁気メモリ素子に書込動作が行われるようにする。これによりn種の各レベルごとに符号「0」又は「1」の判定を行うことができ、これら各レベルごとの判定結果に基づいてnビットの量子化データを得ることができる。つまり量子化ビット数=nによる並列型A/D変換を実現できる。或いは、入力アナログ信号を抵抗により複数レベルに分割する代わりに、各磁気メモリ素子としてそれぞれその反転電流値が異なるものを設けることによっても、上記と同様の結果を得ることができる。並列型A/D変換器の実現にあたり従来のようにオペアンプを備える必要はなくなり、結果、簡易な構成で且つ低消費電力・低発熱のA/D変換器を実現できる。

(もっと読む)

抵抗分圧型D/Aコンバータ

【課題】オフしたスイッチに流れるリーク電流が出力信号に与える影響を抑制することが可能な抵抗分圧型D/Aコンバータの提供

【解決手段】デジタル信号の上位Mビットの信号と下位(N−M)ビットの信号によってNビットのデジタル信号をアナログ信号に変換する抵抗分圧型D/Aコンバータであって、一端が第1の基準電位に接続されるスイッチと、ドレインが前記スイッチの他端に接続され、ゲートとバックゲートが互いに接続されるMOSFETと、からなる2M−1個の制御回路を備える抵抗分圧型D/Aコンバータ。

(もっと読む)

アナログデジタル変換器

【課題】フラッシュ型アナログデジタル変換器において、比較器の出力を保持するために配置が必要となるフリップ・フロップにより回路面積が増大するのを抑制する。

【解決手段】基準信号発生回路1と、比較器2と、エンコーダ3とから少なくとも構成されるアナログデジタル変換器において、比較器2を磁気抵抗素子から構成する。磁気抵抗素子のヒステリシス特性を利用することにより比較器2に保持機能を持たせることができ、従来のフラッシュ型アナログデジタル変換器において必要であったフリップ・フロップからなる保持回路を省くことができる。

(もっと読む)

アナログデジタル変換装置及びオフセット電圧補正方法

【課題】配線数を削減する。

【解決手段】アナログデジタル変換装置は、異なる複数の参照電圧の各々と入力信号電圧とを並列的に比較する複数のコンパレータと、入力信号電圧をアナログ入力信号電圧又は複数の参照電圧の何れか一つに対応する電圧に切り替えるスイッチ部と、複数のコンパレータの比較結果をデジタル信号に変換するエンコーダと、複数のコンパレータの中の補正対象のコンパレータにおいて入力信号電圧が参照電圧に対応する電位となるようにスイッチ部を制御し、補正対象のコンパレータで生じるオフセット電圧を補正するための補正データを前記デジタル信号に基づいて生成し、補正対象のコンパレータへ出力するデジタルアシスト回路と、を備える。

(もっと読む)

有機抵抗による基準電圧発生回路、それを備えたA/D変換回路

【課題】アナログオプション回路を備えた半導体集積回路(A/D変換)を構成する抵抗を、簡便かつ大面積を専有されることなく作成する製造方法、及びその製造方法により作成されるAD変換回路を提供する。

【解決手段】高電源の電圧と低電源の電圧との間に直列に接続された複数個の抵抗からなるストリング抵抗を備えた基準電圧発生部と、入力アナログ電圧値と前記抵抗間の接続点の分圧電圧値とを比較する電圧比較部とを含むA/D変換回路において、

前記抵抗が有機材料で形成されていることを特徴とする。

(もっと読む)

アナログ・デジタル変換器

【課題】上位ビットと下位ビットを分けてAD変換を行い、ノイズの影響を受けやすい下位ビットの変換結果の信頼性を、多数決処理を用いて向上させる場合、並列型ADコンバータの基準電圧発生回路としてDAコンバータを搭載する必要があった。

【解決手段】基準電圧発生回路を簡単な抵抗比のみでの構成することにより、下位ビットを変換する並列型ADコンバータの基準電圧発生回路の規模を最小にすることが可能となる。

(もっと読む)

半導体集積回路、閾値設定方法、及び通信装置

【課題】複数の比較器に対して閾値を等間隔に設定可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、第1の状態において、1<M<Nである第Mの比較器の閾値をTHM、第M+1の比較器の閾値をTHM+1とし、(THM+1−THM)を1より小さい正の実数倍した値をTHMに加えることにより第Mの比較器の閾値を更新する第1の動作と、第2の状態において、第Mの比較器の閾値をTHM、第M−1の比較器の閾値をTHM−1とし、(THM−1−THM)を1より小さい正の実数倍した値をTHMに加えることにより第Mの比較器の閾値を更新する第2の動作とを、交互に複数回実行すると共に、第1の比較器の閾値を第1の値近傍に拘束し、第Mの比較器の閾値を第2の値近傍に拘束する制御回路を含む。

(もっと読む)

AD変換回路およびAD変換方法

【課題】ラッチコンパレータを用いた補間型のAD変換回路において、AD変換回路の高ビット化に伴う較正用回路の回路規模の増大を抑制する。

【解決手段】 AD変換の各段階に対応する刻み幅で設定された参照電圧と入力アナログ信号電圧とを比較する複数の比較器のうち2つの出力がそれぞれ入力される少なくとも一つの補間比較器と、各補間比較器の一致判定誤差を補正するための補正値を、複数の段階それぞれについて求める補正値取得部と、AD変換の段階ごとに、各補間比較器にそれぞれの補正値を設定する補正値適用部とを備え、補正値取得部は、AD変換の段階の一つにおける判定レベルに相当する個別テスト電圧の入力に応じて前記補正対象の補間比較器の出力として得られる前記判定レベルに対応する一致判定誤差と、前記共通テスト電圧を比較器に共通に入力した際に得られる一致判定誤差とに基づいて、前記各段階における判定レベルに対応する補正値を算出する補正値算出部を備える。

(もっと読む)

パイプライン・AD変換回路

【課題】入力範囲に応じて精度の異なるパイプライン・AD変換回路の実現。

【解決手段】直列に接続された複数のアナログ/デジタル変換ユニット30,37と、複数のアナログ/デジタル変換ユニットのサブ変換結果から、入力アナログ信号Vinのデジタル変換値Doutを算出するデジタル演算回路38と、を備え、各アナログ/デジタル変換ユニット30は、サブAD変換器32と、アナログ入力信号からサブAD値に応じたアナログ減算信号を減算して残差信号を発生し、残差信号を増幅して出力する増幅DA変換器39と、を備えるパイプライン・AD変換回路であって、初段のサブAD変換器32は、入力範囲-Vref,Vrefを少なくとも4個以上のサブ範囲に分割して、入力アナログ信号がいずれのサブ範囲に入るかを判定し、4個以上のサブ範囲の大きさが異なる。

(もっと読む)

A/D変換器

【課題】相互オフセット較正型A/D変換器において、キャリブレーション終了後には不要となるA/D変換器を有効活用し、A/D変換の精度を高めたA/D変換器を提供する。

【解決手段】2つのA/D変換器を有し、相互にオフセットを較正するA/D変換器では、キャリブレーション終了後においては両者のトランスファーカーブ特性は同じものとなる。そこで、実際のA/D変換の際には、両者のA/D変換器のトランスファーカーブの関係をその分解能の1LSBの半分である0.5LSBずらして両A/D変換器を動作させる。その後、同一時刻にサンプリングした両A/D変換器の出力の和または平均値を出力する。

(もっと読む)

2ステージD/Aコンバータ及びこれを用いた液晶表示装置のソースドライバ

【課題】高解像度の液晶表示装置のソースドライバに用いられる斬新なD/Aコンバータ及び液晶表示装置のソースドライバを提供する。

【解決手段】ソースドライバは2ステージD/Aコンバータを含む。この2ステージD/Aコンバータは、入力されたMビットのデジタルコードによってアナログ電圧を出力する。ソースドライバは、2ビットシリアル電荷再分配D/Aコンバータと、電圧選択手段と、を含む。2ビットシリアル電荷再分配D/Aコンバータは、ハイ参考(参照)電圧を受けるハイ参考電圧入力節点(ノード)及びロー参考電圧を受けるロー参考電圧入力節点を有する。電圧選択手段は、前記Mビットのデジタルコードの少なくとも一部によって前記ハイ参考電圧と前記ロー参考電圧を選択電圧に設定する。

(もっと読む)

2ステージD/Aコンバータ及びこれを用いた液晶表示装置のソースドライバ

【課題】高解像度の液晶表示装置のソースドライバに用いられる斬新なD/Aコンバータ及び液晶表示装置のソースドライバを提供する。

【解決手段】ソースドライバは2ステージD/Aコンバータを含む。この2ステージD/Aコンバータは、1ビットシリアル電荷再分配D/Aコンバータと、電圧選択手段と、ガンマ校正エキスパンディングと決定論理と、を含む。1ビットシリアル電荷再分配D/Aコンバータは、第1容量と、端末容量と、第1スイッチ回路と、第2スイッチ回路と、を含む。第1容量は容量充電節点(ノード)とロー参考電圧入力節点の間に接続される。端末容量は電荷収集節点とロー参考電圧入力節点の間に接続される。第1スイッチ回路は、容量の充電周期において、容量充電節点をロー参考電圧入力節点またはハイ参考電圧入力節点に接続する。第2スイッチ回路は、電荷の再分配周期において、容量充電節点を電荷収集節点に接続する。

(もっと読む)

増幅回路及びその増幅回路を含むアナログデジタル変換回路

【課題】オフセットキャンセル動作において発生する消費電力を低減可能なコンパレータを提供する。

【解決手段】差動入力信号を受ける一対のMOSトランジスタのドレインと高電位電源線に接続し、一対のMOSトランジスタのドレインに接続する差動出力ノード間の電位差を増幅し、増幅後の電位を差動出力ノードに保持する増幅部と、差動出力ノード間の電圧増幅時に、差動出力ノードにキャンセル電流を流し、増幅部による増幅動作後に、一対のMOSトランジスタのドレイン電圧に応じて差動出力ノードへのキャンセル電流の流入を遮断するキャンセル回路と、差動入力信号の一方の信号の電位を他方の信号の電位と等しく設定し、差動出力ノード間の電位差を増幅したときに、差動出力ノード間の電位が、キャンセル電流を注入する前に比較し、キャンセル電流の注入後に逆転するように、キャンセル電流を設定するコントローラと、を備える増幅回路。

(もっと読む)

1 - 20 / 222

[ Back to top ]