Fターム[5J022CC02]の内容

アナログ←→デジタル変換 (13,545) | 利得制御系 (243) | 最大・最小検出・レベル制御 (51)

Fターム[5J022CC02]に分類される特許

1 - 20 / 51

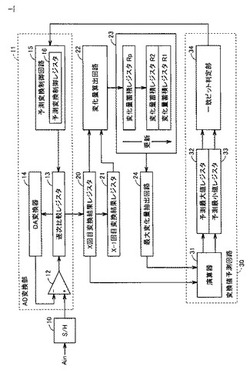

アナログ・デジタル変換装置

【課題】予測変換を行なう逐次変換方式のAD変換装置において、従来よりも予測精度を向上させる。

【解決手段】アナログ・デジタル変換装置1において、変化量算出部22は、変換部11によって入力信号のAD変換が実行される度に、新たに得られたAD変換結果と1つ前に得られたAD変換結果との変化量を算出する。変化量記憶部23は、前回までのAD変換結果に基づいて算出された所定数の変化量を記憶する。最大変化量抽出部24は、変化量記憶部23に記憶されている所定数の変化量のうちで最大変化量を抽出する。変換値予測部30は、抽出された最大変化量に基づいて、AD変換によって求める全ビットのうちの1または複数ビットの予測値を決定する。変換部11は、変換値予測部30によって予測値が決定された1または複数ビットを除く残余のビットの値を逐次比較方式によって決定する。

(もっと読む)

超音波診断装置および超音波画像生成方法

【課題】画像生成処理の高速化と省電力化を図ることができる超音波診断装置を提供する。

【解決手段】アレイトランスデューサから出力される受信信号の振幅に応じて、受信信号処理部による受信信号のA/D変換可能範囲のうち実際にA/D変換が実行されるA/D変換実行範囲を限定し、受信信号のA/D変換を行う。A/D変換実行範囲は、測定深度に関わらずに所定のビット幅を有し、A/D開始ビットおよびA/D終了ビットで特定され、測定深度が増すほど、A/D変換実行範囲のA/D開始ビットおよびA/D終了ビットが漸減される。

(もっと読む)

固体撮像装置

【課題】オーバーレンジのアナログデジタル変換において、隣接する2つのサブレンジの境界付近における入出力特性の不連続性を低減することができる固体撮像装置を提供する。

【解決手段】カウンタ782は、第2の変換ステージにおいて、クロックに応じてインクリメントされる。ランプ電圧発生部618は、カウンタ782の値に応じた大きさのランプ電圧を出力する。第2の変換ステージにおいて、カウンタ782の初期値がSであり、カウンタの取りうる値はサブレンジに対応してM個で、隣接するそれぞれのオーバーラップ領域に対応してL個である。シーケンサは、第1の電圧と第2の電圧の差が、カウンタ782の値が(S+L)のときのランプ電圧の値である第1ランプ電圧とカウンタ782の値が(S+L+M−1)のときのランプ電圧の値である第2ランプ電圧との差に等しくなるように調整部613に調整させる。

(もっと読む)

A/Dコンバータ、マイコン、故障判定方法

【課題】AD変換中にアナログ入力の値が変動したことをより高精度に判別可能なA/Dコンバータを提供すること。

【解決手段】アナログ入力の下限値と上限値が登録された判定テーブル28と、アナログ入力と、アナログ値に変換された基準値を比較する比較手段24と、前記比較手段がアナログ入力の方が基準値より大きいと判定するとより大きい基準値に変更し、アナログ入力の方が基準値より小さいと判定するとより小さい基準値に変更する基準値変更手段26と、比較結果及び基準値を取得し、アナログ入力の方が基準値より小さい場合は前記判定テーブルの前記上限値に基準値を設定し、アナログ入力の方が基準値より大きい場合は前記判定テーブルの前記下限値に基準値を設定するテーブル更新手段27と、アナログ入力が前記下限値と前記上限値の範囲に入るか否かを判定する異常判定手段29と、有する。

(もっと読む)

逐次比較型AD変換装置及び逐次比較型AD変換方法

【課題】サンプル電圧が予測範囲から上又は下に外れたことを検知する技術を提供する。

【解決手段】DAコンバータ4と、コンパレータ5と、逐次比較レジスタ6を備え、サンプル電圧の取り得る範囲を予測して逐次比較レジスタ6の上位nビットを予め決定した上で、サンプル電圧のAD変換を実行し、出力データを生成するADコンバータ1(逐次比較型AD変換装置)は、Max/Min値生成回路10(生成する生成回路)と、Max/Min値比較回路11(データ比較回路)と、を備える。Max/Min値生成回路10は、予め決定した逐次比較レジスタ6の上位nビットに基づいて、サンプル電圧の予測範囲の最大予測値及び最小予測値を生成する。Max/Min値比較回路11は、最大予測値及び最小予測値と、出力データと、を比較する。

(もっと読む)

A/D変換装置

【課題】積分器の前段に増幅回路を追加することなく、ダイナミックレンジの広範囲化および高精度化が可能なA/D変換装置を提供する。

【解決手段】積分器1の出力電圧Voutを基準電圧Vrefと比較するコンパレータ2と、コンパレータ2の後段に設けられクロックパルスをカウントするカウンタ3と、カウンタ3のカウント値を積分器1の出力電圧Voutの振幅に応じたディジタル値に変換して出力する変換回路4と、積分器1の出力電圧Voutの振幅に応じたディジタル値を出力する比較型A/D変換器5と、選択回路6と、タイミング制御回路7とを備える。タイミング制御回路7は、積分器1を積分動作させる積分期間の終了直前の所定時までにコンパレータ2の出力Vcpが反転しない場合には、比較型A/D変換器5にA/D変換を行わせてディジタル値を選択回路6から出力させ、反転した場合には、変換回路4から出力されるディジタル値を選択回路6から出力させる。

(もっと読む)

二重積分型A/D変換器

【課題】両極性の入力電圧を変換可能であり、且つ、カウンタのカウント値が異常値であるか否かを判定することが可能な二重積分型A/D変換器を提供する。

【解決手段】第1積分期間の終了時におけるコンパレータ3の出力に基づいて積分器1の出力電圧Voutの基準電圧VAGNDに対する大/小に基づく極性を“H”/“L”として判定して出力するとともに極性判定結果に応じて入力切替部2を制御する制御回路(制御部)5と、積分器1の出力電圧Voutを基準電圧VAGNDよりも高い第1の比較基準電圧VH、基準電圧VAGNDよりも低い第2の比較基準電圧VLそれぞれと比較して各比較結果ごとに大/小に応じて“H”/“L”の出力を発生する比較手段7とを備える。ディジタル回路8は、カウンタ4のカウント値が最大値であり、且つ、制御回路5での極性判定結果と比較手段7による両方の比較結果とが異なるときに、カウント値を異常値と判定する異常判定手段を有する。

(もっと読む)

アナログデジタル変換装置及びアナログデジタル変換方法

【課題】変換対象であるアナログ信号の信号特性に応じた分解能でデジタル信号に変換でき、消費電力が削減できるアナログデジタル変換装置及びアナログデジタル変換方法を提供する。

【解決手段】入力信号G1の所定の特性を検出する信号特性検出部6と、信号特性検出部6により検出された信号特性に基づき分解能を設定し、該分解能のアナログデジタル変換に必要な動作のみを指示する制御信号G10を生成し、出力する制御信号生成部7と、制御信号G10に基づき動作を制限して、設定された分解能で入力信号をデジタル信号に変換するアナログデジタル変換ユニット4と、を備える。

(もっと読む)

音声処理装置

【課題】大きなヘッドルームを設定したアナログ信号をデジタル処理回路で増幅したときのS/N特性を向上する。

【解決手段】音声処理系統11〜1nは、アナログ増幅回路21〜2n、AD変換回路31〜3n、デジタル処理回路41〜4nを有する。第1の音声処理系統11に入力されたアナログ信号は、分配スイッチ62を介して第1と第2の音声処理系統のアナログ増幅回路21、22に分配される。分配されたアナログ信号は、26dBに設定されたヘッドルームに基づいてアナログ増幅回路21、22で増幅され、AD変換回路31、32で−26dBFSのデジタル信号に変換される。これらのデジタル信号は、切換スイッチ71、72を介して、デジタル信号の加算・処理回路40に入力される。これらのデジタル信号は、デジタル信号の加算・処理回路40において加算、増幅され、一般的基準の出力レベルである−20dBFSのデジタル信号として出力される。

(もっと読む)

AD変換器及びAD変換回路の電圧制御方法

【課題】AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供する。

【解決手段】アナログ信号からデジタル信号に変換するAD変換回路へ、アナログ信号の入力の振幅を可変させて出力するAGC回路と、AGC回路が出力するアナログ信号の出力範囲と、既定の電圧の範囲と比較して、該比較の結果に基づいてAGC回路が出力するアナログ信号の出力範囲を制御する第1検波部と、を備える、AD変換器が提供される。これにより、AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供することができる。

(もっと読む)

パイプライン・AD変換回路

【課題】入力範囲に応じて精度の異なるパイプライン・AD変換回路の実現。

【解決手段】直列に接続された複数のアナログ/デジタル変換ユニット30,37と、複数のアナログ/デジタル変換ユニットのサブ変換結果から、入力アナログ信号Vinのデジタル変換値Doutを算出するデジタル演算回路38と、を備え、各アナログ/デジタル変換ユニット30は、サブAD変換器32と、アナログ入力信号からサブAD値に応じたアナログ減算信号を減算して残差信号を発生し、残差信号を増幅して出力する増幅DA変換器39と、を備えるパイプライン・AD変換回路であって、初段のサブAD変換器32は、入力範囲-Vref,Vrefを少なくとも4個以上のサブ範囲に分割して、入力アナログ信号がいずれのサブ範囲に入るかを判定し、4個以上のサブ範囲の大きさが異なる。

(もっと読む)

入力モジュール

【課題】演算処理部の出力に異常レベルのノイズが重畳する状態において、その異常の要因がアナログ入力信号に重畳されたノイズによるものなのか、入力モジュールの故障によるものかを判定可能とした入力モジュールを実現する。

【解決手段】アナログ入力信号に重畳するノイズをローパスフィルタで軽減してADコンバータによりデジタル変換し、ファームウェアフィルタを備える演算処理部で処理して上位装置に出力する入力モジュールにおいて、

前記アナログ入力信号に重畳するノイズが設定された所定の閾値の範囲か否かを検出してこのノイズのレベル異常を判定する第1監視部を具備する入力ノイズ検出部と、

前記演算処理部の出力より前記アナログ信号のノイズレベルを推定演算し、これが前記所定の閾値の範囲か否かを検出してレベル異常を判定する第2監視部と、

前記第1監視部の判定出力と前記第2監視部の判定出力とを入力し、異常原因を特定して上記上位装置に出力する診断部と、

を備える。

(もっと読む)

A/D変換器用テスト回路、A/D変換器のテスト方法

【課題】 少ないピン数で、D/A変換器及び大容量メモリを有しない小型集積回路上に実装されたA/D変換器のテストが可能なテスト回路及び方法を提供する。

【解決手段】 アナログ信号をA/D変換器20で変換した一連のディジタルデータが入力される最大値検出回路2、最小値検出回路3、及び分散値計算回路5を備える。各回路2,3,5は、それぞれA/D変換器20に対するアナログ信号の入力開始前に所定の初期値にリセットされる。回路2(3)は、一連のディジタルデータが入力される間にわたって、現時点での保持データよりも大きい(小さい)データが入力されると当該保持データを入力データに更新し、回路5は分散計算を行って保持データを更新する。一連のディジタルデータの入力完了後、回路2,3,5の各保持データを、夫々ディジタルデータの最大値、最小値、及び分散値として外部のテスターに出力可能に構成されている。

(もっと読む)

AD変換回路

【課題】2重積分AD変換回路において、積分器の非反転入力端子に近い電圧をAD変換する場合、変換結果が不安定である。

【解決手段】アナログ入力電圧に所定の演算を行ってAD変換を行いその結果に更に所定の演算を行うことにより、積分器の非反転入力端子に近い電圧を直接変換することを回避する。比較電圧を変化させることで、不安定な領域での変換を回避するようにしてもよい。

(もっと読む)

A/D変換器、A/D変換方法

【課題】A/D変換に際して、信号レベルにオフセットを与えた場合において、実用上充分な程度にまで正確に元の信号を復元する。

【解決手段】アナログの入力信号について、サンプルホールド周期1/fsによるサンプルホールドを行う。このサンプルホールド信号が閾値を超えて遅延時間1/2fsを経過したタイミングで、サンプルホールド信号に対するオフセットの付与を開始する。この信号をサンプリング周波数2fsのデジタル信号に変換する。オフセット後の復元処理では、オフセット付与の開始時に得られる、オフセット付与前のレベルと、次のオフセットが付与されたレベルとから実際のオフセットレベルを求めて信号レベルを復元する。

(もっと読む)

測定装置および測定方法

【課題】DAコンバータの誤差を短時間で測定する。

【解決手段】DAコンバータの特性を測定する測定装置であって、デジタルの入力値をインクリメントまたはデクリメントしてDAコンバータに供給する供給部と、供給されたそれぞれの入力値に対応してDAコンバータから出力されたアナログ信号の出力値をサンプリングするサンプリング部と、所定ステップ量の差がある2つの入力値毎に、対応する2つの出力値の間の変化量を算出する変化量算出部と、変化量算出部が算出した変化量を順次に記憶する変化量メモリと、変化量メモリに記憶された変化量のそれぞれについて、理想変化量に対する誤差を順次に算出し、順次に算出した誤差のうちの最大値を出力する演算処理部と、を備える測定装置を提供する。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

オフセット校正回路、オフセット校正方法およびシステム

【課題】 信号に含まれるACオフセットを除去する。

【解決手段】 加算器は、入力信号とオフセットキャンセル信号とを演算し、演算結果を出力信号として出力する。第1極値検出部は、出力信号の信号値のうち正または負の一方を示す複数の極値を求める。第1極大極小検出部は、出力信号に含まれるACオフセットにより変化する一方の極値の第1極大値および第1極小値を求める。第1振幅検出部は、第1極大値および第1極小値の差からACオフセットの第1振幅を求める。第1周期検出部は、第1極大値および第1極小値の一方が現れてから、第1極大値および第1極小値の他方が現れるまでの期間をACオフセットの第1半周期として求める。周期信号生成部は、第1振幅および第1半周期を有する周期信号を生成する。位相調整部は、第1振幅が小さくなる方向に周期信号の位相を調整し、オフセットキャンセル信号として出力する。

(もっと読む)

データ記録装置

【課題】波形の細かな変動を確実に記録しながら記録データ量を抑えることができ、記録後における波形の異常変動部分の検出が容易に行えるデータ記録装置を提供すること。

【解決手段】アナログ入力信号をA/D変換器でデジタルデータに変換してデータメモリに格納するように構成されたデータ記録装置において、前記A/D変換器とデータメモリの間に、前記A/D変換器から変換出力されるデジタルデータに基づきアナログ入力信号の極値点を検出する極値点検出部を設け、前記データメモリには、検出した各極値点の波形データ値および極値点間におけるサンプリング回数をペアにした極値点データを格納することを特徴とするもの。

(もっと読む)

A/D変換での信号伝送補正システム及びその方法

【課題】送信手段で認識された伝送元の信号を、受信手段にて正しく認識できるように信号のレベル補正を行い、さらには、アナログ伝送された信号に購入される外来ノイズが、A/D変換時の分解能幅の中に収まるように信号のオフセットを実施してノイズの無効化を図る。

【解決手段】受信側ブロック4の信号入力側の直近に、補正ブロック8が配置された点にある。補正ブロック8には、送信側ブロック2で認識された伝送元の信号が受信側ブロック4でも正しく認識されるように信号レベルを補正するレベル補正部9と、ノイズを無効化するためのオフセット部10が設けられている。

(もっと読む)

1 - 20 / 51

[ Back to top ]