Fターム[5J022CC03]の内容

アナログ←→デジタル変換 (13,545) | 利得制御系 (243) | 乗算・除算制御 (96)

Fターム[5J022CC03]に分類される特許

1 - 20 / 96

A/D変換回路、A/D変換方法およびA/D変換プログラム

DACの直線歪補正回路

レベル調整装置、およびレベル調整のためのプログラム

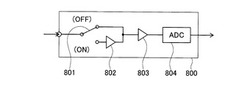

【課題】ユーザに負担をかけることなく、容易にアナログ音響信号の音質劣化を抑制することが可能なレベル調整装置を提供すること。

【解決手段】入力ポートはアナログ入力ブロック800を有し、アナログ入力ブロック800は、迂回スイッチ801、固定ゲインにて信号レベルの減衰を行うパッド802、可変ゲインにて信号レベルを増幅又は減衰して調整するアンプ803を備える。迂回スイッチ801はパッド802とアンプ803により信号レベルが調整されるパッドオン状態とアンプ803のみで信号レベルが調整されるパッドオフ状態を切り替えられる。信号レベルの調整の後に、パッドオン状態で、かつパッドのオン・オフの何れの状態でもゲインの調整が可能な重複範囲ROVの範囲内である入力ポートを抽出し、該当する入力ポートのアナログ入力ブロック800に対して、パッドオフ状態への切り替え調整処理を行う。

(もっと読む)

結合されたディジタル対アナログコンバータおよび信号フィルタ

【課題】多様な応用、および超広帯域の応用において使用されることができるアナログローパスフィルタを提供する。

【解決手段】ディジタル信号201を処理する電子回路は、各々がディジタル信号の遅延されたレプリカを生成するように構成されている複数のディジタル遅延回路203,205,207と、各々がディジタル信号または遅延回路の1つからの遅延されたレプリカをアナログ信号へ変換するように構成されている複数のディジタル対アナログコンバータ211,213,215,217と、各々がディジタル対アナログコンバータからのアナログ信号を利得係数によって調節するように構成されていて、かつ各々が出力をもつ複数のアナログ利得回路221,223,225,227と、アナログ利得回路の出力を加算するように構成されているアナログ加算器231とを含む。

(もっと読む)

デジタル受信機及びそれを用いた光通信システム

【課題】受信信号の品質に応じて、AD変換器の識別レベルを適切に調整することにより、その実効的な分解能を向上させ、もって、高分解能と高速化の要求に応え得るデジタル受信機を提供する。

【解決手段】デジタル受信機は、識別レベル制御信号に応じて識別レベルを設定し、設定された識別レベルに基づいて入力アナログ信号をデジタル信号に変換するAD変換器102と、設定値に基づき識別レベル制御信号を生成し、AD変換器へ出力する識別レベル調整回路104と、設定値に基づきAD変換器の伝達関数に関する情報である伝達関数補正制御信号を生成する信号品質モニタ部108と、伝達関数補正制御信号に基づいて、AD変換器の伝達関数と初期伝達関数とのずれを相殺するようにデジタル信号を信号処理する伝達関数補正回路106とを備える。

(もっと読む)

アナログ‐デジタル変換器及びアナログ信号をデジタル信号に変換する方法

【課題】製造ばらつきによる誤動作が少ないAD変換器を提供することを目的とする。

【解決手段】本発明に係るAD変換器1は、アナログ入力信号を所定の分解能を有するデジタル信号に変換するサイクリック型のアナログデジタル変換器であって、入力される第1アナログ信号の大きさとしきい値とを比較して該比較結果を示すデジタル値を出力する比較部13と、第1アナログ信号を1よりも大きく2よりも小さいβ倍に増幅するとともに比較部の比較結果に応じて所定の演算を実行して第2アナログ信号を出力するMDAC部14とを備えるデジタル近似部10と、MSBを演算するときはアナログ入力信号を、又MSBを演算するとき以外は第2アナログ信号を第1アナログ信号として出力するマルチプレクサ20と、βの値を推定するβ推定部30と、比較部が出力するデジタル値を順次取り込んでデジタル信号として出力するデジタル信号出力部40とを有する。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

データ処理装置、データ処理システム及び電力量計

【課題】増幅回路を用いてAD変換の分解能を拡大するAD変換技術において増幅回路のゲインに対する校正精度を向上させる。

【解決手段】目的ゲイン2n(nは正の整数)に対する前記増幅回路の実際のゲインを実測ゲインとして計測するゲインキャリブレーション処理を行い、アナログ信号を増幅回路で増幅してからAD変換回路で変換してビット拡張された変換データを取得する拡張AD変換処理において、前記増幅回路で増幅してから前記AD変換回路で変換して得られるデータに前記実測ゲインに対する前記目的ゲイン2nの比に応じた操作を施すことによってゲインに起因する誤差を相殺する。前記ゲインキャリブレーション処理では、デジタル的に既知の校正データに応ずる校正信号を目的ゲイン2n倍した信号のAD変換結果に対して、上記校正データをN倍した信号を増幅せずにAD変換して当該変換結果の1/Nの値を用いて、前記実測ゲインを求める。

(もっと読む)

歪み補正装置

【課題】小面積および低消費電力な、A/D変換器の歪み補正装置を提供する。

【解決手段】本発明の一態様としての歪み補正装置は、第一A/D変換器と、第二A/D変換器と、べき乗器と、適応相関制御手段と、歪み除去手段とを備える。前記第一A/D変換器は、第一入力信号をA/D変換して第一変換信号を得る。前記第二A/D変換器は、第二入力信号をA/D変換して第二変換信号を得る。前記第二入力信号は、前記第一入力信号の振幅を低減した信号、または前記第一入力信号は、前記第二入力信号の振幅を増大した信号である。前記べき乗器は、前記第二変換信号をn乗(nは2以上の整数)することにより、べき乗信号を得る。前記適応相関制御手段は、前記べき乗信号と、前記第二変換信号に基づき適応相関制御を行うことにより、前記べき乗信号に含まれるn乗成分である歪み信号を生成する。前記歪み除去手段は、前記第一変換信号から、前記適応相関制御手段で生成された歪み信号を除去する。

(もっと読む)

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】アナログ信号をデジタル信号に変換する第1のAD変換器と、係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器と、制御変数信号に応じて第1のAD変換器の第1の出力信号の非線形性歪みを補償する第1の非線形補償部と、制御変数信号に応じて第2のAD変換器の第2の出力信号の非線形性歪みを補償する第2の非線形補償部と、非線形性歪みを曲率として、第1の非線形補償部による第1の信号および第2の非線形補償部による第2の信号の変化の割合に基づき入力アナログ信号の信号強度に依存する曲率を推定し、曲率部分を打ち消すように制御変数信号を生成して第1の非線形補償部および第2の非線形補償部に出力する非線形検出部とを有する。

(もっと読む)

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】アナログ信号をデジタル信号に変換する第1のAD変換器と、係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器と、制御変数信号に応じて第1のAD変換器の第1の出力信号の非線形性歪みを補償する第1の非線形補償部と、制御変数信号に応じて第2のAD変換器の第2の出力信号の非線形性歪みを補償する第2の非線形補償部と、非線形性歪みを曲率として、第1の非線形補償部による第1の信号および第2の非線形補償部による第2の信号の差分に基づき入力アナログ信号の信号強度に依存する曲率を推定し、曲率部分を打ち消すように制御変数信号を生成して第1の非線形補償部および第2の非線形補償部に出力する非線形検出部とを有する。

(もっと読む)

試験測定装置及び信号デジタル化方法

【課題】ノイズを減らしながら広帯域入力信号をデジタル化する。

【解決手段】スプリッタ10は、特定帯域幅を有する入力信号12を複数の分配信号14及び16へと分配する。高調波ミキサ18及び24は、分配信号14及び16の夫々を、関連する高調波信号20及び26と混合し、関連する混合信号22及び28を生成する。デジタイザ30及び32は、夫々の混合信号22及び28をデジタル化する。高調波ミキサ18及び24に関する高調波信号の少なくとも1つの1次高調波は、デジタイザ30及び32の少なくとも1つの有効サンプル・レートと異なっている。

(もっと読む)

周波数変調装置

【課題】音声信号がアナログ形式で入力される場合であっても、送信周波数をずらすことなく周波数変調を行うことが可能な周波数変調装置を提供する。

【解決手段】周波数変調装置は、アナログ−デジタル変換部(ADC)、DC除去部、中心周波数加算部、振幅−周波数変換部、デジタル−アナログ変換部(DAC)及び送信周波数変換部を具備する。DC除去部は、ADCでデジタル化された信号に含まれる直流成分を除去した減算信号を出力する。中心周波数加算部は、減算信号に、所定の周波数に対応する値を加算した加算信号を出力する。振幅−周波数変換部は、加算信号が示す振幅値情報を周波数値情報に変換する。デジタル−アナログ変換部は、振幅−周波数変換部からの信号をアナログ変換し、送信周波数変換部は、アナログ変換後の信号の周波数を周波数変換し、周波数変調信号として出力する。

(もっと読む)

AD変換装置および信号処理システム

【課題】ダイナミックレンジが歪みで制限されるAD変換の特性を大幅に改善することが可能なAD変換装置および信号処理システムを提供する。

【解決手段】入力アナログ信号をデジタル信号に変換する第1のアナログデジタル(AD)変換器11と、入力アナログ信号を係数αでα倍したアナログ信号をデジタル信号に変換する第2のAD変換器12と、第1のAD変換器の出力信号に係数αを2乗した値α2を掛け合わせる第1の演算器14と、第2のAD変換器の出力信号に係数αを−1乗した値α−1を掛け合わせる第2の演算器15と、第1の演算器の演算結果と第2の演算器の演算結果との差分をとり、入力信号のAD変換結果として出力する第3の演算器16とを有する。

(もっと読む)

ATEのための高速、高分解能及び高精度な電圧源/AWGシステム

【課題】高精度及びリニアリティを改善し、高速の自動テストを行える試験装置を提供する。

【解決手段】デジタルデータ信号の最上位ビットを含むデジタルデータ信号の複数のビットの連続したサブセットで構成される上位ビットアレイ1100を、第1のデジタル/アナログ変換器2100に適用する段階と、デジタルデータ信号の最下位ビットを含みデジタルデータ信号の複数のビットの連続したサブセットで構成される下位ビットアレイ1200の少なくとも一部を操作するために、ルックアップテーブル4000の修正データ4100の少なくとも一部を使用する段階とを備え、修正データの少なくとも第1部分を乗じること、修正データの少なくとも第2部分を加算し、結果を第2デジタル/アナログ変換器に適用することを含む。

(もっと読む)

アナログ−デジタル変換回路、照度センサ、近接センサ、測距センサ、携帯電話、およびデジタルカメラ

【課題】微小なアナログ入力電流を高い精度で検出することが出来るアナログ−デジタル変換回路を提供する。

【解決手段】アナログ−デジタル変換回路1は、アナログ入力電流Iinをデジタル変換してデジタル値ADCOUTを得るADC2(アナログ−デジタル変換部)を備えるアナログ−デジタル変換回路であって、所定期間毎に得られた所定個数のデジタル値ADCOUTを記憶するレジスタユニットと、レジスタユニットが記憶しているデジタル値ADCOUTを全て加算することによって加算値ADD[N]を算出する加算器と、加算値ADD[N]と所定の閾値とを比較するとともに、当該比較の結果に従ってデジタル出力信号DOUTを出力する比較回路5とを備える。

(もっと読む)

アナログ−デジタル変換器

【課題】必要な分解能を達成しながらより低い電力を達成する引き続く要望がある。従って、電力をさらに低減するのは望ましい。従って、必要な分解能を達成しながらより低電力を達成すること。

【解決手段】アナログ入力信号をデジタル出力信号に変換するようにとなっている変換器200が、アナログ入力信号を受信するためにアナログ入力端子205、該アナログ入力端子に接続した冗長符号桁(RSD)段210、デジタル部分220を含む。RSD段は、該アナログ入力端子で該アナログ入力信号を受信するように構成され、第1クロックサイクルの第1半分中該アナログ入力信号からデジタル出力でビットの第1の数を生成するように構成され、第1クロックサイクルの第2半分中該アナログ入力端子でアナログ入力信号の残留フィードバック信号を供給するように構成され、第2クロックサイクルの第1半分中該残留フィードバック信号からデジタル出力でビットの第1の数よりも少ないビットの第2の数を生成するように構成される。

(もっと読む)

複数のPWM信号を用いて出力を制御する方法

【課題】PWM信号をDC信号に変換し、変換後のDC信号に応じて出力を制御する方法において、PWM信号の周波数を下げることなく、変換後のDC信号の分解能を高める。

【解決手段】PWM信号を複数用いて、各PWM信号をそれぞれDC信号に変換し、変換後の各DC信号を合成することにより出力の分解能を高める。例えば、各PWM信号をパルス幅に略比例するDC信号に変換し、変換後のDC信号を加算または乗算する。あるいは、各PWM信号をパルス幅に対して非線形に変化するDC信号に変換し、変換後のDC信号を加算する。

(もっと読む)

アナログ入力二重化装置およびアナログ入力二重化方法

【課題】アナログ入力二重化構成において、現地調整時には稼動側のみについて現地調整を実施すれば足り、片側故障時のモジュール交換の際には現地調整を不要として作業効率を向上させること。

【解決手段】入力するアナログ値の範囲とデジタル値の範囲の対応関係を稼動側と待機側の両方に共通の設定値として設定し、稼動側と待機側のそれぞれでA/D変換誤差を修正するための校正値を入力し、該校正値と前記対応関係から調整用スケール変換データを計算し、稼動側において、外部機器の特性に合わせるための機器調整値を入力し、該機器調整値を稼動側の調整用スケール変換データによってスケール変換して補正値を算出して待機側へ送信し、待機側において、受信した補正値と待機側の調整用スケール変換データを用いて、待機側の機器調整値を計算し、入力した計測値を夫々が保持する機器調整値を用いて修正する。

(もっと読む)

AD変換回路

【課題】2重積分AD変換回路において、積分器の非反転入力端子に近い電圧をAD変換する場合、変換結果が不安定である。

【解決手段】アナログ入力電圧に所定の演算を行ってAD変換を行いその結果に更に所定の演算を行うことにより、積分器の非反転入力端子に近い電圧を直接変換することを回避する。比較電圧を変化させることで、不安定な領域での変換を回避するようにしてもよい。

(もっと読む)

1 - 20 / 96

[ Back to top ]