Fターム[5J022CF01]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 比較器(一致回路) (728)

Fターム[5J022CF01]に分類される特許

1 - 20 / 728

AD変換回路および撮像装置

【課題】エンコードエラーの発生を抑圧することができるAD変換回路および撮像装置を提供する。

【解決手段】VCO100aの出力信号CK0〜CK8のうち出力信号CK7が上位計数部101のカウントクロックとなる。演算部106は、出力信号CK7を基準として定義される出力信号CK0〜CK8の状態(状態0〜状態7)を検出するため、各出力信号の論理状態の変化位置を検出し、検出された変化位置に基づいて下位計数信号を生成する。演算部106がこの変化位置を検出する際の手順では、立下りエッジが略同時になる出力信号CK0と出力信号CK7の論理状態の比較は行われない。このため、エンコードエラーの発生を抑圧することができる。

(もっと読む)

AD変換回路及びその補正方法

【課題】精度の高いAD変換を行うことがが可能なAD変換回路を提供すること。

【解決手段】本発明にかかるAD変換回路は、プリアンプ11,12と、コンパレータ21,22,24と、スイッチ31,41と、トランジスタTr1,Tr5と、スイッチ41をオンした場合におけるコンパレータ21の比較結果に基づいてコンパレータ21のオフセット電圧を補正する第1補正部と、スイッチ31をオンし、スイッチ41及びトランジスタTr1,Tr5をそれぞれオフした場合におけるコンパレータ21の比較結果に基づいてプリアンプ11のオフセット電圧を補正する第2補正部と、を備える。

(もっと読む)

AD変換回路及びAD変換方法

【課題】ビット判定時に比較部での比較時間が長くなることによりAD変換時間が長くなることを抑制する。

【解決手段】アナログ電圧生成部11が、受信したアナログ信号を外部クロック信号Φsに同期してサンプリングし、制御信号に基づいて第1のアナログ電圧及び第2のアナログ電圧を生成し、比較部12がクロック信号Φcに同期して第1のアナログ電圧と第2のアナログ電圧の大きさを比較し、制御部13が第1のアナログ電圧と第2のアナログ電圧の電圧差を縮小させていき、比較部12の比較結果に基づいて、外部クロック信号Φsに同期してサンプリングされたアナログ信号に応じたデジタル信号を生成し、中心電圧調整部15が、クロック信号Φcの信号遷移の回数が閾値以上になると、比較部12の入力トランジスタに流れる電流が増加するように、第1のアナログ電圧と第2のアナログ電圧の中心電圧を調整する。

(もっと読む)

逐次近似アナログ・デジタル変換

【課題】アナログ入力信号をデジタル出力信号に変換するためのシステム及び方法を提供する。

【解決手段】システムは、DAC電流を供給するための電流モード(CM)デジタル・アナログ変換器(DAC)回路210を含む。比較器回路250は、DAC電流及びアナログ入力信号に基づいて決定されたエラー信号に応答して比較器信号を発生する。逐次近似レジスタ回路270は、比較器信号に応答して、DACコード信号274又はデジタル出力信号272のうちの少なくとも1つを発生する。DACコード信号をCM DAC回路によって用いて、DAC電流を制御する。

(もっと読む)

二次電池の状態検知装置、二次電池の状態検知装置のための故障診断方法

【課題】故障診断用の電圧が変動した場合でも、精度良くADコンバータの故障診断を実施する二次電池の状態検知装置を提供する。

【解決手段】二次電池の状態検知のために検出されたアナログ値をデジタル値に変換する複数のADコンバータ(18−20)を備えた二次電池の状態検知装置において、前記複数のADコンバータの故障診断時に、故障診断用電圧を同時に前記複数のADコンバータへ入力するための故障診断用電源(15)と、前記複数のADコンバータの出力値を相互に比較して故障の判定を行う演算部(16)と、を備えた。

(もっと読む)

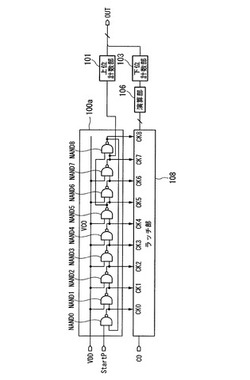

AD変換回路および撮像装置

【課題】カウントクロックの周波数によらず、AD変換により得られるデジタルデータの分解能を向上させることができるAD変換回路および撮像装置を提供する。

【解決手段】ラッチ部108は、比較部109による比較処理の間、クロック生成部18からのクロック信号を通過させ、比較処理の終了に係るタイミングでクロック信号をラッチする。列カウント部103は、クロック生成部18からのクロック信号をカウントすることに加えて、ラッチ部108にラッチされたクロック信号の論理状態に基づいて生成された計数信号をカウントする。

(もっと読む)

固体撮像装置

【課題】従来よりも高精度かつ高速の変換が可能なカラムADCを内蔵した固体撮像装置を提供する。

【解決手段】固体撮像装置200において、各変換部12は、対応の垂直読出線9を介して出力された各画素の信号を第1〜第N(Nは3以上の整数)の変換ステージを順に実行することによってデジタル値に変換する。第1〜第N−1の変換ステージでは、各変換部12は、画素の信号を保持する保持ノードND1の電圧を所定の電圧ステップずつ変化させながら参照電圧と比較することによって、デジタル値の最上位ビットを含む上位の複数ビットの値を決定する。第Nの変換ステージでは、各変換部12は、第N−1の変換ステージにおける電圧ステップの範囲またはそれを超える範囲で、保持ノードND1の電圧を連続的に変化させながら参照電圧と比較することによって、残りの最下位ビットまでの値を決定する。

(もっと読む)

固体撮像装置

【課題】消費電流を低減することができる固体撮像装置を提供する。

【解決手段】画素信号のレベルに応じた論理状態の信号を出力する複数の遅延ユニットのいずれかの出力信号の論理状態をラッチするラッチ回路L_7において、複数の遅延ユニットのいずれかの出力信号が入力端子Dに入力される。NAND回路NAND1およびINV回路INV2は、画素信号のレベルに応じた制御信号が出力される制御信号出力タイミングまでは停止しており、制御信号出力タイミングの後に動作する。スイッチ回路SW1,SW2は、制御信号出力タイミングまでは複数の遅延ユニットのいずれかの出力信号を、信号線LN2を介して出力端子Mから出力し、制御信号出力タイミングから所定時間が経過した後のラッチタイミングで複数の遅延ユニットのいずれかの出力信号の論理状態をNAND回路NAND1およびINV回路INV2がラッチするように接続の切替を行う。

(もっと読む)

マルチビット遂次比較型ADC

【課題】いくつかの逐次比較サイクルでサイクル当たり1つよりも多いビットに変換するアナログ/デジタル変換器(ADC)を提供する。

【解決手段】システムは、容量性サブDAC回路410及び比較器430を含み、スイッチS2は、1つ又はそれよりも多くの最初のサイクル中に容量性サブDAC回路を隔離し、かつ1つ又はそれよりも多くの最終サイクル中にサブDAC回路を融合し、逐次比較型レジスタ(SAR)440は、デジタル出力信号又はDACデジタル信号を発生させる。また、システムは、DAC回路を含み、アナログ入力信号及びDACアナログ信号のうちの少なくとも一方で入力キャパシタCinを予充電し、プログラマブル利得増幅器420は、誤差信号を増幅し、マルチビットADCは、増幅された誤差信号をマルチビットデジタル信号に変換し、SARは、マルチビットデジタル信号を使用してDACデジタル信号又はデジタル出力信号を発生させる。

(もっと読む)

半導体装置

【課題】受信特性に悪影響を及ぼすことなく、受信動作中にバックグランドキャリブレーションを実施可能とする半導体装置を提供する。

【解決手段】受信動作中に、利得や受信チャンネルの切り替えに伴って無効な受信信号が発生するタイミングを検出して、このタイミングに合わせてバックグランドキャリブレーションを行う。このとき、受信信号はもともと無効なのでキャリブレーションに伴うさらなる受信精度の悪化は表面化しない。また、バックグランドキャリブレーションを一定の周期で行う際に発生する不要信号成分も、バックグランドキャリブレーションをランダムなタイミングで行えば発生しない。

(もっと読む)

半導体装置、固体撮像装置、およびカメラシステム

【課題】隣接ビアを伝送される信号間の干渉を低減でき、ひいてはビア数の増大を抑止でき、センサを搭載したチップの面積、実装工程を低減でき、結果的にコスト削減を図ることができる半導体装置、固体撮像装置、およびカメラシステムを提供する。

【解決手段】第1チップ110と、第2チップ120と、を有し、第1チップ110と第2チップ120は貼り合わされた積層構造を有し、第1チップと第2チップ間の配線は、ビア114を通して接続され、第1チップ110は、各センサ111で発生したアナログ信号を時間離散化した信号が、対応するビアを介して第2チップに伝送され、第2チップ120は、ビアを介した第1チップから伝送された信号を第1チップでサンプリングしたタイミングとは異なるタイミングでサンプリングする機能と、量子化してデジタル信号を得る機能と、を含む。

(もっと読む)

比較器、AD変換器、固体撮像装置、およびカメラシステム

【課題】一層のノイズ低減を図ることができることはもとより、低周波ノイズの低減を図ることができる比較器、AD変換器、固体撮像装置、およびカメラシステムを提供する。

【解決手段】比較器500Aは、第1の入力サンプリング容量C511と、第2の入力サンプリング容量C512と、出力ノードdと、一方の入力端子に、第1の入力サンプリング容量を介して、信号レベルが傾きをもって変化するスロープ信号を受け、他方の入力端子に、第2の入力サンプリング容量を介して入力信号を受けて、スロープ信号と入力信号との比較動作を行う差動比較部としてのトランスコンダクタンス(Gm)アンプ511と、Gmアンプの出力部cと出力ノードdとの間に配置され、Gmアンプの出力部の電圧を一定に保持するアイソレータ530とを有する。

(もっと読む)

半導体集積回路、閾値設定方法、及び通信装置

【課題】複数の比較器に対して両端の閾値を適切な値に設定すると共にその間の閾値を等間隔に設定可能である半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力電圧と閾値とをそれぞれ比較する第1乃至第Nの比較器と、第1乃至第Nの比較器のうちの第1及び第Nの比較器について閾値設定動作を実行するとともに、第1乃至第Nの比較器のうちの第2乃至第N−1の比較器について閾値更新動作を複数回実行する制御回路とを含み、閾値設定動作により、第1及び第Nの比較器の閾値は、第1及び第Nの比較器による入力電圧と閾値との比較結果に応じて、それぞれ入力電圧の下限値近傍及び上限値近傍に設定され、閾値更新動作により、1<M<Nである第Mの比較器の更新後の閾値は、第1乃至第Nの比較器の並び順においてM番目の位置の近傍にある複数の比較器の閾値の重み付け平均値に等しく設定される。

(もっと読む)

アナログ・デジタル変換装置

【課題】予測変換を行なう逐次変換方式のAD変換装置において、従来よりも予測精度を向上させる。

【解決手段】アナログ・デジタル変換装置1において、変化量算出部22は、変換部11によって入力信号のAD変換が実行される度に、新たに得られたAD変換結果と1つ前に得られたAD変換結果との変化量を算出する。変化量記憶部23は、前回までのAD変換結果に基づいて算出された所定数の変化量を記憶する。最大変化量抽出部24は、変化量記憶部23に記憶されている所定数の変化量のうちで最大変化量を抽出する。変換値予測部30は、抽出された最大変化量に基づいて、AD変換によって求める全ビットのうちの1または複数ビットの予測値を決定する。変換部11は、変換値予測部30によって予測値が決定された1または複数ビットを除く残余のビットの値を逐次比較方式によって決定する。

(もっと読む)

固体撮像装置

【課題】ランプ信号の生成に容量帰還型アンプを用いても、良好なAD変換精度でAD変換を行うことができる固体撮像装置を提供することを課題とする。

【解決手段】2次元状に配列された複数の画素と、列毎に配置され画素からの信号を増幅する増幅回路と、ランプ信号を生成する参照信号発生回路と、ランプ信号及び増幅回路からの出力を用いて、画素からの信号をAD変換するAD変換回路とを備え、増幅回路が有する容量帰還型アンプ及び参照信号発生回路が有する容量帰還型アンプにて同じ構造の帰還容量を用い、かつ帰還容量と増幅器との接続関係を同じにするようにして、増幅回路及び参照信号発生回路のそれぞれの帰還容量のキャパシタンスの電圧依存性を等しくし、AD変換精度を向上させる。

(もっと読む)

AD変換器、光電変換装置、および撮像システム

【課題】 並列型AD変換器におけるカウンター回路の動作を精度良く制御する。

【解決手段】 第1クロック信号を計数してカウント信号を出力するカウンター回路と、第1クロック信号に基づいて、第2クロック信号を生成する第2クロック信号生成部と、カウント開始信号を前記第2クロック信号に同期して出力するクロック同期化部と、を有し、カウンター回路は、第2クロックに同期したカウント開始信号に応じて計数を行う。

(もっと読む)

光電変換システム

【課題】被写体の撮像と並行して、A/D変換器に供給されるカウント信号の検査を行うことができる光電変換システムを提供することを課題とする。

【解決手段】マトリクス状に配置された複数の画素と、ランプ信号を生成する参照信号生成部と、列毎に配置され、画素からの信号をA/D変換するA/D変換器と、ランプ信号の出力に合わせてカウント動作を行い、カウント信号をカウント信号線を介してA/D変換器に供給するカウンタと、A/D変換器とは独立して設けられ、カウント信号の期待値とカウント信号線を介して供給されるカウンタからのカウント信号とを照合することによりカウンタの検査を行うカウンタ検査回路を備え、被写体の撮像と並行に、カウント信号の検査を行えるようにする。

(もっと読む)

ランプ信号出力回路、アナログデジタル変換回路、撮像装置、ランプ信号出力回路の駆動方法

【課題】 ADCにおいて、ランプ信号の電位の時間に依存した変化の開始に先立って、ランプ信号のランプ開始電位をシフトする形態が知られている。このランプ信号の電位をシフトする方法として、従来は積分アンプの入出力端子間に設けられた積分容量に電流を印加して充放電させていた。従って、ランプ信号のランプ開始電位をシフトするのに積分容量を充放電する期間を要していた。

【解決手段】 ランプ信号のランプ開始電位をシフトさせる電圧供給部を有することを特徴とするランプ信号出力回路である。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】コンパレータのオフセットによるディザ量の制限を解消することができるパイプライン型A/Dコンバータを提供する。

【解決手段】アナログ信号をデジタル信号に変換するパイプライン型A/Dコンバータ100は、縦列接続された複数のステージと、複数のステージのそれぞれから出力される副デジタル信号に基づいてデジタル信号を生成するエラー補正回路101とを備える。複数のステージのうち少なくとも1つのステージは、Nビットの副デジタル信号を出力する場合に、伝達関数のステージゲインが2N-2で、且つ折返し数が2N−4、もしくは、2N−2、もしくは、2Nであり、隣接するステージとエラー補正する際にオーバーラップするビット数が2ビットである。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】アナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の抵抗器で分圧して複数の比較用電圧を生成する。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧との比較結果に応じたデジタル信号を出力する。各比較器は、2つの入力の電位差を検出する差動対回路を含む。差動対回路は、第1回路部50と第2回路部60とを有する。第1回路部は、第1入力トランジスタ51と、第1入力トランジスタと直列に接続される抵抗器Rrefとを含む。第2回路部は、第1入力トランジスタと差動対を形成する第2入力トランジスタ61と、第2入力トランジスタと直列に接続される可変抵抗器Rvとを含む。可変抵抗器は、直列に接続されるとともに、制御信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。

(もっと読む)

1 - 20 / 728

[ Back to top ]